Capitolo VI Conversione A/D e D/A. elettronici/CAP6.pdf · Capitolo VI Conversione A/D e D/A 212 In...

Transcript of Capitolo VI Conversione A/D e D/A. elettronici/CAP6.pdf · Capitolo VI Conversione A/D e D/A 212 In...

Capitolo VIConversione A/D e D/A

209

Capitolo VIConversione A/D e D/A.

6.1) Introduzione.

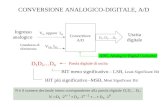

Nei moderni sistemi di misura e controllo le informazioni possono presentarsi in una di duediverse forme. Nella prima la misura di una quantita' fisica (ad esempio una temperatura o unavelocita', etc.) si presenta su una singola linea sotto forma di una grandezza analogica (tensione,corrente, frequenza, etc.), la cui ampiezza rappresenta la misura della grandezza fisica stessa. Nellaseconda invece la misura, e’ presentata (sia in forma seriale su un'unica linea, che in forma parallelasu piu' linee) con un numero finito di bit di informazione, che costituiscono una parola digitale cui e'possibile associare il numero che rappresenta la misura della grandezza di interesse sulla base diun'opportuna unita' di misura.

E' evidente che nel secondo caso la misura risulta discretizzata e la massima risoluzione che sipuo' ottenere e' determinata dal passo di quantizzazione, che coincide con il valore associato al bitmeno significativo della parola.

Ad esempio utilizzando una parola da tre bit in numerazione binaria posizionale e associandoal bit meno significativo ( o in altre parole adottando quale passo di quantizzazione) un volt, lamassima risoluzione sara' appunto di un volt e potranno venir misurate tensioni comprese tra 0 e 7volt in passi incrementali di un volt. Aggiungendo un ulteriore bit prima del piu' significativo, chein qualche modo rappresenti il segno, si potranno evidentemente rappresentare sia grandezzepositive che negative, come illustrato in fig. 6.1

E' immediato osservare che rispetto alla forma analogica (di tipo continuo) larappresentazione digitale (discreta) introduce un errore, detto errore di quantizzazione, la cuiampiezza massima e' pari alla meta' del passo di quantizzazione e la cui distribuzione di probabilita'puo' essere ritenuta uniforme. Questo errore puo' essere ridotto unicamente riducendo il passo diquantizzazione o, in altre parole, aumentando il numero di bit della parola rappresentativa a parita'di ampiezza della grandezza da misurare.

Valore analogico

parola digitale

+ 7

+ 6

+ 5

+ 4

+ 3

+ 2

+ 1

- 1

- 2

- 3

- 4

- 5

- 6

- 7

1111 1110 1101 1100 1011 1010 1001 1000

0000 0001 0010 0011 0100 0101 0110 0111

fig. 6.1

Molti sono i motivi per cui una grandezza viene rappresentata in forma numerica. Uno diquesti e' senza dubbio l'enorme diffusione dei sistemi di eleborazione, che vanno dalla

Capitolo VIConversione A/D e D/A

210

strumentazione basata sui microprocessori ai mainframe di elevatissime prestazioni, disponibilituttavia con una certa facilita' ad una larghissima utenza. Tuttavia la motivazione piu' convincente,che ha portato alla digitalizzazione anche in quei campi che fino a pochi anni or sono sembravanodominio incontrastato della strumentazione analogica, risiede nel fatto che l'elaborazionedell'informazione per via analogica degrada l'accuratezza del dato a ciascun passo di elaborazione eche questa degradazione e' tanto piu' marcata quanto piu' elevata e' la velocita' di elaborazionerichiesta, prevalentemente per l'inevitabile presenza del rumore e per l'imprecisione dei dispositiviadottati.

Con le tecniche digitali invece l'accuratezza del dato e' funzione unicamente del numero di bitutilizzato per rappresentare l'informazione e, qualora si prendano le dovute precauzioni, nondegrada ad ogni passo dell'elaborazione.

E' ovvio che in un sistema, in cui convivano ambedue le forme di rappresentazione, devonoesistere dei dispositivi che permettano il passaggio dall'una all'altra forma in ambedue i versi.Devono cioe' esistere quei dispositivi che vengono chiamati convertitore D/A e A/D.

6.2) Il campionamento.

Come si e’ gia’ accennato i segnali continui, o analogici, possono venir descritti da unafunzione continua del tempo. Al contrario i segnali discreti (o digitali) sono rappresentabili con unasuccessione di numeri, che altro non sono se non la misura del corrispondente segnale analogicosecondo un’opportuna unita’ di misura. E’ evidente pertanto che un segnale discreto non potra’essere definito per qualsiasi valore di t, ma la sua descrizione funzionale sara’ valida solo indeterminati istanti T1, T2, …., Tn nei quali rappresentera’ l’ampiezza del segnale analogico.

Da queste considerazioni discende immediatamente che per passare da una grandezzaanalogica alla sua rappresentazione digitale la prima operazione da eseguire e’ quella di prelevarenegli istanti T1, T2, …., Tn tale grandezza, eseguendo quello che viene chiamato campionamentodel segnale.

Nell’eseguire il campionamento, tuttavia, vanno adottate opportune precauzioni per consentiredi ricostruire a posteriori il segnale. In altre parole la frequenza di campionamento non puo’ esserequalsiasi, ma e’ legata alla massima frequenza contenuta nel segnale da campionare.

Si prenda in considerazione un segnale s(t) (figura 6.2 a) e si supponga che esso abbia unabanda limitata come illustrato in figura 6.2 (b).

s(t)

t

T

s(f)

f-B B

figura 6.2

(a) (b)

c

Capitolo VIConversione A/D e D/A

211

Dalla teoria dei segnali si sa che il segnale campionato, ottenuto prelevando un campione ogniTc secondi, ha uno spettro che si ottiene da quello di s(t) multiplando tale spettro lungo l’asse dellefrequenze a distanza fc = 1/Tc, secondo quanto illustrato in figura 6.3.

s(f)

figura 6.3

0f

f 2 f-f-2 f c c c c

Considerazioni anche intuitive permettono di affermare che per ricostruire il segnale s(t) isingoli spettri non devono sovrapporsi in lacuna loro parte. In altre parole la frequenza dicampionamento fc deve soddisfare la condizione

fc ≥ 2B

In caso contrario si avrebbe il cosiddetto fenomeno dell’aliasing, con distorsioni anchenotevoli del segnale ricostruito.

Per assicurare che le condizioni espresse siano rispettate, all’ingresso dei sistemi diconversione A/D viene di solito introdotto un filtro passa-basso, detto filtro antialiasing, che ha loscopo di limitare superiormente la massima frequenza del segnale analogico che deve’esserecampionato.

Il circuito di campionamento vero e proprio puo’ venir realizzato nella sua forma piu’semplice con un interruttore e un condensatore, come illustrato in figura 6.4.

S

Cv (t) vs o

figura 6.4

Capitolo VIConversione A/D e D/A

212

In questo circuito la tensione ai capi del condensatore, coincidente con la tensione di uscita,segue il segnale vs(t) quando il tasto S e’ chiuso. Quando il tasto S viene aperto la tensione vodiviene costante con un valore pari a quello di vs(t) all’istante di apertura e a tale valore rimane finoalla successiva chiusura.

Un sistema di questo genere, tuttavia, non e’ esente da critiche. In primo luogo la carica delcondensatore C dipende dall’impedenza interna del generatore di segnale vs(t). In secondo luogo ilcondensatore C mantiene l’informazione solo se il circuito a valle ha un’impedenza di ingressoinfinita.

Per ovviare almeno in parte a questi inconvenienti il circuito campionatore puo’ venirrealizzato, ad esempio, secondo lo schema di figura 6.5.

-

+

-

+

Cv (t)

v

tensione di controllodel gate

AA

12

s

o

figura 6.5

L’interruttore in tal caso e’ realizzato con un NMOS e quando un segnale positivo applicato algate lo porta in conduzione il condensatore si carica al valore istantaneo di vs(t). L’inseguitore ditensione A1 ha una duplice funzione. Da un lato non carica il circuito da cui viene prelevato ilsegnale in virtu’ della sua elevatissima impedenza di ingresso. Dall’altro permette al condensatore Cdi caricarsi molto velocemente in quanto la costante di tempo relativa e’ Ro.C, dove con Ro si e’indicata l’impedenza di uscita di A1, che, come si sa, e’ estremamente piccola. Il secondoinseguitore A2 ha il compito di separare il condensatore C dal carico presente in uscita, permettendouna ritenzione dell’informazione per tempi notevolmente elevati.

E’ bene che i condensatori utilizzati siano condensatori a policarbonato, polietilene,polistirolo, mylar o teflon; abbiano cioe’ dielettrico con basse perdite. Tipi diversi di dielettricocauserebbero infatti un rapido decadimento della tensione memorizzata con costanti di tempodell’ordine di alcuni secondi. Inoltre il fenomeno detto di assorbimento dielettrico, per effetto delquale un condensatore “ricorda” una frazione della sua carica precedente quando c’e’ una variazionedella tensione ai suoi capi, introdurrebbe un errore nella grandezza memorizzata.

Quand’anche polarizzazione del dielettrico e assorbimento non avessero importanza, il tempodi tenuta dell’informazione e’ limitato in quanto la corrente di perdita del MOS in condizioni diinterdizione (< 1 nA) e la corrente di polarizzazione di ingresso di A2 (< 1 nA) fluiscono in C.Supponendo pertanto di utilizzare per C un condensatore da 0,5 µF, la tensione ai suoi capipresentera’ una deriva dell’ordine dei 2 mV/sec.

E’ necessario poi tener conto che l’interruttore non si apre istantaneamente. C’e’ sempre untempo, detto tempo di apertura, dell’ordine di 100 nsec e definito come il tempo che intercorre tral’istante in cui viene applicato il comando sul gate e l’istante in cui il MOS effettivamentecommuta. A questo si aggiunge il tempo di acquisizione, cioe’ il tempo necessario affinche ilcondensatore C si carichi dal vecchio al nuovo valore.

Capitolo VIConversione A/D e D/A

213

Se Ro e la resistenza rDS(on) del MOS fossero trascurabili, il tempo di acquisizione sarebbedeterminato dallo slew-rate di A1. Indicando con I la massima corrente che A1 puo’ fornire, lavariazione della tensione vc ai capi del condensatore sarebbe:

CI

dtdvc =

Tutti gli amplificatori operazionali hanno correnti massime d’uscita relativamente limitate(dell’ordine di 25 mA) e quindi il tempo di acquisizione diviene non trascurabile.

Per ovviare a questo inconveniente si puo’ ricorrere a circuiti del tipo di quello illustrato infigura 6.6.

-

+

-

+

Cv (t)

v

porta di controllo

AA

1

2

s

o

figura 6.6

+ V

- V

cc

cc

npn

pnp

In questo circuito la tensione di uscita viene riportata all’ingresso invertente di A1. Cio’ fa si’che durante l’intervallo di campionamento vs(t) = vo. Nell’intervallo di mantenimento vo rimaneinvece al valore raggiunto da vs(t) alla fine dell’intervallo di campionamento, a meno della derivadovuta alla corrente di polarizzazione di A2 e alla corrente di perdita dell’insieme che funge dainterruttore.

Quanto maggiore e’ il valore di C e tanto minore e’ la deriva. Tuttavia un aumento di C faaumentare il tempo di acquisizione. Inoltre la presenza di un polo nel guadagno d’anello puo’generare problemi di stabilita’ del sistema. C pertanto viene scelto come soluzione di compromessotra queste tre esigenze.

E’ opportuno rimarcare che il tempo di tenuta si rende necessario al fine di permettere alconvertitore A/D che si trova a valle di eseguire le sue operazioni avendo in ingresso una tensionecostante.

6.3) I convertitori D/A.

Prima di prendere in esame la struttura dei convertitori A/D e’ opportuno soffermarsi su queicircuiti che effettuano l’operazione inversa, cioe’ sui convertitori D/A. Molto spesso infatti iconvertitori A/D si avvalgono di un convertitore D/A in un loop di reazione.

Un convertitore D/A e' essenzialmente un dispositivo che accetta come ingresso un segnaledigitale D e un riferimento analogico R e genera un'uscita analogica A legata all'ingresso dallarelazione:

Capitolo VIConversione A/D e D/A

214

A R D= .

Il numero rappresentato da D si considera sempre minore dell'unita'. D cioe' e' essererappresentato nella forma:

D a a a (a )nn

i= + + + =− − −1

12

22 2 2 1 0. . ........... . ,

Pertanto l'uscita del convertitore D/A e' data da:

( ) )1.3.6(2.a...........2.a2.a.RA nn

22

11

−−− +++=

Da un punto di vista elementare e puramente qualitativo un convertitore D/A potrebbe venirvisto come un potenziometro digitale in cui R e' la tensione applicata ai capi del potenziometro el'angolo di rotazione Θ del cursore (fig. 6.7) e' rappresentato dal numero D.

D/AD

R

A

V

V

ΘΘΘΘ

R

0

fig. 6.7

In tutte le considerazioni finora svolte, tuttavia, non si e' affatto preso in considerazione ilsegno del numero D, che e' stato implicitamente preso come positivo, al pari di R e di A. Cio' non e'sempre vero. Ritornando all'analogia con il potenziometro e' evidente che per farlo operare con am-bedue i segni, ottenendo nel contempo anche un'uscita bipolare, e' necessario prendere opportuniprovvedimenti. La fig. 6.8 illustra due possibili modi con cui si puo' ottenere quanto voluto.

In fig. 6.8 (a) il potenziometro e' connesso tra due tensioni di riferimento, + VR e - VR, e ilriferimento rispetto al quale si misurano le rotazioni e' posto a mezza corsa, in modo che quando Θ= 0 le tensione di uscita V0 sia anch'essa nulla. Per rotazioni positive la tensione di uscita sara'positiva, per rotazioni negative, negativa.

Con riferimento alla fig. 6.7 (b) il segnale Θ e' rappresentato in ampiezza e segnoseparatamente. Un lato del potenziometro e' connesso a massa, l'altro e' commutato, in funzione delsegno di Θ, sui riferimenti +VR e - VR rispettivamente. L'uscita di tale circuito e' evidentemente lastessa di quella del circuito di fig. 6.7 (a), ma per ottenere la stessa tensione di uscita la corsa delcursore dev'essere doppia.

Capitolo VIConversione A/D e D/A

215

+V

V

-V

+V -V

V

R

0

R

R R

0

ΘΘΘΘΘΘΘΘ

ΘΘΘΘ

polarizzato

ampiezza

segno

(a) (b)fig. 6.7

I convertitori D/A operano in modo del tutto simile; in altre parole e' la codifica del segnaledigitale che determina la configurazione del convertitore. Il progetto e la scelta del convertitore piu'adatto ad un sistema non e' affatto semplice. Normalmente un convertitore non soddisfa tutte lespecifiche ed e' necessario ricorrere a soluzioni di compromesso. I principali fattori, comuni a tutti iconvertitori, da tener presenti per ottenere la migliori prestazioni in rapporto alla dimensione, alpeso e al costo sono:

1. Prestazioni.Le prestazioni di un convertitore D/A devono sempre essere commisurate al costo, alle

dimensioni e al peso. Ad esempio il costo di un resistore aumenta esponenzialmente in funzionedella sua precisione. Da un altro punto di vista vi e' sempre un punto nella curva prestazioni-costo diun convertitore, al di sopra del quale qualsiasi miglioramento delle prestazioni, anche piccolo,comporta un costo irragionevolmente alto.

Questo punto nei convertitori D/A di normale impiego si puo' ritenere situato nell'intornodella precisione dello 0.05% (pari a un numero binario di ingresso da 12 bit) su tutto il campo ditemperatura di esercizio.

2. Alimentazioni di riferimento.Tutti i convertitori D/A a funzionamento bipolare richiedono delle tensioni di riferimento

positive e negative, che devono essere stabili e precise entro lo 0.01% del loro valore nominale, se ilconvertitore deve essere preciso entro lo 0.05% del fondo scala. Tali alimentazioni di riferimentodevono avere una bassa impedenza d'uscita, bassa ondulazione residua e basso rumore. In diversicasi inoltre esse devono avere la capacita' di fornire o assorbire rilevanti correnti.

3. Alimentazioni di potenza.Nella maggior parte dei convertitori D/A le alimentazioni di potenza sono necessarie solo per

gli amplificatori (di norma operazionali) presenti. Pertanto il loro valore e' normalmente compresotra ± 12 V e ± 18V.

Le alimentazioni sono di regola uguali in ampiezza e stabili entro l'uno per cento, con bassaondulazione residua, rumore e impedenza d'uscita.

4. Buffers.

Capitolo VIConversione A/D e D/A

216

All'ingresso dei convertitori sono di solito presenti dei buffers digitali in quanto i segnali diingresso si possono ritenere validi solo in determinati istanti. Quando inoltre si operi conconvertitori D/A seriali o con tecniche multiplex anche sull'uscita dovranno venir inseriti dei buffersanalogici.

5. Amplificatori.Nella realizzazione dei convertitori D/A viene di solito usato almeno un amplificatore

operazionale, che somma le varie componenti di corrente e le converte in una tensione di uscita abassa impedenza. Caratteristiche essenziali di un amplificatore operazionale sono gli offset ditensione e corrente e la loro dipendenza dalla temperatura, il guadagno di tensione o di corrente, larisposta di frequenza, la velocita' di salita della tensione di uscita (slew rate) e l'ampiezza massimadell'uscita.

Nei convertitori D/A solamente l'offset rappresenta un reale problema, in particolare se ilconvertitore deve avere una precisione dello 0.05% del fondo scala nel campo di temperatura anorme MIL (-55° C / 125° C). Cio' implica che la tensione di uscita deve mantenersi stabile entro lo0.01% del fondo scala o entro ± 1 mV del valore desiderato.

Nemmeno i piu' sofisticati amplificatori differenziali possono soddisfare queste caratteristichee si devono quindi impiegare delle tecniche di correzione dell'offset e della deriva.

Nel seguito si supporra' che tutti i convertitori che verranno presi in considerazionecorrispondano alle seguenti caratteristiche, quando non verra' altrimenti specificato.

• I segnali analogici di uscita saranno limitati a tensioni continue comprese, se possibile, tra +10 e - 10 volt. I convertitori con uscita in alternata verranno trattati a parte.

• I segnali digitali sanno numeri in forma seriale o parallela, codificati in complemento a 2 obinario offset, come verra' illustrato in un successivo paragrafo.

• Per convenzione si fara' riferimento alla logica positiva. Pertanto nelle realizzazioni contransistori bipolari o CMOS uno zero logico sara' rappresentato da una tensione nulla, un uno logicoda una tensione positiva, mentre nelle realizzazione PMOS uno zero logico sara' rappresentato dauna tensione negativa, un uno logico da una tensione nulla.

• Il campo di temperatura su cui il convertitore dovra' mantenere le sue caratteristiche sara'quello a norme MIL (-55° C / 125° C).

• Gli amplificatori operazionali eventualmente presenti saranno corretti rispetto all'offset e alladeriva entro il ± 0.01% del loro fondo scala. Si assumera' inoltre che tutti gli altri parametriessenziali dell'amplificatore siano tali da non introdurre errori significativi.

6.3.1) Codici di ingresso.

Prima di passare all'esame, sia pure sommario, di alcuni aspetti relativi alla conversione D/Ae' opportuno dare un cenno sui piu' comuni codici utilizzati. E' abbastanza evidente, da quanto gia'visto, che usando la rappresentazione binaria posizionale si possono manipolare solo grandezzeunipolari. Per rappresentare grandezze sia positive che negative e' necessario ricorrere a codicibipolari, in cui a uno dei bit sia attribuito il significato di segno.

I codici piu' diffusi sono:

• Complemento a 2• Binario offset• Complemento a 1• Segno e ampiezza

Capitolo VIConversione A/D e D/A

217

anche se non sono infrequenti altri codici, quali ad esempio il decimale codificato in binario (BCD)o il codice di Gray. In fig. 6.8 sono riportati i diversi codici citati con riferimento a un fondo scalapari a 7.

Numeroriferimento riferimento

e ampiezza Comp. a 2 Comp. a 1 Binario offsetpositivo negativoSegno

765432100

-1-2-3-4-5-6-7-8

7/86/85/84/83/82/81/80+0-

-1/8-2/8-3/8-4/8-5/8-6/8-7/8-8/8

-7/8-6/8-5/8-4/8-3/8-2/8-1/8

0-0+1/82/83/84/85/86/87/88/8

0111011001010100001100100001000010001001101010111100110111101111------

01110110010101000011001000010000

11111110110111001011101010011000

(0000)

01110110010101000011001000010000(1111)1110110111001011101010011000------

11111110110111001011101010010000(1000)0111011001010100001100100001(0000)

fig. 6.8

CODICI

6.3.2) Codice complemento a 2.

Si supponga di voler rappresentare un numero N con n bit. Il massimo numero rappresentabilein numerazione binaria posizionale e' ovviamente il valore 2 1n − .

Nel codice complemento a 2 si limitano i numeri positivi rappresentabili al valore 2n -1 - 1,che puo' venir rappresentato con n-1 bit, in modo che il piu' grande numero positivo rappresentatocontenga sempre uno 0 al rango piu' significativo e degli 1 o degli 0 in tutte le altre posizioni.

Rappresentando allora i numeri negativi con il complemento a 2n, cioe' rappresentando ilnumero -N (N>0) con la quantita' 2n -N e ricordando che N < 2n-1 si deduce che larappresentazione complementata di -N sara' un valore maggiore di 2n-1 e minore di 2n. Cio'significa che nella stringa di n bit, rappresentativa del numero negativo considerato, la posizionepiu' significativa, detta bit di segno, sara' sempre riempita da un 1.

Uno dei vantaggi della rappresentazione complemento a 2 risiede nel fatto che talecomplemento si ottiene con notevole facilita'. Dato il valore assoluto del numero (0 < N ≤ 2n -1 - 1)il complemento a 2 si ottiene semplicemente per negazione di ciascun bit della stringa, sommandopoi un'unita' al risultato ottenuto. Analoga operazione va compiuta quando da un valore negativo sivuol passare al suo valore assoluto.

Va notato a questo proposito che al campo dei numeri negativi rappresentabili appartieneanche quello formato da un 1 nel rango piu' significativo, seguito da tutti 0, pari al valore - 2n -1 ,ma che, con le convenzioni assunte, il suo valor assoluto non e' rappresentabile su n bit.

La diffusione di tale codice e' dovuta al fatto che l'uscita di molti circuiti di controllo e dicalcolo e' in tale forma. La rappresentazione complemento a 2 ha infatti come ulteriore vantaggio ilfatto che la differenza N1 - N2 si ottiene semplicemente sommando a N1 la rappresentazionecomplementata di - N2. Si ha infatti:

( ) ( )21n

2n

1 NN2N2N −+=−+

Se ( ) 0NN 21 ≥− allora il risultato dell'operazione e' maggiore o uguale a 2n e perrappresentare tale valore sarebbe necessaria una stringa di n + 1 bit. Pertanto il bit rappresentativo

Capitolo VIConversione A/D e D/A

218

del rango 2n va perso e nella stringa dei rimanenti n bit rimane pertanto rappresentata proprio lastringa N N1 2− . Se viceversa N N1 2− < 0 allora si puo' scrivere che:

( ) ( )12n

21n NN2NN2 −−=−+

e ricordando che N N n1 2

12 1− < −− nella stringa di n bit si ha proprio la rappresentazionecomplementata del risultato.

Infine con questo codice la rappresentazione dello zero non e' ambigua. Applicando leoperazioni di complementazione descritte ad una stringa formata da tutti zero si ottiene ancora unastringa formata da tutti zero.

E' evidente che se la parola di comando X del convertitore e' nella forma complemento a 2, ilbit piu' significativo dovra' connettere il relativo ingresso ad un generatore di riferimento di segnoopposto a quello degli altri bit.

Uno svantaggio che tuttavia il codice complemento a 2 presenta risiede nel fatto che passandodal valore 0 (00......0) a quello -1 (11......1) tutti i bit della parola commutano. Con riferimento allarealizzazione circuitale dei convertitori paralleli, cio' puo' causare sia dei picchi di assorbimentodalle alimentazioni, siano esse di riferimento che di potenza, sia dei tempi di transitorio rilevanti acausa delle differenti velocita' con cui i vari bit commutano.

6.3.3) Codice binario offset.

Il codice binario offset e' molto simile alla rappresentazione complemento a 2 ed e' il codice diingresso piu' conveniente per un convertitore D/A parallelo. L’unica differenza riscontrabile rispettoal codice complemento a 2 risiede nel fatto che il bit di segno risulta negato.

Da un altro punto di vista si potrebbe dire che l'offset binario e' una numerazione binariaposizionale il cui 0 coincide con il fondo scala negativo della grandezza rappresentata.

Questo codice risulta particolarmente conveniente quando il convertitore debba venirutilizzato sia per grandezze unipolari che bipolari. Si passa infatti dall'uno all'altro tipo difunzionamento con semplici operazioni di spostamento dell'offset.

Con riferimento alla fig. 6.9, che riporta una possibile realizzazione circuitale di principio diun convertitore D/A, risulta evidente che per lavorare in modalita' bipolare il convertitore deve venirpolarizzato. Cio' puo' essere fatto semplicemente connettendo un resistore di polarizzazione Rb trauna sorgente di riferimento -VR e la giunzione somma dell'amplificatore operazionale che provvedea sommare le varie componenti di corrente e a convertirle in una tensione di uscita. Il resistore dipolarizzazione viene aggiustato in modo che la corrente che lo attraversa sia in valor assoluto parialla corrente del rango piu' significativo. In tal caso in presenza di un ingresso binario rap-presentante lo zero (10......0) le correnti di polarizzazione e di ingresso hanno somma nulla, dandopercio' luogo ad una tensione d'uscita nulla.

Per ottenere la modalita' di funzionamento unipolare e' sufficiente non polarizzare ilconvertitore. E' ovvio che per avere lo stesso fondo scala sia in modalita' unipolare che bipolare e'necessario nel primo caso raddoppiare la resistenza di reazione dell'amplificatore operazionale; intal caso tuttavia raddoppia anche il passo di quantizzazione.

Capitolo VIConversione A/D e D/A

219

Ingresso digitaleparallelo

a

a

a

a

+V

-V

R

R

1

2

3

12

20 k

20 k

40 k

80 k

40.96 M

20 k

Vo

-I/2

I/2

I/4

I/8

I/212

fig. 6.9

Uno svantaggio del codice binario offset e' che nel caso di ingresso nullo si puo' avereun'uscita non nulla se la corrente del rango piu' significativo non e' perfettamente bilanciata dallacorrente di polarizzazione. Inoltre anche con tale codice il passaggio dal valore zero (10......0) aquello -1 (01......1) porta ad una massiccia commutazione con tutti gli inconvenienti gia' descritti nelcaso del codice complemento a 2.

6.3.4) Codice segno e ampiezza.

Come lo stesso nome lascia intuire, in questo codice la parola e' divisa in due parti, segno eampiezza. In altre parole la codifica per i numeri negativi e' la stessa che per i numeri positivieccetto che per il bit di segno.

L'utilizzo di questo codice risulta conveniente quando si abbia a che fare con grandezze cheoscillano nell'intorno dello zero, in quanto nel passaggio da valori positivi a negativi e viceversa siha la commutazione di uno o al piu' di qualche bit.

E' tuttavia opportuno notare che questa rappresentazione si rivela poco adatta all'elaborazionenumerica con sistemi di calcolo, che di solito adottano un'aritmetica complemento a 2. Esiste inoltreun'ambiguita' nella rappresentazione dello zero (00.....0 o 10.....0).

6.3.5) Codice complemento a 1.

Il codice complemento a 1 e' molto simile a quello complemento a 2, ma in questo caso ilcomplemento viene realizzato rispetto al valore 2n - 1 anziche' rispetto 2n. Esso presenta ilvantaggio che un numero negativo si ottiene semplicemente negando i singoli bit del corrispondentepositivo. Le operazioni aritmetiche sono tuttavia piu' difficoltose ed esistono due possibilirappresentazioni per lo zero (00......0 e 11......1).

Capitolo VIConversione A/D e D/A

220

da

aSegno e ampiezza Complemento a 2 Binario offset Complemento a 1

nessuna operazioneSe il bit piu' signifi-cativo vale 1 comple-mentare gli altri bit

e sommare 1

Complementare il bit piu' significati-vo e se il nuovo va-lore e' 1 sommare 1

Se il bit piu' signifi-cativo vale 1 comple-mentare gli altri bitSegno e ampiezza

Se il bit piu' signifi-cativo vale 1 comple-mentare gli altri bit

e sommare 1

nessuna operazione

Complementare il

vobit piu' significati-

Se il bit piu' signifi-cativo vale 1 somma-

re 1Complemento a 2

nessuna operazione

Complementare il

vobit piu' significati-

Complementare il bit piu' significati-vo e se il nuovo va-lore e' 0 sommare 1

Complementare il bit piu' significati-vo e se il nuovo va-lore e' 0 comple-mentare gli altri bit e sommare 1

Binario offset

Se il bit piu' signifi-cativo vale 1 comple-mentare gli altri bit

Se il bit piu' signifi-cativo vale 1 somma-

re 11......1

Complementare il bit piu' significati-vo e se il nuovo va-lore e' 1 sommare

11.....1

nessuna operazioneComplemento a 1

TABELLA 6.1Conversione tra codici

Questa sommaria disamina non esaurisce ovviamente tutti i possibili codici.Esistono codici modificati, autocomplementanti, di Gray, etc, i cui vantaggi generalmente

risiedono nelle semplificazioni che permettono di apportare alle reti di commutazione deiconvertitori o nella maggior velocita' di conversione conseguibile.

In tabella 6.1 sono riassunte le operazioni che permettono di passare dall'uno all'altro deicodici descritti.

6.4) I convertitori D/A paralleli.

Si definisce convertitore D/A parallelo quello che accetta come ingresso un segnale binario Xpin forma parallela e utilizza tanti interruttori analogici quanti sono i bit di Xp. Ciascuna linea diingresso di Xp aziona un interruttore che collega una tensione di riferimento VR o la massa adun'opportuna rete resistiva, come illustrato in fig. 6.10.

La rete resistiva normalmente converte la tensione presente su ciascuna linea di ingresso inuna corrente di opportuna ampiezza, che viene sommata con le altre correnti, generate dagli altriinterruttori e resistori. La corrente totale viene poi convertita in tensione, ad esempio facendoricorso a un amplificatore operazionale.

E' ovvio che se il convertitore fosse di tipo bipolare sono necessarie due tensioni diriferimento, l'una positiva e l'altra negativa.

I convertitori paralleli sono i piu' veloci in quanto sono in grado di fornire la tensione di uscitanon appena il segnale digitale di ingresso viene applicato. La velocita' di risposta e' limitataunicamente dalla velocita' degli interruttori analogici, dalle reattanze parassite associate ai resistoridella rete e dalla velocita' di salita degli amplificatori eventualmente presenti.

Capitolo VIConversione A/D e D/A

221

Ingresso

parallelo

a

a

a

a

VR

1

2

3

12

Vo

I/2

I/4

I/8

I/212

fig. 6.10

digitale

Per contro i convertitori paralleli richiedono che il segnale di ingresso sia presente in manieracontinuativa. Poiche' molti circuiti digitali di controllo forniscono l'uscita solo a certi specificiintervalli di tempo, spesso e' necessario prevedere dei circuiti in grado di memorizzare il segnaledigitale tra la presentazione di un dato e l'altro.

Comando dicaricamento

Ingresso parallelo

Uscita parallela

FF 1 FF 2 FF 3 FF n

FF 1 FF 2 FF 3 FF n

FF 1 FF 2 FF 3 FF n

FF 1 FF 2 FF 3 FF n

(a)Comando discorrimento

Ingressoseriale

Uscita parallela(b)

Comando discorrimento

Ingressoseriale

Comando dicaricamento

Uscita parallela

(c)

fig. 6.11

Per segnali che pervengono al circuito in forma parallela la memoria consiste in un flip-flopper ciascun bit (fig. 6.11 (a)) della parola binaria di ingresso. Normalmente non e' prevista alcunatecnica di interlacciamento per il caricamento dei dati, poiche' tale operazione e' pressocche'istantanea e richiede tempi che di solito sono trascurabili rispetto al tempo di conversione.

Per segnali di ingresso che pervenissero invece in forma seriale, viene invece previsto uninsieme di n flip-flop connessi a formare un registro a scorrimento (fig. 6.11 (b)) e vi deveevidentemente essere un clock sincronizzato con i bit della parola seriale. E' essenziale che sia ilnumero degli impulsi di avanzamento che la loro temporizzazione siano esatti.

Capitolo VIConversione A/D e D/A

222

La parola binaria di uscita in forma parallela e' disponibile dopo che il processo dimemorizzazione e' stato completato; e' evidente che durante le operazioni di conversione da serialea parallelo l'uscita del convertitore D/A fornira' delle tensioni errate.

Se l'uscita analogica viene usata come ingresso di sistemi a lunga costante di tempo, taleerrore, generalmente di breve durata, e' di solito tollerato. In caso contrario l'uscita del registro ascorrimento viene accumulata in un buffer parallelo (fig. 6.11 (c)) in modo da evitare tale errore. Ilcomando di caricamento del buffer parallelo viene dato non appena l'operazione di memorizzazionenel registro a scorrimento e' terminata.

6.4.1) Convertitore D/A a resistenze pesate.

Il piu' semplice e diretto metodo di conversione e' quello a resistenze pesate che fa uso di unresistore per bit, secondo lo schema di fig. 6.12 (a).

Le resistenze hanno ciascuna un valore inversamente proporzionale al peso del bit cuirisultano collegate.

R

2R

4R

R

V

+V

-V

R

R 0A

L

R

2R

4R

R

V

4R

+V

-VR

R

M.S.B.0A

L

resistore diterminazione

L.S.B. L.S.B.

M.S.B.

(a)(b)

fig. 6.12

La resistenza di uscita R0 della rete, supponendo che i generatori di riferimento approssiminosufficientemente dei generatori di tensione, e' evidentemente:

1 1 12

14

740R R R R

R= + + =

cioe'

R R047

=

Generalizzando al caso di n bit si ottiene:

1 1 12

12

2 120

1 1R R R RRn

n

n= + + + = −− −......

Capitolo VIConversione A/D e D/A

223

R Rn

n0

122 1

=−

−.

e quindi all'aumentare di n R0 tende al valore R/2.La tensione di uscita e' ovviamente funzione della parola binaria di ingresso. E' facile vedere

che con l'i-esimo bit posto a 1 e tutti gli altri a 0 la tensione di uscita, con resistenza di caricoinfinita, vale :

V Vi

n

n R0 1

112

22 1

=−−

−. .

e quindi per sovrapposizione degli effetti

Rn

1n

n1n3210 V.12

2.b.21......b.

41b.

21bV

−

++++=

−

−

Qualora non si possa trascurare l'effetto del resistore di carico RL la tensione di uscita sara':

V V RR R

L

L0 0

0

' .=+

Spesso la rete viene modificata con l'aggiunta di un resistore di valore pari a quello del bitmeno significativo, come illustrato in fig. 6.12 (b). In tal caso l'impedenza d'uscita e' sempre pari aR/2, indipendentemente dal numero di bit della parola digitale. Anche l'espressione della tensionedi uscita ne risulta semplificata. Si ha che:

Rnn3210 V.b.21......b.

81b.

41b.

21V

++++=

Un vantaggio della rete a resistori pesati risiede nel fatto che la corrente che il generatore diriferimento deve fornire diminuisce con il diminuire della significativita' del relativo bit. D'altraparte all'aumentare del numero di bit della parola digitale il valore dei relativi resistori cresceesponenzialmente e resistori molto precisi di elevato valore sono difficili sia da realizzare che moltocostosi, anche quando non si volesse tener conto delle costanti di tempo introdotte dalle capacita'parassite, che limitano la velocita' operativa, e delle conduttanze parassite fonte di errore.

Non e' ovviamente pensabile di superare questi inconvenienti riducendo oltre un certo limitela resistenza relativa la bit piu' significativo.

Pertanto la realizzazione a resistori pesati non viene in pratica utilizzata quando la paroladigitale ha un numero di bit superiore a otto.

La precisione dei convertitori a resistenze pesate e' migliore dello 0.1% del fondo scala se siassume che la tensione di riferimento abbia una tolleranza massima dello 0.01%, che la tolleranzadei resistori sia inferiore allo 0.05% e che l'errore introdotto dagli interruttori sia limitato allo0.05%. La velocita' di conversione e' limitata, come gia' osservato, dai tempi di commutazione degliinterruttori e dalle reattanze parassite.

Gli interruttori usati sono di solito serie-parallelo, come quello illustrato in fig. 6.13. I duegate sono pilotati in controfase in modo che ci sia sempre uno dei due MOS in conduzione e che

Capitolo VIConversione A/D e D/A

224

l’impedenza vista dall’ingresso della rete di conversione sia approssimativamente costante sia nellostato ON che in quello OFF dell’interruttore.

C

C

VR

figura 6.13

6.4.2) Convertitore D/A con rete resistiva a scala.

I convertitori D/A con rete resistiva a scala (resistor ladder D/A converter), malgrado usino unnumero di componenti maggiore che non i convertitori con resistenze pesate, sono il tipo diconvertitore piu' largamente diffuso.

In fig. 6.14 (a) e' riportata la rete di conversione di un convertitore da quattro bit (fondo scala ± 7). Si puo' notare che vengono usati solamente due valori di resistenza, R e 2R.

E' facile calcolare la resistenza di uscita, pari a R, di tale rete, supponendo che tutti gliinterruttori siano connessi a massa. In tal caso infatti il circuito equivalente e' quello illustrato in fig.6.14 (b). Questo valore di impedenza di uscita si conserva anche quando gli interruttori non sonocommutati a massa, purche' l'impedenza interna dei generatori di riferimento sia trascurabile rispettoR.

1

2

3

4

R

R

2R

2R

2R

2R

b

b

b R

b

+V

-V

R

R4

3

2

1

L

R

R

2R 2R 2R 2R

uscita4

5

6

123

5

6

(a)

(b)

fig. 6.14

Il valore scelto per R dipende dal valore del carico RL, dalle variazioni che tale carico puo'subire e dalla precisione del sistema. Solo nel caso in cui il carico sia di valore molto elevato, al

Capitolo VIConversione A/D e D/A

225

limite un circuito aperto, il valore di R e' determinato essenzialmente da considerazioni di velocita'operativa. Quanto piu' bassa e' R tanto minore sara' l'impedenza di uscita e di conseguenza tantomeno sensibili saranno gli effetti delle capacita' e delle conduttanze parassite.

La tensione di uscita a vuoto e' anche in questo caso calcolabile per sovrapposizione deglieffetti considerando che solo un bit alla volta valga 1 (a parte il bit di segno che determinaunivocamente il segno della tensione di uscita). Con riferimento alla fig. 6.14 (a), indicando conb4b3b2b1 la parola binaria di ingresso e supponendo di operare a circuito aperto si ottiene:

con b3b2b1= 100

V VR012

=

con b3b2b1= 010

V VR014

=

con b3b2b1= 001

V VR018

=

In definitiva:

R1230 V.b.81b.

41b.

21V

++=

La tensione di uscita sara' quindi compresa tra 0 e i 7/8 della tensione di riferimento VR. Larete pertanto quantizza la tensione di riferimento in un appropriato numero di passi uguali, messi inrelazione con il numero rappresentato dalla parola binaria di ingresso. Estendendo quanto esposto aparole di n bit, il passo di quantizzazione diviene ovviamente 1/2n , mentre il fondo scala e'determinato dal massimo valore rappresentabile sugli n bit. Si ha cioe':

( ) nRn

fs0 2V.12V −=

In generale la tensione di uscita sara':

Rnn210 V.b.21......b.

41b.

21V

+++=

avendo indicato con b1 il bit piu' significativo della parola digitale di ingresso.Se la resistenza RL di carico non fosse infinita la tensione di uscita che si ottiene e'

ovviamente:

V V RR R

L

L0 0' .=

+

Capitolo VIConversione A/D e D/A

226

6.4.2) Altri tipi di convertitori D/A.

Oltre i tipi di convertitore D/A visti ne esistono ovviamente altri con strutture circuitalidiverse.

Tra essi puo’ venir citato il convertitore D/A a correnti pesate illustrato in figura 6.15, distruttura particolarmente semplice.

4/7 I

2/7 I

1/7 I

V0A

R L

fig. 6.15

Esso si avvale di generatori di corrente comandati, che in caso di uscita unipolare sono moltofacili da realizzare. Qualche difficolta’ si puo’ avere per quanto riguarda l’accuratezza dello zero acausa delle correnti di perdita in particolare quando si operi ad alta temperatura. Inoltre, quando laresistenza di carico RL assume elevati valori, puo’ diventare alquanto problematico realizzaresorgenti che abbiano resistenza d’uscita molto maggiore di quella di carico.

Di conseguenza la conversione a correnti pesate risulta conveniente solo in sistemi diconversione di precisione medio-bassa in cui tuttavia si desiderino velocita’ di conversione elevate.

Un’ulteriore tipologia di convertitore D/A e’ quella detta a tensioni pesate, il cui schema diprincipio e’ riportato in figura 6.16.

fig. 6.16

R

R

R

R

R

R

R

R

RR/2

R/6

R/(2n- 2)a

a

a

a

VR

1

2

3

n

V0

ingressobinarioparallelo

Capitolo VIConversione A/D e D/A

227

In esso vengono generate frazioni binarie di corrente I/2, I/4, ...., I/2n dividendo la tensione diriferimento in frazioni binarie con divisori resistivi del tutto convenzionali e sommando tali frazionialla giunzione somma di un amplificatore operazionale. Viene usato un interruttore per ciascun bitdel segnale di ingresso, controllato ciascuno da una separata linea di comando. Quando il livello delsegnale di controllo e' basso (zero logico) l'interruttore e' aperto e una corrente fluisce attraverso laresistenza di ingresso fino alla giunzione somma, mentre quando e' il segnale di controllo e’ allivello alto l'interruttore e' chiuso cortocircuitando a massa il resistore di ingresso.

Un convertitore D/A a tensioni pesate da 12 bit consiste pertanto di 48 resistori, di cui 36 diprecisione, di dodici transistori e di un amplificatore operazionale. I dodici transistori sono pilotatidirettamente dalle 12 linee che rappresentano il segnale binario di ingresso. Tali transistori sonoconnessi in configurazione inversa in modo da dar luogo a basse tensioni di offset. A titolo diesempio si puo' dire che con una corrente di base di 2 mA e una corrente di carico di 0.25 mA lamassima tensione di offset e' minore di 1 mV sull'intero campo di temperatura.

Il valore delle resistenze serie deve venir scelto come soluzione di compromesso tra l'esigenzadi avere basse correnti di carico nel transistore di commutazione e quella di mantenere le resistenzele piu' basse possibili. Un valore che soddisfa abbastanza bene tali esigenze di aggira sui 40 kΩ.

Le due esigenze si potrebbero in effetti conciliare diminuendo la tensione di riferimento, macio' introdurrebbe altri problemi, facendo aumentare il rapporto tra le tensioni da commutare e latensione di offset.

Il valore delle resistenze da inserire in parallelo puo' venir calcolato dalla relazione:

22RR ipi −

= i = 1, 2, ...., n

che si ricava immediatamente qualora si consideri che al punto di inserzione dell'interruttore, ainterruttore aperto, deve essere presente una tensione pari a:

VRi2

6.4.3) Pilotaggio di una giunzione somma.

L'uscita di uno qualsiasi dei convertitori descritti in precedenza, con l’eccezione di quello atensioni pesate, in cui tale provvedimento e’ gia’ presente nella struttura base, puo' essere connessaad una giunzione a somma nulla che si puo' ottenere facendo si' che la corrente fornita dalconvertitore D/A sia uguale ed opposta a quella fornita da altre sorgenti. Operando in tal modo si fasi' che la giunzione somma sia sempre a tensione nulla, come se l'uscita del convertitore fossecortocircuitata a massa.

Un possibile esempio e' riportato in fig. 6.17, in cui l'uscita di un convertitore a resistenzepesate e' collegata alla giunzione somma di un amplificatore operazionale.

E' opportuno ricordare che se il guadagno a catena aperta dell'amplificatore e' sufficientementeelevato, la tensione presente alla giunzione somma e' praticamente nulla (massa virtuale) indipen-dentemente dalla tensione V0A presente all'uscita dell'amplificatore stesso.

In tali condizioni ciascun bit della parola digitale di ingresso che si trovi al valore logico 1opera come una sorgente di corrente e alla giunzione somma deve essere soddisfatta la condizione:

I b I b I b I b IF1 1 2 2 3 3 4 4 0. . . .+ + + − =

Capitolo VIConversione A/D e D/A

228

avendo indicato con Ii la corrente entrante alla giunzione somma per effetto del bit i-esimo e con IFla corrente uscente lungo la resistenza RF.

R

2R

4R

R

V

+V

-V

R

R

0A

F

8R

massa virtuale

giunzione somma

K

fig. 6.17

b

b

b

b

1

2

3

4

Trasportando il tutto al caso di n bit si ottiene:

+++= − R.2

b......R.2

bRb.VI 1n

n21RF

Poiche' V0A = - IF.RF, si ha in definitiva:

+++−= − R.2

b......R.2

bRb.R.VV 1n

n21FRA0

e il fondo scala e' dato da:

0

FRFS0 R

R.VV −=

dove R0 rappresenta l'impedenza di uscita della rete di conversione.In sostanza la relazione trovata e' formalmente identica a quella che era stata ricavata in

assenza dell'amplificatore operazionale. In questo caso tuttavia si consegue il vantaggio di poterscegliere entro certi limiti il valore della tensione di fondo scala scegliendo opportunamente ilvalore di RF e di rendere la tensione di uscita indipendente dal valore della resistenza di carico. E'bene osservare tuttavia che nelle realizzazioni integrate dei convertitori D/A molto spesso laresistenza di reazione viene essa stessa integrata nel dispositivo.

E' infine opportuno illustrare un uso non del tutto convenzionale dei convertitori D/A presi inesame. Con alcune semplici considerazione si ottiene che un convertitore connesso alla giunzionesomma di un amplificatore operazionale fornisce in uscita dello stesso la tensione:

+++=− n

n21FR0 2

b......4b

2b.

RR.VV

Capitolo VIConversione A/D e D/A

229

avendo indicato con RF la resistenza di reazione e con R l'impedenza di uscita della rete diconversione. Considerato che:

b b b b b b Bnn

n nn

n n1 2 1

12

2 0

2 4 22 2 2

2 2+ + + = + + + =

− −...... . . ...... .

dove con B si e' indicato il valore rappresentato dalla parola binaria di ingresso, risulta evidente che,se all'ingresso viene applicato un segnale Vi anziche' una sorgente di riferimento VR, in uscita siottiene una tensione:

V V R BRi

Fn0 2

= − . ..

Si ottiene cioe' un amplificatore invertente il cui guadagno puo' essere controllato, con laprecisione propria dei convertitori D/A, attraverso l'uso di una parola digitale B da n bit tra unvalore nullo, quando B = 0, e il valore:

RR

Fn

n.2 12

−

quando B e' tutta formata da 1. Il guadagno puo' essere controllato in passi discreti di ampiezza:

RR

Fn. 1

2

In sostanza il convertitore puo' essere visto come una resistenza variabile di valore

RB

n.2

E' ovvio che il convertitore D/A puo' essere inserito anche nel loop di reazione. Il tal casol'espressione del guadagno e':

VV

RB

Ri

n

i

0

2

= −.

Anche in questo caso si ottiene un amplificatore il cui guadagno e' controllabile attraverso unaparola binaria, ma il legame tra il guadagno e B e' di proporzionalita' inversa. Per questo motivomolto spesso in parallelo al convertitore viene connessa una resistenza fissa RF e il convertitoreviene utilizzato unicamente per ottenere piccole variazioni del guadagno nell'intorno del valorenominale.

Quale ultima considerazione relativa ai convertitori che fanno uso di amplificatorioperazionali (in sostanza tutti i convertitori reperibili in commercio) e' necessario far notare che lecaratteristiche dell'amplificatore condizionano le prestazioni globali.

Le caratteristiche essenziali da prendere in considerazione in questo caso sono, come gia'accennato, gli offset di tensione e di corrente e la loro dipendenza dalla temperatura, il guadagno, larisposta di frequenza, lo slew rate e la massima ampiezza dall'uscita.

Capitolo VIConversione A/D e D/A

230

Nella maggior parte dei casi tuttavia solo l'offset costituisce un reale problema, in particolarese il convertitore deve avere una precisione dello 0.05% del fondo scala nella gamma di temperaturaa norme MIL (-55° - 125° C). Cio' implica infatti che la tensione di uscita si debba mantenerestabile entro il ± 0.01% del fondo scala o entro ± 1 mV del valore desiderato.

Nemmeno i piu' sofisticati amplificatori differenziali possono soddisfare questi requisiti e sidevono quindi applicare opportune tecniche di correzione dell'offset e della deriva.

Infine anche le alimentazioni degli amplificatori rivestono la loro importanza. Esse sonogeneralmente duali e nonostante il buon PSRR (Power Supply Rejection Ratio) degli amplificatoricorrentemente disponibili e' necessario che esse siano uguali in ampiezza, stabili entro il ± 1%, abasso rumore, a bassa ondulazione residua con un'impedenza d'uscita la piu' bassa possibile.

6.4.3) Il convertitore D/A con rete a scala invertita.

Tutti i convertitori presi in esame fino a questo momento presentano una rete di resistori postatra gli interruttori analogici e l'amplificatore operazionale (fig. 6.18 (a)). Questa disposizionecircuitale da' luogo a parecchi inconvenienti. E' necessario infatti commutare tensioni relativamenteelevate rendendo necessari dei piloti a tensione elevata, che sono complessi e lenti. Le correnti cheattraversano i resistori variano al passaggio degli interruttori dallo stato ON a quello OFF eviceversa. Poiche' tutti i resistori presentano elementi parassiti induttivi e capacitivi, le correnti chevi fluiscono vanno a regime in un tempo che dipende dall'entita' degli elementi parassiti. Infine,come si e' gia' detto, per aumentare la velocita' i resistori dovrebbero essere di basso valore, mentreper ottenere la massima precisione tale valore dovrebbe essere elevato, in particolare rispettoall'impedenza di conduzione degli interruttori.

Tutti questi problemi possono essere evitati, senza avere alcun inconveniente, se la posizionedella rete resistiva e degli interruttori viene invertita come illustrato in fig. 6.18 (b).

ingressodigitale

V

V

Interruttori

analogici

di tensione

Interruttori

analogici

di tensione

Rete

resistiva

Rete

resistiva

ingressodigitale

V

V0

0

R

R

(a)

(b)

fig. 6.18

Capitolo VIConversione A/D e D/A

231

Se, ad esempio, nel convertitore con rete resistiva a scala la posizione degli interruttori e deiresistori venisse invertita, come illustrato in fig. 6.19, dal punto di vista del funzionamento noncambierebbe nulla tranne che per le specifiche che gli interruttori dovrebbero soddisfare.

Nella configurazione normale gli interruttori connettono i resistori di ingresso a una tensionedi riferimento VR o a massa. Nella configurazione invertita lo stesso interruttore, posto tra resistoree giunzione somma dell'amplificatore operazionale, permette di inviare la relativa corrente o allagiunzione somma citata o di richiuderla a massa. Connettendo la tensione di riferimento a quella chenormalmente e' l'uscita della rete a scala e connettendo a massa (eventualmente alla massa virtualedell'amplificatore operazionale) quelli che normalmente sono gli ingressi, nei resistori di ingressocircoleranno delle correnti che sono delle frazioni binarie e che vengono poi opportunamentesommate alla giunzione somma dell'operazionale.

R

R

R

2R

2R

2R

2R

VR

2R 2R

V0

fig. 6.19

In relazione agli interruttori si possono fare due considerazioni; innanzi tutto l'interruttorediviene un commutatore di corrente, di piu' facile realizzazione. In secondo luogo le resistenze dellarete a scala possono essere grandi quanto si vuole poiche' le reattanze parassite perdono di impor-tanza in quanto la corrente che circola sui resistori e' costante.

Un convertitore del tipo descritto richiede un interruttore e due resistori di precisione perciascun bit. Gli interruttori tuttavia risultano notevolmente meno complessi di quelli dellarealizzazione tradizionale. Infatti, poiche' le resistenze della rete a scala possono essererelativamente alte non e' necessario usare interruttori con impedenze di conduzione molto basse.L'unico fattore che limita il valore delle resistenze della rete e' il loro ingombro che in una certamisura puo' essere considerato proporzionale al valore resistivo. Un buon compromesso siraggiunge di solito con R = 25 ÷ 50 kΩ.

Con questi valori resistivi un interruttore che abbia un'impedenza di conduzione di 75 Ωintroduce un errore di non linearita' di solo lo 0.03%. Questo errore inoltre puo' essere facilmentecorretto con un piccolo resistore di compensazione in serie con il resistore di reazione.

6.4.4) Precisione e accuratezza di conversione.

Le relazioni, che si sono trovate per i vari tipi di convertitore descritti ai paragrafi precedenti,sono state ricavate nell'ipotesi di interruttori e resistori ideali. Nella pratica le cose vannodiversamente in quanto i valori resistivi presenteranno sempre una certa tolleranza rispetto ai lorovalori nominali e gli interruttori, normalmente allo stato solido, avranno una resistenza di con-duzione non nulla e una corrente di perdita anch'essa non nulla quando si troveranno nello statoOFF.

Capitolo VIConversione A/D e D/A

232

C'e' inoltre da osservare che anche il segnale di pilotaggio degli interruttori puo' in una certamisura presentarsi in uscita, introducendo un ulteriore errore.

In fig. 6.20 (a), nella quale si e' fatta l'ipotesi che il bit piu' significativo della parola binaria siaal valore logico 1 mentre quello immediatamente successivo sia al valore logico 0, sono illustrati iparametri tipici che contribuiscono a diminuire la precisione di conversione.

Le relazioni che sono state trovate in precedenza per la tensione di uscita erano funzione didue sole quantita'; il valore della tensione di riferimento commutata da interruttori ideali postiall'ingresso della rete resistiva ed i valori nominali dei resistori stessi.

Introducendo nelle relazioni i valori reali anziche' quelli ideali per VR e R si possono valutaregli effetti sulla precisione.

E' bene notare che tutte le cause di errore possono esser fatte rientrare o nella tensioneequivalente di riferimento o nel valore relativo al resistore associato ad un particolare bit.Nell'esempio, che si sta trattando, gli errori che possono essere associati alla rete resistiva sono letolleranze ±∆R e l'impedenza dinamica rs dell'interruttore definita come:

r vis

ac

ac=

con vac tensione presente ai capi dell'interruttore in presenza di una corrente iac (a piccoli segnali),nelle condizioni di funzionamento previste.

fig. 6.20

VR r∆VR

g±±±±

V rswitch on

±±±± ∆∆∆∆R R

IPilota dello switch

OF s

R switch off

V0A

agli altri bit

±±±± ∆∆∆∆ 2R 2RI R

switch off

rs

VOF

switch onPilota dello

switch

I D

ID

bit piu' significativo(1)

bit immediatamente successivo(0)

V±±±±∆∆∆∆ RV

R(ID + IN).rg

VOF rs ±±±± ∆∆∆∆R R

±±±± ∆∆∆∆ 2R 2RVOF rs

agli altri bit

(b)

(a)

VOF, detta tensione di offset, e' invece la tensione che esiste ai capi di diversi tipi di interrut-tore analogico anche in assenza di corrente. In altre parole VOF non e' funzione della corrente che

Capitolo VIConversione A/D e D/A

233

fluisce attraverso l'interruttore verso la rete resistiva, ma e' generata all'interno del circuito a causadel segnale di pilotaggio e si presenta ai suoi terminali in condizioni ON.

Se ad esempio come interruttore venisse utilizzato un normale diodo al silicio, commutandoloin conduzione con una corrente di 1 mA, si avrebbe una tensione di offset VOFapprossimativamente di 0.6 volt. Tale tensione va algebricamente sommata alla tensione diriferimento.

Anche l'impedenza della sorgente rg deve venir tenuta in considerazione, soprattutto quando lacommutazione dell'interruttore fa circolare su rg una corrente, dando luogo ad un errore nellatensione di riferimento.

±∆VR rappresenta le variazioni di VR con il tempo, la temperatura, etc.La corrente di perdita dell'interruttore OFF il piu' delle volte si puo' invece trascurare in

quanto e' di modestissima entita' e circola su rs e rg che normalmente sono di basso valore.In fig. 6.20 (b) e' riportato un circuito equivalente semplificato dell'esempio precedente, in cui

sono state eliminate le sorgenti di errore meno significative, come ad esempio IR. rg e' statasostituita da una tensione equivalente di errore pari a (ID + IN).rg in serie con il riferimento.

Si tenga ora presente che il bit piu' significativo contribuisce all'uscita per circa la meta' dellatensione di fondo scala. Pertanto qualsiasi errore in serie con la tensione di riferimento contribuiscein uscita con un errore pari alla meta' del suo valore. Il bit successivo contribuisce con peso 1/4 ecosi' via fino al bit meno significativo, che contribuisce con un peso pari a 1/2n.

E' quindi evidente che e' necessario curare al massimo tutti i circuiti relativi al bit piu'significativo per mantenere piccolo l'errore in uscita, mentre l'esigenza di elementi precisi e stabili siva via via riducendo man mano che si procede verso i bit meno significativi.

Queste considerazioni sono vere anche per i resistori della rete a scala e per le resistenze seriedegli interruttori, che connettono la sorgente di riferimento alla rete stessa.

Per meglio chiarire le cose si supponga di avere a che fare con un convertitore da 10 bit. Ilpeso del bit meno significativo e' 1/1024 e quindi anche se il resistore relativo ha una tolleranza del10% esso determina in uscita un errore che e' solamente lo 0.01% del fondo scala. Sulla base diqueste considerazioni e' intuibile che l'accuratezza totale e' dello stesso ordine di grandezza di quelladei singoli resistori. Infatti, detta p l'accuratezza percentuale dei resistori e P l'accuratezzapercentuale dell'uscita rispetto il fondo scala, si ha:

p21......

41

21.pP n ≅

+++=

6.5) I convertitori D/A seriali.

Da quanto esposto ai paragrafi precedenti si puo' intuire che i convertitori paralleli sononotevolmente veloci. Essi tuttavia richiedono un considerevole numero di componenti. D'altrondespesso la loro elevata velocita' non puo' venir utilizzata poiche' il segnale di ingresso e' in formaseriale, l'amplificatore d'uscita e' lento oppure il sistema analogico che utilizza l'uscita del conver-titore ha delle costanti di tempo molto grandi e quindi non e' richiesta un'elevata velocita' operativa.

Per tali motivi sono stati sviluppati convertitori D/A seriali, ottenendo una maggiorsemplicita’ circuitale, con un minor numero di componenti e a minor costo, a spese della velocita'.Cio' non significa naturalmente che tutti i convertitori seriali siano lenti; spesse volte, come nel casodei convertitori ciclici, essi sono rapidi almeno quanto un convertitore D/A parallelo che agisca inunione con un buffer serie-parallelo.

Tutti i convertitori seriali si basano sul principio operativo illustrato in fig. 6.21. Il segnalebinario di ingresso XSB controlla il funzionamento del convertitore bit per bit. Se durante il periodo

Capitolo VIConversione A/D e D/A

234

attivo di clock Ti il segnale XSB e' al valore logico 1 alla tensione Vi immagazzinata in uncondensatore (rappresentato in figura dal blocco memoria analogica) viene sommata la tensione diriferimento VR e la somma risultante viene divisa per due. Se XSB e' zero allora Vi viene semplice-mente ridotta a meta'. Come risultato di queste operazioni si ha una tensione Vi+1, che vienememorizzata nella capacita' in modo da essere disponibile al successivo periodo di clock Ti+1. Si hacioe':

( )Rii1i V.aV.21V +=+

dove ai e' il bit della parola binaria XSB al tempi Ti.La tensione immagazzinata nella capacita' durante l'ultimo tempo di bit rappresenta l'uscita del

convertitore. Poiche' tale tensione e' disponibile soltanto durante un breve periodo durante ciascuntempo di parola e' necessario un circuito di ritenuta per ottenere una tensione di uscita costante.

1/2

Memoria analogica

VVi+1

i+

+V

-V

R

R

XSB (TS)

XSB (Ti )

fig. 6.21

I convertitori seriali usualmente operano ad una frequenza fc di clock pari a quella del segnaledi ingresso. In altre parole il funzionamento del convertitore e' sincronizzato dalla temporizzazionedel segnale binario di ingresso XSB. Tale segnale e' normalmente fornito direttamente al converti-tore, il bit meno significativo per primo, e l'eliminazione di qualsiasi tipo di buffer realizza unaconsiderevole economia circuitale.

All'inizio della conversione e' evidentemente necessario forzare la tensione Vi a zero e taleoperazione viene effettuata mediante un impulso di sincronizzazione immediatamente seguente ilperiodo del bit piu' significativo. Tale impulso riazzera la tensione Vi del condensatore dopo avertrasferito il valore ivi presente a un circuito di ritenuta.

I convertitori D/A seriali si prestano molto bene a tecniche di multiplazione poiche' sial'ingresso che l'uscita sono realizzati con una singola linea. Utilizzare un convertitore seriale da 12bit per 10 segnali di ingresso richiede un commutatore elettronico ad una via e 12 posizioni, doveper ottenere la stessa cosa con un convertitore parallelo sarebbe necessario un commutatore a 12 viee 10 posizioni.

Per ragioni di semplicita', pur senza togliere nulla alla generalita' della descrizione, nel seguitoverranno presi in esame solo convertitori seriali unipolari. Essi possono d'altra parte esseretrasformati in dispositivi a funzionamento bipolare con semplici tecniche, che tuttavia dipendono

Capitolo VIConversione A/D e D/A

235

dal tipo di rappresentazione usato per il segnale binario di ingresso; ne' la presentazione in modulo esegno, ne' la presentazione binaria offset sono molto pratiche per convertitori seriali afunzionamento bipolare e non saranno quindi prese in considerazione.

Al contrario la rappresentazione complemento a 2 o a 1 puo' essere implementata su qualsiasiconvertitore seriale con l'aggiunta di un unico interruttore analogico e di una tensione di riferimento-VR, come illustrato sempre in fig. 6.21. L'interruttore analogico commuta tale tensione di riferi-mento all'ingresso del convertitore durante il periodo di clock Ts relativo al bit di segno. In tal modola tensione VR viene sottratta dalla tensione Vi. Per operazioni bipolari quindi la relazioneprecedentemente trovata va modificata in:

( )Rii1i V.aV.21V +=+ per sii ≠

( )Risis V.aV.21Vu −= per sii =

dove is e' l'indice relativo all'ultimo bit dell'ingresso, cioe' quello piu' significativo.Con lo stesso ingresso binario l'uscita di un convertitore seriale bipolare e' sempre la meta' di

quella di un convertitore unipolare. Cio' e' ovviamente dovuto al fatto che il bit piu' significativo e'utilizzato allo scopo di realizzare operazioni bipolari.

6.5.1) Il convertitore seriale Shannon-Rack.

Il convertitore Shannon-Rack risolve il complesso problema della conversione D/A serialericorrendo a un minimo numero di componenti e sfruttando la curva esponenziale di scarica di uncondensatore.

Nello schema di principio di fig. 6.22 un generatore di corrente carica con una correntecostante Ic una capacita' C durante la prima meta' di ciascun periodo di clock quando il segnalebinario all'ingresso rappresenta un uno logico.

X

f

f

T

f

I

S

SS

C R

VS

C

V04

st

3

c

2

1

c

SB

c

c

c

s

f c

fig.6.22

G1

G

G

2

3

Durante la seconda meta' del periodo di clock la capacita' C viene scaricata sulla resistenza Rmediante l'interruttore analogico S3.

Capitolo VIConversione A/D e D/A

236

Se invece durante un particolare periodo di clock il segnale di ingresso XSB e' uno zero logicola capacita' C non viene caricata, non essendo abilitato il relativo gate G1, mentre la scarica durantela seconda meta' del periodo di clock avviene comunque.

La scarica esponenziale della capacita' puo' essere messa in relazione con gli impulsi dellaparola seriale di ingresso dalla relazione:

V Vc Rk= −.2

dove Vc e' la tensione ai capi della capacita' dopo il k-esimo periodo di clock e VR e la tensioneiniziale ai capi del condensatore dopo la prima meta' del primo periodo si clock.

Affinche' cio' sia vero e' sufficiente che:

R TC

lnc=2

2.

.

dove Tc rappresenta il periodo di clock.La relazione appena introdotta mostra che durante la seconda meta' di ciascun periodo di clock

la tensione ai capi della capacita' C viene dimezzata. Tenendo presente che, per ciascun uno logicopresente nel segnale di ingresso, la tensione ai capi della capacita' viene aumentata di VR durante laprima meta' del periodo di clock, ne risulta che alla fine di ciascun periodo tale tensione puo' essereespressa con una conveniente frazione di VR. Al numeratore di tale frazione si avra' il valoredecimale rappresentato dal segnale binario di ingresso pervenuto fino a quell'istante, mentre al de-nominatore si avra' la potenza di due relativa alla posizione dell'ultimo bit pervenuto. In sostanza siha:

V V aCk R ii k

i

k= − −

=∑. .2 1

1

dove con VCk si e' indicata la tensione ai capi del condensatore dopo il k-esimo periodo di clockmentre ai e' il bit al periodo i-esimo.

A titolo di esempio si consideri l'ingresso binario da 8 bit 00101011 = 4310. In fig. 6.23 sonoriportati il segnale binario di ingresso ordinato dal bit meno significativo al piu' significativo e latensione ai capi della capacita' C in funzione del tempo. L'uscita Vu e' la tensione Vc ai capi dellacapacita' durante la prima meta' del nono periodo di clock ed e' proporzionale all'ingresso digitaleXSB.

Nello schema di principio di fig. 6.22 i componenti base del convertitore Shannon-Rack sonoun generatore a corrente costante, quattro interruttori analogici, due amplificatori di separazione,due capacita' di memoria e tre gate AND.

Vi e' una grande varieta' di scelta tra gli interruttori, siano essi realizzati con transistoribipolari o a FET. La scelta piu' opportuna viene a dipendere dalla logica usata nella parte bipolare dicontrollo. In linea di massima si puo' affermare che con logiche bipolari si rivelano maggiormenteadatti i FET a giunzione, mentre con logiche MOS o CMOS vengono preferiti gli interruttori MOS

Capitolo VIConversione A/D e D/A

237

T T T T T

f

Sincronismo

1 1 0 1 0 1 0 0 0 1X

V

V

c

R

2

SB

c

1 2 3 9 1

VV

V V

V

V

R

R

R

R

R

R

34

38

1116

1132

4364

43128

VR43256

2 2 2 2 2-8 -7 -6 -1 -8

fig. 6.23

Ts

Le funzioni svolte dai quattro interruttori dello schema di massima riportato in fig. 6.22 sonole seguenti:

• S1 permette la carica alla corrente costante Ic della capacita' C durantela prima meta' di ciascun periodo Ti di clock nell'ipotesi che durantetale intervallo di tempo XSB valga 1.

• S2 cortocircuita C in modo da scaricarlo durante il periodo di reset Ts.

• S3 connette la capacita' C alla resistenza R durante la seconda meta' di Ti per scaricarla esponenzialmente.

• S4 trasferisce durante la prima meta' del periodo di reset la tensione Vc ad un circuito di ritenuta formato dal condensatore Cst e da un amplificatore operazionale.

Quale amplificatore di separazione tra la rete RC e il circuito di ritenuta viene impiegato uninseguitore di tensione, che presenta un'impedenza di ingresso estremamente elevata, rendendosuperfluo l'uso di uno stadio di ingresso a FET.

L'interruttore S4 in unione con Cst e un secondo inseguitore di tensione realizza il circuito diritenuta. Tale circuito non richiede particolari caratteristiche di velocita' essendo la tensione Vccostante durante la prima meta' del periodo Ts di reset.

Sebbene il convertitore Shannon-Rack sia estremamente semplice dal punto di vista circuitale,esso non e' mai stato usato in forma estensiva. La ragione risiede nel fatto che tale tipo diconvertitore non e' molto preciso. Tuttavia utilizzando dispositivi FET o MOS e amplificatori

Capitolo VIConversione A/D e D/A

238

operazionali di basso offset e elevata impedenza di ingresso, appare ragionevole parlare di unaprecisione dello 0.1% del fondo scala. E' necessario d'altra parte prevedere una regolazione dellarete RC in quanto la sua costante di tempo deve venir determinata sulla base della frequenza fc diclock. Inoltre e' molto discutibile quale sia la gamma di temperatura su cui la precisione citata puo'essere mantenuta, in quanto e' difficile e costoso produrre condensatori con coefficiente di tempera-tura molto basso. Infine il progetto di ogni circuito lineare e' generalmente un compromesso traprestazioni statiche e dinamiche. Cio' e' vero in modo particolare per il convertitore Shannon-Rack,in cui la temporizzazione dei vari passi operativi e' essenziale in rapporto alla precisione statica.

Per quanto riguarda la velocita' di conversione e' ovvio che essa e' determinata interamentedalla velocita' degli interruttori analogici. Ad esempio con tempi di commutazione di 300 nsec. lafrequenza del clock non deve superare approssimativamente i 10 kHz se si vuole che gli erroridovuti agli interruttori analogici non superino lo 0.1%. Cio' da' luogo a un tempo totale di con-versione di 1.2 msec. per parole digitali da 12 bit.

6.5.2) Il convertitore seriale “sample-hold”.

Un tipo diverso di convertitore seriale e' quello sample-hold o convertitore a ritenuta,realizzato con tre circuiti S/H e il cui schema di principio e' riportato in fig. 6.24.

Il principio di funzionamento di ciascuno di questi tre circuiti e' identico; quando l'interruttoreS e' chiuso il condensatore C si carica alla tensione V, combinazione lineare delle tensioni presentiall'ingresso del circuito di ritenuta stesso. Quando l'interruttore S e' aperto, l'uscita del circuito diritenuta si mantiene al valore V raggiunto.

Il primo circuito di ritenuta della figura 6.24 somma una tensione di riferimento VR all'uscitaV02 del secondo circuito di ritenuta e moltiplica tale somma per un fattore 1/2. Il secondo circuito diritenuta ha un solo ingresso, al quale e' applicata la tensione V01. Il suo fattore di amplificazione e'unitario e quindi V02 e' uguale in ampiezza a V01.

+V

X

f

T

f

T

S S C

2R

2R

R

S/H

R R S C

S/HV V

S

T

C

V0

02

2

2 24

01

1

131

SB

R

c

i

c

i

G1G2

fig. 6.24

-+

I due circuiti di ritenuta sono connessi ad anello e i due interruttori S3 e S4 vengono azionatialternativamente, uno nella prima meta' del periodo di clock, l'altro nella seconda meta', in modoche quando V01 varia V02 rimane costante e viceversa.

Il segnale digitale di ingresso XSB aziona direttamente l'interruttore S1 in modo che incorrispondenza agli 1 logici del segnale di ingresso la tensione applicata al primo Sample-Hold siapari a VR.

Poiche' l'interruttore S3 e' chiuso durante la prima meta' del periodo di clock Ti, la tensione diuscita e':

Capitolo VIConversione A/D e D/A

239

( )Ri0201 V.aV.21V +=

avendo indicato con ai il valore del bit della parola di ingresso presente al tempo i. La variazionerispetto al valore precedente avviene con una costante di tempo RC, dove R e C sono i valori diresistenza e capacita' inseriti sul ramo di reazione dell'amplificatore operazionale.

Durante la seconda meta' di Ti la tensione V01 e' trasferita al secondo circuito Sample-Holdcon la chiusura dell'interruttore S4 e la tensione V02 diventa uguale a V01. Si completa cosi’ unciclo operativo. Le operazioni durante tutti gli altri cicli si susseguono identiche facendo si' chel'uscita del convertitore alla fine dell'intera parola di ingresso sia proporzionale al valore darappresentato da quest’ultima.

In fig. 6.25 e' riportato l'andamento delle tensioni nei vari punti del circuito in corrispondenzaall'ingresso seriale 000000101011. Il formato di parola dura pertanto 12 periodi di clock, da T1 aT12; ciascun periodo viene poi considerato diviso in due parti, Ti e iT .

Si suppone inoltre che esista un impulso di reset (sincronizzazione), sempre nullo eccetto cheal tempo T13 e che il tempo necessario a caricare i condensatori dei circuiti S/H sia piccolo inrapporto a Ti. Si tenga infine presente che l'interruttore S3 e' chiuso durante il semiperiodo Ti,mentre S4 e' chiuso durante il semiperiodo iT .

Il circuito di un convertitore seriale Sample-Hold consiste di quattro interruttori analogici, treamplificatori operazionali, due gate AND a due ingressi ed alcuni componenti discreti.

I due interruttori S3 e S4 connessi ai circuiti di Sample-Hold devono avere una capacita'ingresso-uscita la piu' piccola possibile, poiche' operano direttamente alla giunzione sommadell'operazionale; in caso contrario l'energia che attraverso essi si trasferisce durante le operazioni dicommutazione potrebbe caricare erroneamente le due capacita' di memorizzazione C1 e C2.

Nell’applicazione presa in esame, come in molte altre in cui siano usati circuiti di ritenuta, sirichiede che l'uscita segua l'ingresso con l'errore massimo di un millivolt. Di conseguenza percaricare correttamente il condensatore di ingresso e' necessario che il periodo di clock sia parialmeno a nove costanti di tempo. In altre parole, se si volesse un periodo di clock di 10 µsec. la co-stante di tempo di carica del condensatore dovrebbe essere dell'ordine del microsecondo. Sonoquindi imposte delle specifiche abbastanza pesanti ai valori di resistenza e capacita' e inoltre anchelo slew rate degli amplificatori operazionali dev'essere di buon valore.

Ad esempio, con una costante di tempo di carica di 1 microsecondo, con R = 10 kΩ e C = 100pF, l'amplificatore deve avere una velocita' di salita di 6 V/µsec. e tale specifica e' abbastanzapesante per un buon numero di amplificatori operazionali monolitici. A cio' si aggiunge che se ilvalore assunto per R appare ragionevole quello di C e' troppo basso.

Di conseguenza si deve il piu' delle volte giungere ad un compromesso e la soluzione piu'semplice e' quella di ridurre la velocita'. A titolo di esempio, se si scegliesse un periodo di clock di50 µsec. valori ragionevoli per il circuito Sample-Hold potrebbero essere R = 10 kiloohm, C = 500picofarad e slew-rate di 1.2 V/µsec.

Un importante vantaggio del convertitore Sample-Hold rispetto a quello Shannon-Rack e' chele sue prestazioni, entro larghi limiti, non dipendono ne' dalla precisione, ne' dalla stabilita' deicondensatori. E' questo un fattore molto importante in quanto, come gia' e' stato detto, condensatoridi elevata precisione e stabilita' sono difficili da realizzare e molto costosi.

Capitolo VIConversione A/D e D/A

240

f

T

X

V

V

t

t

c

13

SB

01

02

1 1 0 1 0 1 0 0 0 0 0 0

T T T T T T1 2 3 12 13 1

12 VR

34 VR

38 VR

1116 VR

1132 VR

4364 VR

43128 VR

43256 VR

43512 VR 43

1024 VR

12 VR

34 VR

3 VR8

fig. 6.25

Altro importante vantaggio si ha per il fatto che i tempi di commutazione degli interruttorianalogici non sono critici, poiche' essi al massimo limitano la velocita' operativa. Le prestazionistatiche e dinamiche del convertitore dipendono in pratica solo dalle prestazioni del circuitoSample-Hold usato.

E' ragionevole pensare che la precisione del circuito illustrato schematicamente in fig. 6.24 siaalmeno dello 0.1% del fondo scala ad una frequenza di clock di 10 kHz. La risoluzione puo'raggiungere qualsivoglia valore, semplicemente variando la temporizzazione del segnale di resetT13.

Con una frequenza di clock di 10 kHz il tempo di conversione per parole binarie da 12 bit e' di1.2 msec. E' ovvio tuttavia che sulla base delle caratteristiche di componenti piu' moderni si possonoottenere delle precisioni e delle velocita' operative considerevolmente piu' alte.

6.5.3) Il convertitore seriale ciclico.

Un ulteriore tipo di convertitore D/A seriale, che evita tutti gli inconvenienti del convertitoreShannon-Rack e' quello ciclico. Esso differisce da quello Sample-Hold in quanto usa solo dueamplificatori operazionale e alcune resistenze di precisione; e' tuttavia necessario un numeromaggiore di interruttori analogici. Uno dei suoi pregi risiede nel fatto che e' notevolmente piu'veloce che non quello Sample-Hold.

Il convertitore ciclico, illustrato in fig. 6.26, usa due interruttori S1 e S2 per collegarel'ingresso di un amplificatore A1 ad una tensione di riferimento o a terra.

Capitolo VIConversione A/D e D/A

241

V

X

X

S

S

R

R

AV

T

S

C

S

C

S

C

S

S

T

f f

SB

R

SB

2

1

1k

12

3

c

4

st

A

5

B

7

8

1

c

f cfc

V0

fig. 6.26