Amplificatori CMOS

Transcript of Amplificatori CMOS

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 1/64

I

MICROELETTRONICA

Prof. Mario Bertolaccini

AMPLIFICATORI

CMOS

A.A. 2006/07

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 2/64

AMPLIFICATORI CMOS

II

INDICE

1 GENERALITA’

1.1 CATEGORIE DI AMPLIFICATORI CMOS

1.2 RELAZIONI E PARAMETRI FONDAMENTALI DEI TRANSISTORI

MOSFET A CONFRONTO CON I TRANSISTORI BJT

2 TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

2.1 CIRCUITI DI POLARIZZAZIONE DIRETTAMENTE DERIVATI DALLE

TENSIONI DI ALIMENTAZIONE.

2.2 CIRCUITI DI POLARIZZAZIONE CON PICCOLA DIPENDENZA DALLE

TENSIONI DI ALIMENTAZIONE.

2.3 GENERATORI DI CORRENTE

3 AMPLIFICATORI CMOS A TRANSCONDUTTANZA (OTA) “ON CHIP”

3.1 AMPLIFICATORI MONOSTADIO

3.2 AMPLIFICATORI A DUE STADI

3.3 LA COMPENSAZIONE IN FREQUENZA

4 AMPLIFICATORI OPERAZIONALI CMOS (OPA) “STAND ALONE”

5 AMPLIFICATORI OPERAZIONALI CMOS COMPLETAMENTE

DIFFERENZIALI (“FULLY DIFFERENTIAL”

5.1 CARATTERISTICHE GENERALI DEGLI AMPLIFICATORI

COMPLETAMENTE DIFFERENZIALI

5.2 UN ESEMPIO MOLTO SEMPLICE DI AMPLIFICATORE

5.3 RETI CMF A TEMPO CONTINUO

5.4 RETI CMF A TEMPO DISCRETO (A CAPACITA’ COMMUTATE)

5.5 ESEMPI DI AMPLIFICATORI COMPLETAMENTE DIFFERENZIALI

BIBLIOGRAFIA

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 3/64

AMPLIFICATORI CMOS

1

Cap.1

GENERALITA’

1.1 CATEGORIE di AMPLIFICATORI CMOSSi possono distinguere due categorie di amplificatori CMOS:

a) amplificatori singoli “general purpose” (amplificatori “stand-alone”);o sorgenti e carichi non definiti (ad esempio carichi capacitivi sino a qualche centinaio

di pF e resistivi sino a meno di 1 kΩ)b) amplificatori all’interno di sistemi di maggiori dimensioni e con funzioni assai più ampie,

solitamente in grande prevalenza digitalio sorgenti e carichi definiti, salvo, a volte, quando un amplificatore deve ricevere

dall’esterno o inviare all’esterno (“off-chip”) un segnale; quest’ultima situazione ècomunque poco frequente e si tratta in genere di “buffer” di uscita

Ci occupiamo qui quasi esclusivamente della seconda categoria, trattandosi di quella assaipiù ampiamente rappresentata. In questo caso sono usualmente rilassate alcune specifiche propriedegli amplificatori della categoria a). Ad esempio: guadagno in continua, che può essere spessoanche assai minore; offset, che può essere a volte significativamente maggiore; CMRR; level shiftaccurato; ecc.

Si tratta quasi esclusivamente di amplificatori a transconduttanza (OTA) in quanto destinatia pilotare carichi capacitivi e cioè capacità (ad esempio sistemi a capacità commutate) o altrestrutture CMOS.

Le categorie più utilizzate sono semplici amplificatori a transconduttanza con uscita singleended e amplificatori completamente differenziali, cioè con uscita differenziale.

Essendo tali strutture condizionate, per quanto riguarda l’alimentazione, dal sistema digitale

in cui sono inserite esse sono prevalentemente a singola alimentazione, anche se possono darsi casidi doppia alimentazione. Per lo stesso motivo è inoltre di particolare interesse il caso di bassetensioni di alimentazione, dell’ordine di 3 V (3,3 V) o inferiori.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 4/64

GENERALITA’

2

1.2 MOSFET A CONFRONTO CON BJT

BJTFunzione di trasferimento

esponenziale / (1 ) BE T V V

C S CE I I e V λ = +

Cattivacomplementaritànella tecnologia

base

Transconduttanza di piccolo segnale proporzionale alla corrente di lavoro C

m

T

I g

V =

Conduttanza di collettore (“di uscita”) di piccolo segnale

circa proporzionale alla corrente di lavoro1

1C A C

o C C

o CE A A CE A

I V I g I I

r V V V V V

λ λ

λ = = = =

+ +;

VA tensione di Early dell’ordine del centinaio di volt1

AV λ =

Fattore di guadagno, in continua, (guadagno a vuoto) dell’ordine delle migliaia(in genere assai maggiore del guadagno sotto carico)indipendente dalla corrente di lavoro e dalla fondamentale caratteristica

geometrica del dispositivo controllabile in fase di progetto (area di emettitore)1

m CE A CE A A m o

o T T T

g V V V V g r

g V V V

λ µ

λ

+ += = = = ;

Tensione termica

T

kT V

q= k=1,38 10-23 J/K costante di Boltzmann

q=1,6 10-19 C carica dell’elettrone

per T=300 K VT=26 mV

MOS

Buonacomplementarità

Regione di saturazione: GS t V V > DS GS t V V V > −

funzione di trasferimento quadratica:2( ) (1 ) D GS t DS

I k V V V λ = − + 1

'2 ox

W W k C k

L L µ = =

Regione ohmica: GS t V V > DS GS t V V V < − funzione di trasferimento:

12 ' ( )

2 D GS t DS DS

W I k V V V V

L= − −

quasi lineare per DS GS t V V V << −

Transconduttanza di piccolo segnale.

Proporzionale alla radice della corrente di lavoro o alla corrente di lavoro aseconda del parametro di controllo utilizzato (rapporto di forma o tensione di

overdrive)

2 ( )(1 ) 2 ' 1

2

Dm GS T DS D DS

GS

W I g k V V V k I V V V L

λ λ = − + = + =−

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 5/64

AMPLIFICATORI CMOS

3

Conduttanza di collettore (“di uscita”) di piccolo segnalecirca proporzionale alla corrente di lavoro

11

D A Do D D

o DS A A DS A

I V I g I I

r V V V V V

λ λ

λ = = = =

+ +;

tensione di Early VA dell’ordine delle decine di volt; cresce al crescere deldrogaggio del substrato e di L

1L

DS

A eff

dX dV

V Lλ = =

eff L L L X = −

XL lunghezza di modulazione del canaleFattore di guadagno (guadagno a vuoto, in continua) compreso tra le decine e

le centinaiainversamente proporzionale alla radice della corrente di lavoro

proporzionale alla radice del prodotto WL (dimensioni del dispositivo)Uno scaling a campo costante, cioè variando proporzionalmente allo stessomodo le dimensioni del dispositivo e le tensioni applicate non varia µΑ. Uno

scaling a tensione costante, cioè variando solo le dimensioni del dispositivo,varia µΑ.

11 12 '

2 2

DS A A m o

GS t GS t D

V W V g r k

V V V V L I

λ µ

λ λ

+= = = =

− −

1 1 12 '

2

A L GS t L D

DS DS

Lk WL

dX V V dX I dV dV

µ =−

;

Effetto bulk Tensione di soglia in funzione della tensione VSΒ (source-bulk) per MOS a

canale n e a canale p rispettivamente

( )

( )

0

0

2 2

2 2

t t SB

t t SB

V V V

V V V

γ

γ

= + Φ + − Φ

= − Φ − − Φ

2SI sub

ox

qN

C

ε γ = ln sub

i

N kT

q nΦ =

Transconduttanza di bulk (canale n)12 2

mmb

SB

gg

V γ = −

Φ +

Controllo della corrente di drain in regime di piccolo segnale

d m gs o ds mb sbi g v g v g v= + +

L’effetto body si riduce al diminuire del drogaggio Nsub del substrato, ma cresce il parametro λ di modulazione della lunghezza di canale e quindi si riduce il guadagno massimo µΑ ottenibile.Inoltre una eccessiva riduzione della concentrazione di ioni droganti (circa < 1013 cm-3) un NMOSpuò comportarsi come un dispositivo a svuotamento e cioè come un JFET.

Nel caso di debole inversione (funzionamento sottosoglia, cioè per tensioni di overdrive inferioria qualche decina di mV per un NMOS), la caratteristica di trasferimento diviene esponenziale comein un transistore bipolare:

( ) / / 1 D DxT T GS DSV nV V V W

I I L

e e−

= −

dove IDx dipende dal processo tecnologico e n è compreso tra 1 e 2. Le correnti ottenibili sono

molto piccole essendo IDx dell’ordine di qualche decina di nA; il dispositivo risulta quindi dotato dif T molto bassa. Può essere usato in applicazioni a potenza molto bassa e a frequenze modeste.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 6/64

TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

4

Cap. 2

TECNICHE DI POLARIZZAZIONE NEGLI

AMPLIFICATORI CMOS

2.1 CIRCUITI DI POLARIZZAZIONE

2.1.1 CIRCUITI DIRETTAMENTE DERIVATI DALLE TENSIONI DI ALIMENTAZIONE.

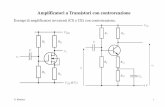

Nella figura 2.1 è rappresentato lo schema circuitale di un amplificatore a transconduttanza(OTA) particolarmente semplice. Si tratta di una struttura monostadio, differenziale, con carico aspecchio, destinata a pilotare direttamente un carico capacitivo e quindi di una soluzione applicabileon-chip ogni qual volta non siano richieste caratteristiche migliori, quali guadagno e slew rate piùelevati.

Tale soluzione verrà discussa dettagliatamente più avanti.

INM1 M2

M3

2I

IN

DDV

1

M4

M5

I1I1

Vbias

SSV

OUT

CL

Figura 2.1

Semplice amplificatore a transconduttanza CMOS a singolo stadio

Si noti che, ovviamente, è richiesto un circuito di polarizzazione atto a fissare la corrente dilavoro dello stadio, circuito che non è rappresentato nella figura, mentre è indicata la tensione dipolarizzazione Vbias da esso fornita.

Nell’ambito della tecnologia CMOS spesso le polarizzazioni si possono considerare intermini di tensioni anziché direttamente di correnti e i circuiti di polarizzazione possono essereconsiderati, spesso indifferentemente, quali generatori di tensione o di corrente. Con le struttureCMOS è infatti possibile generare facilmente delle tensioni ricorrendo solamente ai transistori senzautilizzare necessariamente resistori

Nella figura 2.2 è rappresentato un singolo transistore MOS nella connessione bipolare detta“a diodo”, che genera ai suoi capi una tensione

1 ' DS GS t t ov I V V V V V W k

L

= = + = + Vov tensione di overdrive

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 7/64

AMPLIFICATORI CMOS

5

(si è trascurato l’effetto Early, in questo caso di peso assai modesto, e si è consideratoassente l’effetto body)

E’ importante osservare che il transistore si trova sempre a lavorare in regione di saturazioneessendo rispettata la relazione VDS>VGS-Vt.

La relazione precedente può essere scritta nella forma equivalente

DS t V V V = + ∆

dove ∆V risulta controllabile attraverso il rapporto di forma

M1 V =DS

I

VGS

k' W/L

I1=Vt +

Figura 2.2

MOS in connessione a diodo

Quindi una disposizione in serie di MOS opportunamente dimensionati consente di ottenereun partitore di tensione a partire da una tensione di alimentazione.

M1

DDV

M2I

V1

V2

Mn

Mn+1I

Vn

I

Figura 2.3

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 8/64

TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

6

Partitore di tensione MOS Un esempio generalizzato è riportato nella figura 2.3, dove si mette anche in evidenza come

strutture di questo tipo siano fortemente influenzate dall’effetto body: pur utilizzando transistorinominalmente identici essi risultano caratterizzati da tensioni di soglia effettive diverse.

La relazione caratterizzante il partitore si basa ovviamente sulla disposizione in serie equindi sulla condizione di eguaglianza delle correnti che percorrono i MOS:

( ) ( ) ( )2 221 1 2 1 2 1

1 2 1

' ' 't t DD n tn

n

W W W k V V k V V V k V V V L L L

+

+

− = − − = ⋅⋅ ⋅ ⋅ ⋅⋅ = − −

Nota la sequenza V1 – Vn che si vuole realizzare e fissata la corrente di lavoro (in base acriteri quali dissipazione e occupazione di area), si determinano le varie tensioni di soglia e quindi irapporti di forma necessari. La dipendenza delle tensioni di soglia di tutti i transistori al di sopradel primo dall’effetto body aggiunge notevole dispersione nel risultato.

Ovviamente la stessa struttura può essere realizzata ricorrendo a dispositivi a canale P e,parimenti, tutte le strutture mostrate nel seguito possono essere tradotte nella loro formacomplementare.

Le strutture del tipo considerato, utilizzate per produrre tensioni di polarizzazione, sono

realizzabili con numerose varianti, soprattutto in dipendenza dalle configurazioni degli amplificatoria cui devono essere associate. Nella figura 2.4 è rappresentata una soluzione atta a produrre unatensione determinata in base alle relazioni

( ) ( )2 2' '

ref N bias tN P DD bias tP

N P

W W I k V V k V V V

L L

= − = − −

( )'

1 ref

bias SS tN

N N

I V V V

W k L

− = +

DDV

SSV

I

Vbias

ref

M1

M2

Figura 2.4

Altro esempio di partitore di tensione MOS

Questo semplice circuito di generazione di una tensione di polarizzazione può essereassociato con vantaggio ad esempio all’amplificatore della figura 2.1. Tale associazione è riportatanella figura 2.5 che quindi mostra una struttura elementare OTA completa.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 9/64

AMPLIFICATORI CMOS

7

I transistori M5 e M6 verranno necessariamente dimensionati in base alla condizione

( )( )

15

6

2

ref

W I L

W I L

=

e, nel caso di buon matching dei parametri tecnologici di M6 e M5 (tra cui anche λ, peraltro

solitamente caratterizzato da dispersione non trascurabile)5 6 6 5 DS DS GS GSV V V V = = =

Quindi M5 rimane in saturazione anche al variare (entro limiti ragionevoli) delle tensioni dialimentazione e le condizioni di lavoro del circuito risultano sostanzialmente stabili anche secorrenti e tensioni sono sensibili alle tensioni di alimentazione. Inoltre l’effetto Early noninterviene, almeno in prima approssimazione, nel dimensionamento di M5 e M6.

INM1 M2

M3

2I

IN

DDV

1

M4

M5

I1I1

Vbias

SSV

OUT

I

M6

M7

ref

Figura 2.5

Esempio di polarizzazione di un OTA tramite un partitore di tensione MOS

Nel circuito considerato, se realizzato in p-well, non interviene l’effetto body. Il circuito dipolarizzazione considerato è peraltro utilizzabile senza dover ricorrere a transistori di dimensionieccessive (M7, la cui VGS è pari alla totale tensione di alimentazione -VGS5) purché le tensioni dialimentazione non siano troppo elevate e può quindi presentare problemi di dimensionamento.

Alcune soluzioni circuitali per realizzare generatori di tensioni di polarizzazione nonescludono l’uso di veri e propri resistori.2.1 Un esempio è mostrato nella figura 2.6.

2. 1 In tecnologia CMOS si possono realizzare resistori per diffusione, in polisilicio e in well. Resistori diffusi si ottengonoutilizzando le diffusioni utilizzate per realizzare le regioni di source e di drain; si ottengono così resistori con proprietà simili a

quelle dei resistori in tecnologia bipolare, ma di basso valore considerata la bassa resistenza di strato (qualche decina diΩ /quadro). Resistori in polisilicio si possono derivare dallo strato utilizzato nelle tecnologie con gate in polisilicio e anche inquesto caso la resistenza di strato risulta bassa (qualche decina di Ω /quadro) e piuttosto dispersa. Le regioni di well possono essereutilizzate per realizzare resistori; la resistenza di strato risulta assai elevata, ma è caratterizzata da forte dispersione, elevatocoefficiente di temperatura e spiccata dipendenza dalla tensione.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 10/64

TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

8

Anche in questo caso ambedue i dispositivi utilizzati si trovano necessariamente insaturazione e non vi è effetto body. Ovviamente

1 1GSV V = 2 2 DD GSV V V = −

e in virtù della disposizione in serie si può scrivere la relazione

( ) ( ) ( ) ( )( )2 2' ' 2 1

1 1 2 2

1 2

1 1ref N tN N P tP P

V V W W I k V V V k V V V

L L R

λ λ −

= − + = − + =

Noti i valori V1 e V2 desiderati si fissa un valore ragionevole di Iref (sostanzialmente in basea considerazioni di dissipazione e di occupazione di area) e si deducono i valori di W/L deidispositivi e di R, utilizzando eventualmente una procedura “cut and trial”.

M2

M1

DDV

SSV

V1

Iref

R

V2

Figura 2.6

Altro esempio di partitore di tensione MOS utilizzante un resistore

Tutte le strutture sinora considerate producono riferimenti di polarizzazione più o menofortemente dipendenti dalla tensione di alimentazione. Gli amplificatori on-chip sono destinati,salvo casi molto particolari, ad operare con tensioni di alimentazione nominalmente prefissate, mala reiezione dei disturbi associati alle alimentazioni (PSR) richiede in primo luogo che tali disturbinon possano sensibilmente alterare, in transitorio,le condizioni di polarizzazione; inoltre, in caso didispersione non trascurabile delle tensioni di alimentazione, si richiede spesso una buonariproducibilità e stabilità delle condizioni di polarizzazione. E’ quindi importante poter ricorrere a

circuiti di polarizzazione che forniscano tensioni e correnti il più possibile indipendenti dallealimentazioni utilizzate.

2.1.2 CIRCUITI CON PICCOLA DIPENDENZA DALLE TENSIONI DI

ALIMENTAZIONE.

Una particolare categoria di circuiti di polarizzazione, generatori di corrente e/o di tensioneè costituita dalle strutture cosiddette “autoalimentate” il cui funzionamento, come è noto, si basasulla presenza di una retroazione positiva interna che consente lo stabilirsi a regime di unacondizione di polarizzazione in linea di principio indipendente dalle tensioni di alimentazioneutilizzate. La corrente di lavoro viene prodotta utilizzando un opportuno riferimento di tensione

In genere si cerca peraltro di evitare l’uso di resistori veri e propri in quanto la struttura MOS può fungere da transistore (elementoattivo), da condensatore e, in regione ohmica, da resistore. Un MOS polarizzato in regione ohmica consente di ottenere resistoricon resistenza controllabile tramite la polarizzazione gate-source e di valore anche elevato, ma è caratterizzato da scarsa linearità.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 11/64

AMPLIFICATORI CMOS

9

interno: in genere si tratta della VGS di un MOS,oppure della VBE di un BJT oppure della ∆VBE diuna coppia di BJT (cioè della tensione termica VT).

Nella figura 2.7 è riportato un circuito che utilizza la VGS di un MOS per produrre lacorrente di polarizzazione tramite un resistore di opportuno valore.

I transistori M1 e M2 costituiscono uno specchio che impone un determinato rapporto dicorrenti nei due rami, ad esempio 1:

bias ref I I = I transistori M3 e M4 possono essere accoppiati in modo da avere la medesima VGS, ad

esempio, nel caso di fattore di specchio M1, M2 unitario, imponendo

3 4

W W

L L

=

In questa maniera si impone al resistore R la tensione VGS del transistore M5 e si ottienequindi la corrente

( )'

55

ref

t

PGS

bias

I V

W k V L

I R R

+

= =

M3

M1

M4

DDV

M2

R

M5

Iref Ibias

I bias

k' W/L

I1=R V +t

I ref = γ Ibias

VGS=

M6

Ibias

ref

Figura 2.7

Circuito di polarizzazione autoalimentato utilizzante come riferimento la tensione V GS di un MOS

Tale corrente viene prelevata tramite il transistore M6 pilotato da M2.Se nella relazione precedente, lavorando a bassa corrente e dimensionando il transistore M5

con W/L grande, si rende trascurabile rispetto a Vt il termine sotto radice (cioè la tensione dioverdrive), si ottiene un circuito riferito alla tensione di soglia. Ciò è peraltro possibile solamente in

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 12/64

TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

10

prima approssimazione in quanto una diminuzione eccessiva della tensione di overdrive porterebbeM5 sottosoglia.

Le relazioni precedenti – uguaglianza delle correnti imposta dallo specchio e legamequadratico tra le correnti stesse determinato dalla conversione della tensione VGS5 – evidenzianol’intervento di una retroazione positiva (non divergente) e mostrano che il sistema è caratterizzatoda due possibili punti di lavoro di cui il primo corrispondente a Ibias=0 instabile in linea di principio,

ma solitamente non di fatto. Infatti in fase di avvio (applicazione dell’alimentazione) il guadagnointerno della struttura è troppo piccolo, causa lo stato di non conduzione o insufficientepolarizzazione dei dispositivi, e non consente di raggiungere il punto di lavoro corrispondente a Ibias

diverso da zero. E’ dunque a volte necessario un circuito di “startup” che conduca inizialmente ilcircuito a raggiungere la condizione stabile di regime, ma risulti escluso in tale condizione.

Nell’analisi è stato trascurato l’effetto Early che istituisce un “collegamento diretto” con latensione di alimentazione e quindi introduce una certa dipendenza dall’alimentazione stessa dellacorrente prodotta.

Il circuito soffre inoltre di dipendenza dalla temperatura spesso non trascurabile. Ilcoefficiente di temperatura della corrente prodotta si può esprimere come

5

5

1 1 1bias GS

T

bias GS

I V R

I T V T R T

δ δ δ

δ δ δ Γ = = − e, dato che il coefficiente di temperatura di VGS è negativo (compreso tipicamente tra -1 e -2

mV/°C) mentre quello del resistore è solitamente positivo2.2, di fatto i due termini non si possonocompensare, ma si sommano.

Del circuito riportato nella figura 2.7 sono possibili diverse varianti, ad esempio quellariportata nella figura 2.8

M3

M1

M4

DDV

M2

R

Iref

Ibias

M6

Ibias

Figura 2.8

Variante del circuito della figura 2.7

2.2 Possono avere coefficiente di temperatura negativo resistori ad impiantazione ionica o a film sottile.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 13/64

AMPLIFICATORI CMOS

11

Lo specchio M1, M2 impone anche in questo caso un certo rapporto, ad esempio 1, tra lecorrenti nei due rami e lo specchio Widlar M3, M4, R legge la tensione VGS3 in termini di correnteattraverso il convertitore resistivo R. La struttura si comporta come la precedente, ma il matchingtra M1 e M2 è peggiorato in quanto la caduta di tensione ai capi dei due transistori è diversa equindi la relazione tra le correnti nei due rami imposta dallo specchio risulta influenzata dall’effettoEarly e maggiormente dispersa.

Come riferimento di tensione interno al circuito autoalimentato può essere utilizzata lacaduta ai capi della giunzione base-emettitore di un transistore bipolare.2.3

J1

DDV

R

M3

M1

M4

M2

Iref Ibias

I biaskT I

ln=Rq IS

I ref = γ Ibias

VBE=

M5

Ibias

ref

Figura 2.9

Circuito di polarizzazione autoalimentato utilizzante come riferimento la tensione V BE di un BJT

Il circuito si comporta come quello della figura 2.7, ma la corrente risulta proporzionale allaV BE del transistore bipolare J1

1

1

ln ref BE T bias

S

I V V I R R I

= =

2 .3 Nell’ambito della normale tecnologia CMOS possono essere realizzati transistori bipolari verticali sfruttando uno well, ilsubstrato e la giunzione tra la diffusione di source (o di drain) o lo well: a partire da uno p-well si ottiene un transistore n-p-n; apartire da uno n-well si ottiene un transistore p-n-p. Il substrato costituisce il collettore che quindi risulta sempre collegato a unadelle alimentazioni (l’alimentazione negativa nel caso di substrato p e quindi di transistore p-n-p; l’alimentazione positiva nel casodi substrato n e quindi di transistore n-p-n); la base è costituita dallo well, l’emettitore dalla diffusione source/drain. Il transistoresi comporta quindi come un p-n-p di substrato della tecnologia bipolare di base: buona capacità di corrente, basso guadagno,cattiva risposta in frequenza.

Naturalmente tecnologie CMOS più avanzate sono in grado di produrre BJT di entrambe le polarità senza utilizzare il substratocome collettore e quindi fornendo dispositivi bipolari liberamente utilizzabili. Si tratta delle tecnologie BiCMOS. I transistoribipolari sono realizzati in un processo a bassa tensione con drogaggio di collettore un ordine di grandezza più elevato che neiprocessi bipolari ad alta tensione, isolamento dielettrico, dimensioni, soprattutto verticali, assai ridotte, impiantazione ionica,caratteristiche tutte che bene si sposano con quelle di un processo CMOS avanzato.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 14/64

TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

12

Anche dal punto di vista della dipendenza dalla temperatura il comportamento risulta deltutto analogo a quello del circuito in cui viene utilizzata la VGS di un MOS: il coefficiente ditemperatura infatti è dato da

1

1

1 1 1bias BE T

bias BE

I V R

I T V T R T

δ δ δ

δ δ δ Γ = = −

e, dato che il coefficiente di temperatura di VGS è negativo (attorno a -2 mV/°C) mentrequello del resistore è solitamente positivo, di fatto i due termini si sommano.

Una soluzione circuitale che utilizza come riferimento di tensione la tensione termicaVT=kT/q è riportata nella figura 2.10.

J1 J2

DDV

R

xm

Iref Ibias

I ref = γ Ibias

M3

M1

M4

M2

IbiaskT

mln=Rq

VBE=∆

M5

Ibias

Figura 2.10

Circuito di polarizzazione autoalimentato utilizzante come riferimento la tensione termica V T

La parte inferiore della struttura è identica in termini di architettura e dimensionamento a

quella dei circuiti delle figure 2.7 e 2.9 e quindibias ref

I I =

e 3 4GS GSV V = I transistori J1 e J2 confrontano le loro VBE ed, essendo l’area di emettitore di J2 pari a m

volte quella dell’emettitore di J1 si ottiene

1 2 ln BE BE BE T V V V V m∆ = − = e quindi

ln 1lnT

bias

V m kT I m

R q R= =

Il coefficiente di temperatura è

1 1 1 1 1bias T T

bias T

I V R R

I T V T R T T R T

δ δ δ δ

δ δ δ δ Γ = = − = −

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 15/64

AMPLIFICATORI CMOS

13

I due coefficienti sono ora dello stesso segno (positivi) e quindi si sottraggono per cui unascelta opportuna del tipo di resistore produce una corrente molto meno dipendente dalla temperaturache non quella prodotta dai circuiti precedenti. In realtà la scelta del valore e della natura di R, inconnessione con la scelta di m, è spesso condizionata anche da un criterio di minimizzazionedell’area occupata da R stesso, da J1 e da J2.

In tutti i circuiti del tipo di quelli esaminati le principali fonti di errore e dispersione sonocostituite da:- l’imperfetto accoppiamento dei dispositivi; nel caso delle strutture considerate nelle figure

2.7, 2.9, 2.10 l’accoppiamento tra M1 e M2, e tra M3 e M4- l’effetto Early che può influenzare la relazione tra le correnti nei due rami e che comunque,

come già notato, determina accoppiamento con l’alimentazione- l’eventuale effetto body

Per quanto riguarda il primo punto, particolare cura deve essere usata per ottenere un buonaccoppiamento; dal punto di vista geometrico producono migliori risultati dispositivi di dimensioninon troppo piccole ed è importante utilizzare opportune tecniche di layout (ad esempio disposizionia centroide comune).

L’effetto Early può essere sensibilmente ridotto utilizzando strutture cascode. Ad esempio ilcircuito della figura 2.10 può essere modificato come nella figura 2.11, sostituendo i transistori M1,M2, M3, M4 con le relative configurazioni cascode. Questa soluzione consente di ottenere una

J1 J2

DDV

R

xm

Iref Ibias

M1 M2

M3 M4

M3 M4

M1 M2

M5

M5

Ibias

1 1

1

1 1

2

2

22

2

Figura 2.11

Il circuito della figura 2.10 modificato tramite l’introduzione di strutture cascode.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 16/64

TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

14

dipendenza di Ibias dalla tensione di alimentazione molto piccola, ma presenta una dinamicadi uscita in tensione considerevolmente ridotta causa le ulteriori cadute di tensione introdotte daitrasferitori di corrente e non è quindi utilizzabile in sistemi a bassa tensione di alimentazione (adesempio VDD=3,3 V). Inoltre l’aggiunta di dispositivi “floating” rispetto a well e substrato introduceinevitabilmente effetto body.

2.1.3 GENERATORI DI CORRENTE La più semplice realizzazione di un generatore di corrente pilotato a specchio è

rappresentata nella figura 2.12.La relazione tra la corrente Ibias e la corrente di riferimento Iref , cioè il fattore di specchio, si

può ovviamente scrivere

( )( )

11

22

1

1bias DS

ref DS

W I V L

W I V L

λ γ

λ

+= =

+

M1

DDV

M2

Iref

Ibias

Figura 2.12

Semplice generatore di corrente a specchio

La dinamica di tensione in uscita è determinata dal limite di saturazione Vsat del transistoreM2 e quindi, trascurando l’effetto Early

( )2 2'

2

bias DD out sat ov

I V V V V

W k L

> > = =

Il transistore M2 andrebbe quindi dimensionato in modo da ridurre il più possibile la suatensione di overdrive.

La resistenza di uscita è semplicemente ro, cioè quella di drain di un MOS e non risultaquindi particolarmente elevata.

L’accoppiamento tra i transistori risulta evidentemente critico per ottenere buona precisione

e riproducibilità e l’effetto Early contribuisce negativamente da questo punto di vista in quanto ingenerale la tensione ai capi dei due transistori risulta diversa.La resistenza di uscita può essere aumentata utilizzando una struttura retroazionata o

configurazioni cascode. Il primo approccio conduce alla ben nota configurazione Wilson

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 17/64

AMPLIFICATORI CMOS

15

ampiamente utilizzata in tecnologia bipolare. Va peraltro notato che nel caso dei transistori bipolarila struttura Wilson è utilizzata anche, e spesso, soprattutto per ridurre l’errore sistematico dispecchio connesso con la presenza delle correnti di base; non è ovviamente questo il caso intecnologia CMOS. Essendo lo specchio Wilson retroazionato la resistenza di uscita vienemodificata in termini del guadagno d’anello che, purché il fattore di guadagnoµA dei transistori siagrande rispetto ad 1, in prima e buona approssimazione vale appunto µA (si è fatta l’ipotesi che i

transistori abbiano tutti lo stesso rapporto di forma e che il generatore Iref non carichiapprezzabilmente la struttura). Perciò la resistenza di uscita è sostanzialmente data da

3 3out m o o A or g r r r µ = ⋅ =

M1

M3

DDV

M2

Ibias

Iref

Figura 2.13

Specchio Wilson

Essendo µA compreso tipicamente tra qualche decina e qualche centinaio la resistenza diuscita risulta considerevolmente più elevata che nel caso dello specchio semplice.

Peraltro lo specchio Wilson soffre principalmente di due inconvenienti: la dinamica di uscitarisulta considerevolmente ridotta rispetto a quella dello specchio semplice e la precisione eriproducibilità sono alquanto modeste in quanto i transistori M1 e M2 hanno diversa tensione aicapi e gioca quindi l’effetto Early. Questi inconvenienti sono assai più gravi che in tecnologiabipolare in quanto le cadute residue nei MOS (tensione di saturazione) sono significativamentemaggiori di quelle dei bipolari 2.4 e le tensioni di Early possono essere anche molto minori. Inoltrele tensioni di alimentazione sono normalmente sensibilmente più basse.

2.4 Ovviamente il significato di “saturazione” è completamente diverso nei due casi. Qui e nel seguito con Vsat si indicala tensione che nominalmente separa la regione ohmica da quella di saturazione, cioè la tensione minima che deveessere presente ai capi del dispositivo MOS perché esso operi nella regione di saturazione. Tale tensione coincide con la

tensione di overdrive Vov=VGS-Vt e costituisce un limite da cui è in pratica necessario discostarsi alquanto per garantireil funzionamento in saturazione: infatti la transizione tra le due regioni non è netto, ma piuttosto graduale. Per canale“ultracorto” l’effetto della saturazione della velocità dei portatori comporta uno scostamento dalla caratteristicaquadratica che tende ad essere linearizzata.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 18/64

TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

16

La dinamica della tensione di uscita è limitata (inferiormente, nella figura) dall’entrata inregione ohmica di M3 per cui la caduta residua risulta data da

2 3GS sat V V + cioè, nel caso che i transistori abbiano tutti lo stesso rapporto di forma

2 sat t V V + da confrontare con quella dello specchio semplice pari soltanto a V

sat. Ad esempio per una

tensione di overdrive di 180 mV e Vt =0,9 V nello specchio semplice la caduta residua risulta pari a0,18 V, mentre nello specchio Wilson è 1,26 V e quindi scarsamente compatibile con bassealimentazioni.

Si noti che una buona dinamica di tensione in uscita è importante soprattutto nel caso che igeneratori di corrente vengano utilizzati come carichi attivi.

Il peso dell’effetto Early nel condizionare l’accoppiamenti tra i transistori M1 e M2 puòessere ridotto aggiungendo alla struttura un transistore di level shift per simmetrizzarla, comemostrato nella figura 2.14.

In ogni caso deve essere attentamente curato l’accoppiamento tra gli elementi attivi, inparticolare tra M1 e M2, M3 e M4

M1

M3

DDV

M2

Ibias

Iref

M4

Figura 2.14

Specchio Wilson simmetrizzato

Una struttura molto usata in tecnologia CMOS è quella del generatore di corrente cascodeche può essere derivato direttamente dallo specchio semplice M1-M2 aggiungendo due transistoriM3 e M4 a costituire strutture cascode su ciascun ramo. La configurazione che così si ottiene èrappresentata nella figura 2.15.

Tale configurazione è intrinsecamente simmetrica nel caso di buon accoppiamento dellecoppie M1-M2 e M3-M4, presenta una resistenza di uscita elevata - dello stesso ordine di quelladello specchio Wilson e cioè µAro – ma è caratterizzata da una caduta residua in uscita anch’essapari a quella dello specchio Wilson 2V

sat+V

t.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 19/64

AMPLIFICATORI CMOS

17

M1

M3

DDV

M2

Ibias

Iref

M4

Figura 2.15

Specchio cascode L’andamento della corrente in funzione della tensione all’uscita dello specchio cascode è

mostrato nella figura 2.16. Nelle valutazione fatte e nella figura è stato trascurato l’effetto Early.

Vout

Ibias

2Vsat +Vt2Vsat

M2 e M4 ambedue in saturazione

M2 in saturazione e M4 in regione ohmica

M2 e M4 ambedue in regione ohmica

Figura 2.16

Corrente in funzione della tensione all’uscita dello specchio cascode

E’ possibile ridurre tale caduta e quindi migliorare nettamente la dinamica di uscita delcircuito modificando in modo semplice la struttura tramite l’introduzione di una traslazione dilivello che costringa il transistore M2 ad avere ai suoi capi una tensione pari a V

satinvece che V

GS.

La soluzione usualmente utilizzata è riportata nella figura 2.17.Nella figura si riconoscono i transistori M1-M4 della configurazione cascode originaria. Tra

i transitori M3 e M4 è ora interposto il transistore M5 (alimentato dal transistore M6 e quindi in

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 20/64

TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

18

configurazione follower) che introduce una traslazione di livello pari alla sua VGS5. Tra il suo gate eil drain del transistore M2 si ha quindi una caduta pari a

2 GSV e quindi per portare la tensione ai capi di M2 ad essere pari a

sat GS t V V V = − è necessario portare il gate di M3 e M5 a

2 3 3 2GS sat GS t sat t

V V V V V V + = − = + Dunque il transistore M3 deve essere dimensionato in modo che la sua tensione VGS3 sia pari

a

3 2 2GS GS t sat t V V V V V = − = +

cioè in modo che abbia una tensione di overdrive

3 2( )GS t GS t V V V V − = −

doppia della tensione di overdrive degli altri transistori.Ciò, considerata la relazione quadratica tra corrente e tensione di overdrive, si ottiene

riducendo il rapporto di forma di M3, rispetto a quello degli altri transistori, di un fattore 22=4.

M1

M3

DDV

M6

Iref

M5

M2

Ibias

M4

W/L W/L

W/L

W/L1

4

= Iref

3Vsat

+2Vt

Vsat+Vt

Vsat

2Vsat+Vt

W/L

W/L

Iref

Figura 2.17

Specchio cascode con dinamica di uscita migliorata

La struttura considerata riduce quindi considerevolmente la caduta residua in uscita inquanto, rispetto alla struttura cascode precedente, cancella il contributo corrispondente a Vt, cioè ilcontributo decisamente più alto, e presenta una dinamica limitata solamente da 2Vsat.

2.5 Riprendendo l’esempio quantitativo considerato nel caso dello specchio Wilson, si passa da 1,26 Va 0,36 V.

2.5 Con VGS e Vsat sono state indicate le tensioni,rispettivamente gate-source e di saturazione, dei dispositivi conrapporto di forma pari a W/L

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 21/64

AMPLIFICATORI CMOS

19

La modifica introdotta ha peraltro reso asimmetrico lo specchio in quanto la caduta ai capidi M3 è ora forzatamente diversa da quella ai capi di M4 per effetto della traslazione di livellointrodotta da M5, la differenza essendo pari a VGS; una differenza di VDS è stata introdotta anche perla coppia di transistori M1-M2 e vale Vt. Ciò peggiora l’accoppiamento tra i transistori in quantointerviene il diverso effetto Early.

E’ possibile realizzare una struttura, sempre del tipo cascode, che ripristina la simmetria pur

conservando una caduta residua in uscita contenuta ed eventualmente pari a quella del circuito dellafigura 2.17. Si tratta di portare ambedue i transistori M1 e M2 ad avere ai capi Vsat.La nuova struttura è rappresentata nella figura 2.18 e nella figura 2.19 in una forma

“generalizzata” che evidenzia, attraverso il parametro di dimensionamento relativo m (scaling delrapporto di forma), l’approccio utilizzato.

Facciamo dapprima riferimento alla figura 2.18.Anche qui si riconoscono i transistori M1-M4 della configurazione cascode originaria alla

quale si aggiunge il transistore M5 e nella quale si modifica la connessione a diodo di M1.

M1

M3

DDV

M5

Iref

M2

Ibias

M4

Iref

W/L W/L

W/L W/L

W/L1

4

Vsat+Vt

VsatVsat

2Vsat+Vt

Figura 2.18

Specchio cascode con dinamica di uscita migliorata e simmetrizzato

Affinché sia M1 che M2 risultino polarizzati con tensione ai capi VDS pari a Vsat i gate diM3 e M4 devono essere posti al livello

2sat GS sat t

V V V V + = + A ciò provvede il transistore M5 opportunamente dimensionato.Deve essere

5 5 2 2GS DS sat t GS t V V V V V V = = + = − e cioè

5 2( )GS t GS t V V V V − = −

Ciò, considerata la relazione quadratica tra corrente e tensione di overdrive, si ottieneriducendo il rapporto di forma di M5, rispetto a quello degli altri transistori, di un fattore 22=4.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 22/64

TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

20

Evidentemente la connessione originaria, a diodo, dei singoli transistori M1 e M3 non risultacompatibile con il voler porre M1 al limite di saturazione e con il dimensionamento di M5 rispettoagli altri transistori: la connessione va cambiata e l’unica soluzione semplice adottabile è quellariportata nella figura.

Nella successiva figura 2.19 si aggiunge un grado di flessibilità in base alla considerazione

che non è a rigore necessario che tutti i quattro transistori M1-M4 abbiano il medesimo rapporto diforma: ciò è necessario separatamente per le coppie M1-M2 e M3-M4, anche se, dal punto di vistadi un buon matching generale, avere dispositivi uguali costituisce un vantaggio. Introducendo unfattore di scaling m, i transistori M3 e M4 potrebbero essere dimensionati sulla base di m2 e cioècon un fattore di forma

2

1 W

m L

dove m è un numero intero uguale o maggiore di 1E’ immediato mostrare che, in questo caso, per ottenere il risultato desiderato, cioè sia M1

che M2 polarizzati al limite di saturazione, è necessario dimensionare M5 in base a uno scaling(1+m)2. 2.6

M1

M3

DDV

M5

Iref

M2

Ibias

M4

Iref

W/L W/L

W/L1

W/L1

m

W/L1

(m+1)

2

2

m2

Vsat+Vt

VsatVsat

(m+1)Vsat+Vt

Figura 2.19

Specchio cascode della figura precedente con dimensionamento “generalizzato”

Il limite inferiore della tensione di uscita si raggiunge quando ai capi di M4 si ha

4 DS sat V mV =

e quindi la caduta residua in uscita risulta pari a

2.6 L’elevazione al quadrato discende, come già fatto notare, dalla dipendenza quadratica della corrente dalla tensione dioverdrive.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 23/64

AMPLIFICATORI CMOS

21

( 1) sat m V + E’ evidente che da questo punto di vista è conveniente porre m=1. Inoltre m di valore

sensibilmente discosto da 1 condurrebbe a difficoltà di dimensionamento causa problemi dioccupazione di area e di accoppiamento.

Nella trattazione precedente relativa ai generatori rappresentati nelle figure 2.15 – 2.19 sonostate considerate valide alcune approssimazioni che in un progetto reale non possono essere

rigorosamente mantenute. Ad esempio è sempre stato trascurato l’effetto body, in particolare perquanto riguarda i transistori “floating” M3 e M4. Inoltre la transizione tra la regione ohmica equella di saturazione non è netta, ma piuttosto graduale e quindi i transistori devono esserepolarizzati con una tensione ai capi maggiore della Vsat nominale, onde garantire buonecaratteristiche quali, ad esempio, la resistenza di uscita.

Il problema del buon accoppiamento tra più dispositivi è particolarmente grave in tecnologiaCMOS e i risultati ottenibili sono in generale inferiori a quelli raggiungibili in tecnologia bipolare;ciò a causa del maggior numero di parametri che controllano il funzionamento di un MOS e delfatto che alcuni di essi, come ad esempio la tensione di soglia, risultano piuttosto dispersi.

Consideriamo ad esempio il caso dello specchio semplice di corrente, riportato nuovamentenella figura 2.19

Definiamo il valor medio e la deviazione della corrente, del fattore di forma e della tensionedi soglia

( )1 2

12

I I I = + 1 2 I I I ∆ = −

1 2

12

W W W

L L L

= +

1 2

W W W

L L L

∆ = −

( )1 2

12t t t

V V V = + 1 2t t t V V V ∆ = −

M1 M2

I1 I2

W/L( )2

W/L( )1

Figura 2.19

Accoppiamento degli elementi di uno specchio semplice

Utilizzando le espressioni precedenti entro la relazione caratteristica del MOS2' ( ) (1 )

D GS t DS

W I k V V V

Lλ = − +

trascurando l’effetto di modulazione della lunghezza del canale nonché i termini di ordinesuperiore si ottiene

2

2

t t

GS t ov

W W

V V I L LW V V W I V

L L

∆ ∆∆ ∆∆ = − = −−

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 24/64

TECNICHE DI POLARIZZAZIONE NEGLI AMPLIFICATORI CMOS

22

Al posto delle deviazioni vanno poi introdotte le varianze o dispersioni statistiche e si ha lasomma di due termini di cui uno dipendente dal dimensionamento geometrico e l’altro dipendentedalla dispersione della tensione di soglia e quindi di origine tecnologica. Il primo termine èindipendente dalle condizioni di lavoro ed è controllato tecnologicamente dal sistema litografico ein sede di realizzazione da opportune e accurate tecniche di layout. Il secondo termine dipendeinversamente dalla tensione di overdrive (come è del tutto intuitivo in quanto più piccola è tale

tensione e maggiore, nel controllo del dispositivo, diviene il peso della variazione della tensione disoglia) e può quindi diventare dominante per piccoli valori di tale grandezza. Pertanto un buonaccoppiamento è favorito dall’utilizzo di dimensioni geometriche non troppo prossime al limiteinferiore imposto dalla tecnologia e da polarizzazioni corrispondenti a tensioni di overdrive nontroppo piccole. D’altro canto queste scelte progettuali influenzano negativamente caratteristiche eparametri quali la risposta in frequenza, l’offset di tensione, le dinamiche di tensione, ecc. e lesoluzioni da adottare sono quindi, come sempre, il frutto di un compromesso.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 25/64

AMPLIFICATORI CMOS

23

Cap. 3

AMPLIFICATORI CMOS A TRANSCONDUTTANZA

(OTA) “ON CHIP”

3.1 AMPLIFICATORI MONOSTADIO

La più semplice struttura di amplificatore CMOS differenziale a transconduttanza è quellagià mostrata nella figura 2.1 e riportata nuovamente nella figura 3.1.

Il guadagno differenziale è dato da

// mid mi oi ol

oi ol

g A g r r

g g=

+;

dovegmi transconduttanza dei transistori di ingresso

goi conduttanza di drain (di Early) dei transistori di ingressogol conduttanza di drain (di Early) dei transistori di carico

INM1 M2

M3

2I

IN

DDV

M4

M5

II

Vbias

SSV

OUT

CL

Figura 3.1Semplice amplificatore a transconduttanza CMOS a singolo stadio

La resistenza di uscita è1

out

oi ol

r g g+

;

Introducendo la tensione di overdrive e il parametro λ della tecnologia, le espressioniprecedenti si possono scrivere

( )

1 1 //

1

2

d mi oi ol

i lGSi ti

A g r r V V λ λ +−

; ;

1 1out

i l

r I λ λ +

;

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 26/64

AMPLIFICATORI CMOS OTA” ON CHIP”

24

La prima delle due mostra che il guadagno può essere controllato tramite la tensione dioverdrive dei transistori di ingresso e la seconda mostra che, fissata la corrente di lavoro, laresistenza di uscita è, in prima approssimazione, determinata dalla tecnologia. Dal punto di vistaprogettuale la tensione di overdrive viene controllata attraverso il dimensionamento geometrico deitransistori di ingresso, cioè attraverso il rapporto di forma

( ) ( )'

1GSi ti

ii

I

V V W k L

− =

Piccola tensione di overdrive, e quindi elevato guadagno, significa elevato rapporto diforma, condizione questa che risulta in accordo con i requisiti di rumore che richiedonotransconduttanza degli elementi di ingresso sufficientemente elevata onde contenere il loro rumoretermico e ridurre il peso relativo del rumore introdotto dal carico. D’altro canto la tensione dioverdrive non può essere ridotta al di sotto di un certo valore pena l’instaurarsi del meccanismo difunzionamento della conduzione sottosoglia. Si vedrà poi, più avanti, discutendo il comportamentoin frequenza, che, sino ad un valore massimo, il prodotto guadagno banda cresce in una strutturacome quella esaminata, al crescere del rapporto di forma dei transistori di ingresso.

In una seconda approssimazione si può anche notare che il parametro λ dipende dallalunghezza di canale e diminuisce al crescere di essa il che indurrebbe, in relazione al guadagnoottenibile, a utilizzare dispositivi di ingresso a canale relativamente lungo, peraltro, a parità di W/L,con aumento dell’occupazione d’area.

Va ricordato anche che l’aumento delle dimensioni dei dispositivi influisce negativamentesulla loro risposta in frequenza, ma, entro certi limiti, non necessariamente su quella dell’interosistema.

La corrente di lavoro deve primariamente essere determinata con riferimento allo slew rate(esterno) necessario per caricare su grande segnale, a velocità sufficiente, la capacità di carico che sidesidera pilotare. Essendo lo stadio evidentemente in classe A vale la relazione

2e

L

I

SR C = e quindi

2e

L

SR I C =

Il guadagno si può quindi esprimere nella forma

' '2 22 1 1 1

2

i i

i id mi out

GSi ti i l i l i le L

W W k k

L L A g r

V V I SR C λ λ λ λ λ λ

= = =− + + +

;

Si noti che il guadagno, in prima e accettabile approssimazione, non dipende daldimensionamento geometrico dei dispositivi di carico, il quale interviene per quanto riguarda larisposta in frequenza e il rumore, sia termico che 1/f.

A titolo di esempio consideriamo una capacità di carico di 10 pF e uno slew rate richiesto di10 V/ µs

La tecnologia utilizzata sia p-well Lmin = 3 µ λi = 0,035 λl = 0,05 3.1

3.1 In realtà il parametro da utilizzare sarebbe il coefficiente di modulazione della lunghezza di canale dXL /dVDS da cuiλ = (dXL /dVDS)/Leff e i valori di λ andrebbero correlati con la lunghezza di canale. Ciò da un lato costituisce unelemento di un certo peso da utilizzare nel progetto, ma nell’esempio qui riportato complicherebbe notevolmente il

procedimento da utilizzare. D’altro canto nel seguito vengono ammesse altre semplificazioni (quale, ad esempio, iltrascurare l’effetto Early nei dispositivi di ingresso) allo scopo di consentire un dimensionamento di primaapprossimazione. (Νella versione più utilizzata del programma di simulazione numerica Spice si considera λ costante).

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 27/64

AMPLIFICATORI CMOS

25

ki’ = 30 µA/V2 ki’ = 12 µA/V2 Vti = Vtl = 0,7 V

Il guadagno è quindi dato da

( )

23,5d

GSi ti

AV V −

;

ed è controllato dalla tensione di overdrive. Per ottenere circa 150 si deve porre157GSi tiV V mV − ;

valore piuttosto basso e che sarebbe quindi favorevole anche per quanto riguarda l’offset ditensione. Tale valore va confrontato con quello che corrisponde, nominalmente, alla transizione trasopra e sotto soglia. Tale transizione corrisponde a

( )

2 2

2 2

' 4

GS t T sub

sub T

kT V V nV n

q

W I k n V

L

− = =

=

con n compreso tipicamente tra 1 e 1,5 in dipendenza dalla tecnologia (funzione crescentedel drogaggio del body); di fatto n è un parametro il cui valore deve essere desunto da unacaratterizzazione sperimentale dei dispositivi. Assumiamo ad esempio n=1,2

( ) 62,4GS t subV V mV − =

Un parametro significativo, in quanto rappresenta una misura dell’efficienza dellapolarizzazione nel produrre transconduttanza, è il rapporto tra la transconduttanza e la corrente dilavoro

' 22m

GS t

W k g L

I I V V = =

−

che risulta proporzionale all’inverso della tensione di overdrive.Al limite di sottosoglia1m

sub T

g

I nV

=

e per n=1,2

132m

sub

gV

I

− =

La transizione tra sotto e sopra soglia è molto graduale e, se si desidera un funzionamentodei dispositivi descrivibile tramite le classiche relazioni sopra soglia, una regola semiempiricarichiede

2 10m

GS t

g I V V

= ≤−

cioè 200GS t V V mV − ≥

Nel caso di tensioni di alimentazione basse si utilizzano a volte valori più bassi dellatensione di overdrive, sino ad essere poco superiori a 100 mV, ma il dimensionamento, utilizzandole relazioni caratteristiche del transistore sopra soglia, risulta poco accurato.

In ogni caso valori molto bassi non sono comunque consigliabili anche perché, a parità dialtre condizioni, la dispersione della tensione di soglia viene a giocare maggiormente neldeterminare l’accoppiamento tra i dispositivi di ingresso.

Poniamo quindi ad esempio

235GSi tiV V mV − = che conduce ad un guadagno

100d

A =

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 28/64

AMPLIFICATORI CMOS OTA” ON CHIP”

26

La corrente di lavoro risulta1

502 e L

I SR C A µ = ⋅ =

Il fattore di forma dei dispositivi di ingresso risulta

( )( )

2'30

i

i GSi ti

I W L k V V

==

−

;

valore abbastanza elevato, corrispondente a una transconduttanza

424mi

Ag

V µ =

E’ evidente che la semplice struttura monostadio considerata è utilizzabile solamentequando sono richiesti guadagni modesti e quando devono essere pilotate capacità di basso valorecon slew rate non troppo elevati. Nel caso di CL = 5 pF, SRe = 5 V/ µs e per un guadagno di circa100 si otterrebbe

235GSi tiV V mV − = 12,5 I A µ = 7,5

i

W

L

;

Il dimensionamento dei dispositivi di carico può essere effettuato, in un primo approccio,sulla base delle caratteristiche di rumore desiderate. Per ridurre il peso del rumore introdotto dalcarico rispetto a quello dovuto ai dispositivi di ingresso la transconduttanza dei transistori M3 e M4deve risultare convenientemente inferiore a quella di M1 e M2

' '

'

'2,4

l i

l i

i

l i il

W W k k

L L

k W W W

L k L L

<

< =

e, per ottenere un peso relativo del rumore in regione bianca (termico) pari a circa il 50%utilizzando le condizioni e il dimensionamento che conducono a un guadagno pari a 100 e a unfattore di forma dei dispositivi di ingresso pari a 30

0,626 18,75l i

W W

L L

=

;

corrispondente a una transconduttanza

212ml

Ag

V µ =

(pari alla metà di quella dei dispositivi di ingresso, considerate le condizioni poste sulrumore)

e a una tensione di overdrive

4 471GS tlV V mV − =

valore elevato che influenza negativamente la dinamica di tensione in uscita; d’altro cantoun valore significativamente inferiore comporterebbe un peso importante del rumore dovuto alcarico.

Utilizzando per i transistori di ingresso la lunghezza di canale minima si ottieneLi = 3 µ Wi = 90 µ

Per i dispositivi di carico, onde ridurre il loro contributo al rumore flicker, convieneutilizzare una lunghezza di canale maggiore, ad esempio 5 µ; si ha allora

Ll = 5 µ Wl = 93,75 µ

Il transistore M5 deve essere dimensionato in modo che la sua tensione di overdrive, che

interviene nel determinare il limite inferiore della dinamica del modo comune in ingresso, non siatroppo elevata in relazione alla tensione di alimentazione utilizzata. Essendo esso polarizzatotramite il doppio della corrente di lavoro degli altri transistori ciò comporta sicuramente un elevato

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 29/64

AMPLIFICATORI CMOS

27

rapporto di forma e quindi notevole occupazione di area ed elevata capacità parassita del nodocorrispondente al suo drain e ai source dei transistori di ingresso. Ponendo ad esempio VGS-Vt = 250mV si ottiene

5

53W

L

=

e quindi L5

= 3 µ W5

= 159 µ Si ottengono quindi dispositivi tutti di notevoli dimensioni, risultato questo connesso con

l’estrema semplicità della struttura che solo in queste condizioni può ragionevolmente soddisfare lespecifiche imposte. Per ottenere un dimensionamento più contenuto dal punto di vista geometricodevono essere rilassate tali specifiche: in particolare capacità di carico e slew rate.

Il dimensionamento sinora progettato costituisce un primo approccio e va verificato eripreso per iterazioni successive anche in relazione ad altri aspetti di rilievo connessi concaratteristiche desiderabili dell’amplificatore risultante: la tensione di polarizzazione in uscita (cioèla traslazione di livello introdotta), la dinamica di uscita, la dinamica del modo comune in ingresso,la risposta in frequenza e il margine di fase, l’offset di tensione riferito all’ingresso, la reiezione del

modo comune. Inoltre il dimensionamento deve essere considerato, per quanto riguarda alcuniaspetti, anche tenendo conto del sistema di polarizzazione utilizzato. In una struttura così sempliceutilizzante un numero assai ridotto di elementi circuitali (transistori), l’utilizzo di una tecnologiaadeguata (nell’esempio considerato p-well) consente di evitare l’effetto body.

La dinamica di uscita dipende ovviamente dal livello di riferimento assunto per gli ingressi(i gate di M1 e M2). Considerando tale livello pari a 0 V e facendo riferimento a una utilizzazioneretroazionata dell’amplificatore e assenza di modo comune, si può in prima approssimazioneritenere nullo il segnale sui due ingressi. Quindi il limite inferiore della dinamica di uscita si haquando M2 raggiunge il limite della regione ohmica cioè Vsat2 = VGS2-Vti ai capi e perciò con ildrain a –Vti rispetto al gate; il limite superiore corrisponde all’entrata di M4 nella regione ohmica ,cioè a VDD-Vsat4 ed è quindi limitato dalla tensione di overdrive di M4. Dunque l’escursione

dinamica massima nominale consentita risulta pari a4 DD sat tiV V V − +

e nell’esempio risulta circa poco discosto da VDD. Va notato che la dinamica effettivautilizzabile va determinata in considerazione della massima distorsione accettabile, per cui ènecessario mantenere un certo margine rispetto al limite di transizione saturazione↔ regioneohmica.

La dinamica di uscita condiziona la scelta del livello di polarizzazione in tensione dei draindi M2 e M4 che andrebbe posto al centro della dinamica. Ovviamente tale livello dipendedall’effetto Early di cui quindi si deve tenere conto per tutti i transistori del sistema e diconseguenza condiziona il dimensionamento dei vari dispositivi. Come già detto la procedura di

dimensionamento va ripresa e comunque si presenta notevolmente più complessa e difficilmenteeffettuabile sulla carta. Anche il comportamento in frequenza e il conseguente margine di fasedevono essere tenuti in conto producendo ulteriore complessità nell’approccio progettuale e lanecessità di procedere comunque per iterazioni e quindi approssimazioni successive sfruttandoadeguate tecniche di simulazione numerica.

Per quanto riguarda la dinamica del modo comune in ingresso 3.2 evidentemente essa èlimitata inferiormente dal limite di saturazione Vsat5 di M5 pur rimanendo inalterata la VGS di M1 eM2 ed è quindi, in valore assoluto

( )5 1 5 1SS sat GS SS sat sat tiV V V V V V V − − = − + +

mentre è limitata superiormente dal limite di saturazione di M1 e M2 che si verifica quandoil drain di tali transistori scende sotto il gate di una tensione pari a quella di soglia

3.2 La dinamica del modo comune in ingresso si può definire come l’escursione del segnale di modo comune entro laquale rimane sostanzialmente costante il guadagno di modo differenziale.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 30/64

AMPLIFICATORI CMOS OTA” ON CHIP”

28

( )1 3 3 DD DG GS DD sat tl tiV V V V V V V + − = − + −

E’ evidente che la struttura considerata presenta una dinamica del modo comune in ingressoasimmetrica: è cioè migliore quella positiva rispetto a quella negativa. Nell’esempio sopra riportatolo scostamento dall’alimentazione negativa è pari a

1,185 Vmentre quello dall’alimentazione positiva è pari a

0,471 VTale asimmetria è ovviamente tanto più gravosa quanto più basse sono le tensioni di

alimentazione e risulta sostanzialmente inaccettabile quando la tensione totale di alimentazioneammonta a pochi volt.

Ovviamente, a parità di altre condizioni, i risultati ottenuti si invertono nel caso dellastruttura complementare rispetto a quella della figura 3.1, rappresentata nella figura 3.2.

INM1 M2

M3

2I

IN

DDV

M4

M5

II

Vbias

SSV

OUT

Figura 3.2

L’amplificatore della figura 3.1 nella versione n-well

In questo caso è favorita la dinamica negativa rispetto a quella positiva e ciò suggerisce unasoluzione di carattere generale e cioè l’utilizzo contemporaneo, cioè in parallelo, di ambedue lestrutture. Tale soluzione viene implementata in strutture più efficienti di quella particolarmentesemplice qui considerata e cioè strutture cascode (folded) o strutture a più stadi (due più uneventuale stadio di uscita) oppure, più frequentemente in amplificatori completamente differenzialiche comportano una retroazione sul modo comune. E’ evidente che una elevata dinamica del modocomune in ingresso è particolarmente importante quando l’amplificatore viene retroazionato nellaconfigurazione a guadagno unitario (buffer).

Si può infine notare che lo stadio considerato presenta potenzialmente miglioricaratteristiche di rumore nella regione 1/f , cioè a bassa frequenza, se realizzato nella versione n-well invece che p-well: ciò perché le attuali tecnologie producono dispositivi a canale p affetti daminor rumore flicker che non i dispositivi a canale n. Peraltro in n-well le caratteristiche dei

dispositivi a canale n e a canale p differiscono maggiormente, e quindi è peggiore lacomplementarità, in quanto il dispositivo n è intrinsecamente superiore a ragione della maggiormobilità dei portatori e, in generale, i dispositivi realizzati nel substrato hanno miglioricaratteristiche di quelli realizzati in well.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 31/64

AMPLIFICATORI CMOS

29

Tra le limitazioni della struttura sinora considerata evide in particolare il guadagnodecisamente modesto, tipicamente inferiore al centinaio o, al più, di poco superiore. Il guadagno èovviamente condizionato dal valore della capacità da pilotare in connessione con lo slew raterichiesto. Esso risulta proporzionale all’inverso della radice del prodotto di tali grandezze:

1d

e L

ASR C

÷

Una riduzione di tali specifiche non conduce a un sensibile aumento del guadagno anche seaccompagnata da un aumento (entro i limiti del possibile e comunque opinabile) del fattore di formadei dispositivi di ingresso.

Una soluzione alternativa per una struttura monostadio è quella di utilizzare una architetturacascode, il che equivale a ridurre considerevolmente (tipicamente di diverse decine di volte) i valoridi λ, ottenendo così, a parità di altre condizioni guadagni superiori di circa due ordini di grandezza,cioè nel campo delle migliaia.

DDV

INM1 M2

M10

2I

IN

M9

II

M3 M4

Vbias1

M5 M6

M7 M8

OUT

CL

SSV

Vbias2

Vbias3

M11

I

+I

10

9

Figura 3.3

Amplificatore monostadio cascode

La figura 3.3 mostra un amplificatore monostadio che utilizza in ingresso unaconfigurazione cascode e un carico attivo costituito da uno specchio Wilson simmetrizzato.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 32/64

AMPLIFICATORI CMOS OTA” ON CHIP”

30

L’evidente svantaggio della soluzione considerata è costituito dalla utilizzazione di unnumero di dispositivi in serie doppio rispetto a quello della semplice struttura di partenza e quindi didinamica di uscita e di modo comune in ingresso assai ridotte.

La struttura di ingresso è polarizzata, per quanto riguarda la caduta di tensione relativa aitransistori M1 (di ingresso) e M3 (trasferitore di corrente) e, corrispondentemente, M2 e M4,tramite il transistore M10 che può essere dimensionato geometricamente e attraverso la corrente I10

che lo attraversa in modo da mantenere M1 e M2 al limite della saturazione al variare del livello dimodo comune in ingresso: i gate di M3, M4 risultano così agganciati al modo comune in ingresso.Ricordiamo che lo specchio Wilson è intrinsecamente caratterizzato da una cattiva dinamica

di uscita; a questo è possibile rimediare sostituendolo con una struttura cascode come quellariportata nella figura 2.17 o quella della figura 2.18.

DDV

INM1 M2

M10

2I

IN

M9

II

M3 M4

Vbias1

M5 M6

M7 M8

OUT

CL

SSV

Vbias2

M11

I

+I

10

9

Figura 3.4

Amplificatore monostadio cascode con migliori caratteristiche di dinamica

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 33/64

AMPLIFICATORI CMOS

31

Un possibile amplificatore così modificato (con carico del tipo di quello della figura 2.18) èrappresentato nella figura 3.4. Malgrado siano stati introdotti significativi miglioramenti rispettoalla struttura cascode più semplice, l’amplificatore risulta inadatto all’utilizzazione nel caso ditensioni di alimentazione non sufficientemente elevate. Inoltre risultano necessarie tre tensioni dipolarizzazione.

Una soluzione più efficiente è quella riportata nella figura 3.5. Si tratta evidentementesempre di una struttura cascode con i relativi vantaggi, ma la tensione totale utilizzata risultasignificativamente inferiore a quella della struttura precedente. E’ peraltro necessario introdurre,ovviamente, una addizionale coppia di generatori di corrente (M9 e M10 nella figura) il che, tral’altro comporta problemi di rumore. La rete di polarizzazione deve fornire 4 tensioni e, soprattuttonel caso sia richiesta limitata dipendenza dalle tensioni di alimentazione, può risultare complessa, alpunto da richiedere un numero di componenti comparabile o addirittura superiore a quellidell’amplificatore vero e proprio.

DD

INM1 M2

M9

2I

IN

1

M10

M11

I1I1

M3 M4

Vbias1

Vbias2

Vbias3

M5 M6

M7 M8

I2I2

Vbias4

OUT

CL

Figura 3.5

Amplificatore monostadio folded cascode

Nella figura 3.6 è riportato un amplificatore di questo tipo completoA sinistra è rappresentata un struttura di polarizzazione autoalimentata basata su∆VBE,

costituita dai transistori M11-M14, J1-J2 e dal resistore R. Tale struttura fornisce direttamente latensione di gate del generatore M5 di polarizzazione degli elementi di ingresso del folded cascode ealimenta a specchio i generatori M15 e M16 che a loro volta alimentano M17 e M18. La caduta aicapi di M17 è utilizzata per polarizzare in tensione i gate dei trasferitori di corrente M3-M4. Lacaduta ai capi di M18 polarizza i gate dei transistori M9-M10 che alimentano il carico del foldedcascode. M18 funge anche da specchio insieme a M19 il quale alimenta M20 che polarizza i gatedei transistori M5 e M6 del cascode di carico. M20 è dimensionato in con (W/L)20 pari a ¼ dei

fattori di forma di M5-M8 in modo da portare M7 e M8 al limite di saturazione e minimizzare cosìla caduta residua in uscita dovuta al carico.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 34/64

AMPLIFICATORI CMOS OTA” ON CHIP”

32

M 1 1 J

1

M 1 3

M 1 2

J 2 M

1 4

V b i a s

R

x m

D D

V

I N

M 1

M 2

M 9

2 I

I N

1

M 1 0

M 1 1

I 1

I 1

M 3

M 4

M 5

M 6

M 7

M 8

I 2

I 2

O U T

C L

M 1 5

M 1 6

M 1 7

M 1 8

M 1 9

M 2 0

I 3

Figura 3.6

Amplificatore monostadio folded cascode completo

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 35/64

AMPLIFICATORI CMOS

33

3.2 AMPLIFICATORI A DUE STADI

La più semplice struttura di amplificatore CMOS differenziale a transconduttanza a duestadi è quella riportata nella figura 3.7. L’amplificatore richiede l’introduzione di una rete dicompensazione in frequenza che nella figura non è inserita; le tecniche di compensazione verrannodescritte più avanti.

DDV

Vbias

M6

I2

INM1 M2

M3

2I

IN

1

M4

M5

I1I1

SSV

OUT

M7

CL

Figura 3.7

Semplice amplificatore a due stadi

Il secondo stadio è un semplice stadio source comune polarizzato in classe A,configurazione atta a pilotare un carico capacitivo (pilotaggio di corrente).

Il guadagno differenziale, a bassa frequenza, dell’amplificatore è6

06 7

mi md

oi ol o o

g g A

g g g g+ +;

e la resistenza di uscita

6 7 2 6 7

1 1 1o

o o

r g g I l l

=+ +

;

(il pedice i indica i dispositivi di ingresso, l quelli di carico, go indica la conduttanza di drain)Nella struttura riportata nella figura 3.7 la dinamica di uscita e la capacità di corrente sono

limitate dalla configurazione del secondo stadio che opera in classe A; in particolare la correnteerogabile in fase di source è limitata dalla polarizzazione del carico M7.Una struttura più efficiente da questo punto di vista è riportata nella figura 3.8.Il secondo stadio, costituito dai transistori M6-M9, è una struttura del tipo push-pull

polarizzata in classe A-B: i due transistori di uscita M8 e M9 sono dimensionati in modo da averepolarizzazioni gate-source circa uguali e il più possibile limitate e quindi massimizzazione delladinamica (simmetrica) di uscita. Il follower M6-M7 opera come traslatore di livello il che comportaun dimensionamento di M6 tale da accordarsi con una elevata tensione di overdrive.

Il guadagno del secondo stadio è dato da8 9

28 9

m m

o o

g g A

g g

+

+; (a parte il segno)

per cui il guadagno totale risulta dato da

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 36/64

AMPLIFICATORI CMOS OTA” ON CHIP”

34

8 90

8 9

m i m m

oi ol o o

g g g A

g g g g

++ +

;

Si noti che nel caso di ambedue le soluzioni presentate il guadagno in continua può essereanche piuttosto elevato, da qualche migliaio a qualche decina di migliaia, in dipendenza peraltrodalle caratteristiche tecnologiche dei dispositivi.

Le soluzioni considerate sono utilizzabili per il pilotaggio di capacità di valore relativamente

modesto, cioè capacità (integrate) sino a poche decine di pF. Capacità più elevate presenterebberoproblemi di compensazione in frequenza in quanto introdurrebbero un polo a frequenza ancheinferiore al prodotto guadagno-banda (si veda quanto discusso nel paragrafo 3.3).

INM1 M2

M3

2I

IN

DDV

1

M4

M5

I1I1

Vbias

SSV

OUT

CL

M6

M7

M9

M8

Figura 3.8

Amplificatore a due stadi con dinamica di uscita e capacità di corrente migliorate.

Qualora sia necessario ottenere guadagni particolarmente elevati si può, ovviamente,ricorrere allo stesso approccio considerato nel caso degli amplificatori monostadio: l’utilizzazionedi configurazioni cascode, come mostrato nelle figure 3.9 e 3.10.

La figura 3.9 mostra una struttura derivata direttamente da quella della figura 3.8 tramitel’utilizzazione di una architettura cascode “telescopica” per il primo stadio (si veda la figura 3.3).

Sono evidenti

- maggiore complessità- ridotta dinamica in uscita dal primo stadio e quindi da tutto l’amplificatore- ridotta dinamica del modo comune in ingresso anche se migliorata rispetto a quella di un

cascode privo del tracking introdotto dal transistore M10L’amplificatore risulta quindi inadatto all’utilizzazione nel caso di tensioni di alimentazione

non sufficientemente elevateNella figura 3.10 è riportata una soluzione che consente di ottenere maggiore dinamica in

uscita. Essa è ovviamente derivata dalla struttura monostadio della figura 3.5 utilizzante la ben notaconfigurazione folded cascode. Tale configurazione è quella più spesso utilizzata nell’ambito degliamplificatori CMOS on-chip per ottenere elevati guadagni e buona risposta in frequenzacompatibilmente con le ridotte tensioni di alimentazione utilizzate.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 37/64

AMPLIFICATORI CMOS

35

DDV

INM1 M2

M10

2I

IN

M9

II

M3 M4

Vbias1

M5 M6

M7 M8

CL

SSV

Vbias2

M11

I

+I

10

10

OUT

M12

M13

M15

M14

Figura 3.9

Amplificatore cascode a due stadi.

DDV

INM1 M2

M9

2I

IN

1

M10

M11

I1I1

M3 M4

Vbias1

Vbias2

Vbias3

M5 M6

M7 M8

I2I2

Vbias4

CL

OUT

M12

M13

M15

M14

Figura 3.10

Amplificatore folded cascode a due stadi.

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 38/64

AMPLIFICATORI CMOS OTA” ON CHIP”

36

3.3 LA COMPENSAZIONE IN FREQUENZA

Gli esempi di amplificatori OTA mostrati nei paragrafi precedenti non riportano le retiutilizzate per ottenere, ad anello chiuso, un margine di fase adeguato. Consideriamo dunque ora lepossibili, più semplici e più frequenti soluzioni del problema della compensazione in frequenza.

Iniziamo col considerare la più semplice struttura monostadio della figura 3.1 riportata

nuovamente nella figura 3.11. In questo caso non si tratta propriamente di un compensazione infrequenza, ma piuttosto della semplice progettazione dal punto di vista della risposta in frequenza,senza l’aggiunta di reti addizionali.

+IN IN

+V

-V

- C

M1 M2

M3 M4

M52I

p-well

DD

SS

L

1 2

biasV

0

Figura 3.11

Semplice amplificatore OTA monostadio. Sono evidenziati i nodi a cui sono associate le

singolarità principali.

Il nodo 2 a cui sono associate la capacità di carico CL e una capacità intrinseca (“parassita”)C2 dà luogo al polo dominante.

Il nodo 1, cui è associata la capacità intrinseca C1, dà luogo a una coppia polo-zero(“doppietto”) distanti una ottava, le cui pulsazioni sono

polo 21

ml

p

g

C w =

zero1

2 ml z

g

C w =

Il prodotto guadagno-banda è dato da

2

miT

L

g

C C w =

+

Diamo di seguito un esempio di dimensionamento dell’amplificatore che conduca adottenere un margine di fase accettabile. Dall’esempio si deduce che, nel caso della tecnologiaCMOS, il prodotto guadagno-banda non è solitamente noto a priori, come invece accadesostanzialmente in tecnologia BJT, ma è dipendente da parametri almeno in qualche misuracontrollabili dal progettista.

Una condizione che è ragionevole porre in partenza appare quella relativa alla posizione deldoppietto che, per le note ragioni di settling time, è bene non si trovi al di sotto di ωT. Qualora il

5/14/2018 Amplificatori CMOS - slidepdf.com

http://slidepdf.com/reader/full/amplificatori-cmos 39/64

AMPLIFICATORI CMOS

37

polo ωp2 del doppietto sia posto in coincidenza con ωT il margine di fase risulta di circa 70° e si puòquindi solitamente considerare sufficiente (>60°).

Possiamo quindi utilizzare la coppia di relazioni

1 2

m l mi

L

g g

C C C =

+

2

mi

T L

g

C C w = + a fronte peraltro di tre incognite relative alla polarizzazione e al dimensionamento

geometrico degli elementi della struttura:

0 I i

W

L

æ ö÷ç ÷ç ÷çè ø

l

W

L

æ ö÷ç ÷ç ÷çè ø

E’ dunque necessario introdurre un ulteriore vincolo operando una scelta per ildimensionamento dei transistori di ingresso o ponendo una condizione relativa alla polarizzazionedegli stessi. Il guadagno dell’amplificatore è determinato dalla tensione di overdrive dei transistoridi ingresso Vovi

2 1d

ovi i l A V λ λ +;