Tesi_Aimone

description

Transcript of Tesi_Aimone

Politecnico di Torino

Master Thesis

Ultra Wide Band Variable Gain IFAmplifier for V-band Transceivers

Author:

Alessandro Aimone

TU Supervisors:

Prof. Dr.- Ing. Georg Boeck

Ing. Andrea Malignaggi

PoliTo Supervisors:

Prof. Giovanni Ghione

Prof. Fabrizio Bonani

A thesis submitted in fulfillment of the requirements

for the degree of Science in Micro- and Nanotechnologies for ICT

September 2012

i

Declaration of Authorship

I, Alessandro Aimone, declare that this thesis titled, ’Ultra Wide Band Variable

Gain IF Amplifier for V-band Transceivers’ and the work presented in it are my own. I

confirm that:

This work was done wholly or mainly while in candidature for a research degree

at this University.

Where I have consulted the published work of others, this is always clearly at-

tributed.

Where I have quoted from the work of others, the source is always given. With

the exception of such quotations, this thesis is entirely my own work.

I have acknowledged all main sources of help.

Where the thesis is based on work done by myself jointly with others, I have made

clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

ii

i

Project Overview

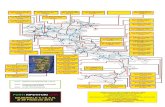

This masther thesis is the result of a 6 months project carried out in the Microwave

department of TU Berlin, under the supervision of Professor Georg Boeck. The aim

of the work is to study and design a wideband Variable Gain Amplifie within the

framework of WioNet project (No.10033322): Wireless Communication and Networks

(WN), financially supported by the Federal Ministry of Education and Research of

Germany (BMBF). The part of the WioNet project that is carried on in the Profes-

sor Boeck group, consists in the design of an entire 60 GHz transceiver, which the

VGA will be part of. The project started in the middle of 2010 and the transceiver

is expected to be completed and fully functional during the course of 2013. The first

printed version of the variable gain amplifier is expected to be measured in the month

of September 2012, while an optimized version should be obtained at the end of the year.

Acknowledgements

I would like to acknowledge my Politecnico supervisors for helping me improving this

work. In the same way, I am grateful to Professor Boeck for giving me the opportunity

of working in his group.

Grazie soprattutto ad Andrea: nonostante il nostro ben diverso approccio alla vita, ti

ringrazio per la continua disponibilita e l’infinito numero di ore passate ad assistermi.

Senza di te questo lavoro non sarebbe che una montagna di dubbi.

Grazie alla mia famiglia.

Grazie nonna Sarina: i tuoi piatti accompagnati da lunghe discussioni, piene di saggezza,

mi hanno aiutato ad affrontare diversi momenti difficili e sono sicuro che ancora lo

faranno. Grazie nonno Piero per il tuo affetto, silenzioso ma costante.

Grazie nonna Anna: in ogni momento mi infondi coraggio dimostrandomi che ogni giorno

e buono per partire, buttandosi in una nuova avventura senza aver mai paura.

Grazie zii, cugini e fratello: anche se non spesso vicini, l’affetto che mi lega ad ognuno

di voi mi sostiene continuamente.

Thanks to those, among my fellow students, who helped me face the never-lasting classes.

Stefano: grazie per la disponibilita e le sagge discussioni nelle piccole camere del Berlioz,

nonche nei luminosi spazi del Rolex.

Adrien & Benjamin: ensemble jusqu’a la fin. Merci pour toutes les betises qu’on s’est

raconte. Merci pour m’avoir supporte (tous les team-work !) et merci pour pas souligner

que je fais plans des fautes quand j’ecris dans cette horrible langue (oui, maintenant

aussi!).

Grazie anche ad Emanuele: e grazie a te se il mio master si e concluso 7mila volte meglio

di come e iniziato!

Merci Benoıt I : toutes les choses qu’on a fait ensemble ont vraiment change ma experience

a Grenoble. Merci a toi et a tous tes fous amis pour les grillades et les soirees passees

ensemble. Vous avez ete super avec moi !

Grazie a Valeria e a Chiara: in coppia per forza. Persi un po’ per la distanza o altre

stupidaggini, cosı come abbiamo iniziato, spero si finisca presto da Busters in un freddo

inverno torinese, a scambiarsi sveglie e calzini come regali!

Merci Benoıt II : je serais pas tombe amoureux de Copenhague si c’etait pas pour toi.

C’est vrai, c’est vrai, je tombe amoureux un peu facilement ! Mais je t’assure : t’as

ete un ami exceptionnel et si je remercie, c’est pas seulement pour tous tes bieres et

cocktails, que je ”goutais” seulement quand meme!

v

vi

Thanks to my first-aid group in Lausanne.

Jenny! I cannot write what I think about you, because this is an official work! I therefore

have to get sentimental and tell you that with you I had the best connection ever. The

days spent talking of everything as well as those spent judging your food and your lack

of hygiene will be forever in my heart.

E Valeria! Grazie per le incredibili stupidaggini nonche i discorsi piu seri. Ma soprattutto

grazie per la tua bonta. Non so come altro dirlo: sei la persona piu buona e generosa

che io abbia mai conosciuto e spero un giorno di riuscire a diventare un po’ piu come te.

Grazie a Cinzia. Splendida Cinzia con un’infinita pazienza nei miei confronti. Grazie

per il sostegno in terra straniera. Sei il mio pilastro nonche la mia piu cara amica.

Prometto: saro carino al telefono! Tu sopportami ancora un po’ e ti dedico la tesi del

dottorato!

Un grande, immenso grazie e per Giuliana: non posso immaginare come sarebbero stati

gli ultimi anni senza di te. Grazie per l’immenso affetto dimostrato, mai dovuto, ma

sempre presente. Grazie per il supporto, tu solo sai quante volte mi hai sentito lamen-

tarmi. Grazie per l’ospitalita, non dimentichero mai la vecchia via Beaulard (letta come

si scrive, perche altrimenti non capiscono) e la nuova, ridente, via Duino. Grazie per

tutte le milioni di occasioni in cui mi sei stata vicino: le mie infinite malattie (il diabete

e ancora lı!) e i mille test; i miei amori vecchi, ma sempre sofferti; le mie noiosissime

spiegazioni sulle onde e i loro amici, e le mille altre che, se scrivessi, renderebbero i

ringraziamenti piu lunghi della tesi.

Il piu importante ringraziamento e per mio padre: Claudio, la dedica di questo intero

lavoro (la trovi qualche pagina piu avanti!) non e abbastanza per ringraziarti. Non solo

il vile denaro, che pur mi ha permesso di fare tutte le cose che ho fatto fino ad oggi, e

cio di cui ti sono grato. Grazie per le lezioni di piano, grazie per Lilli, grazie per avermi

tirato fuori da tutti i casini in cui sono un mastro a ficcarmi. Grazie a te e a mia madre.

Grazie per avermi fatto e per avermi reso la persona che sono oggi: ogni mio interesse,

nonche ogni aspetto della mia personalita, e dovuto a voi.

Contents

Declaration of Authorship ii

Project Overview iii

Acknowledgements iv

List of Figures vii

1 Introduction 1

1.1 Transceiver architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.1.1 Variable Gain Amplifiers . . . . . . . . . . . . . . . . . . . . . . . . 3

1.2 Technology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.3 Methods and Equipment . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 Design Specifications 6

2.1 Bandwidth . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.1.1 Feedback Amplifiers . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.2 Variable Gain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.3 Impedance Matching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.4 Linearity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.5 Stability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.6 Group Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3 Amplifier Design 24

3.1 VGA Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.1.1 Fixed Gain Stages . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.1.2 Variable Gain Stages . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.1.3 Active Feedback . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.1.4 Output Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.1.5 Additional Components . . . . . . . . . . . . . . . . . . . . . . . . 33

3.2 Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.3 Circuit Simulations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.3.1 Statistical Simulations . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.3.2 Post layout simulations . . . . . . . . . . . . . . . . . . . . . . . . 44

vii

Contents viii

4 Conclusions and Outlook 46

A Circuit Layout 49

Bibliography 50

i

List of Figures

1.1 Transceiver simplified schematic . . . . . . . . . . . . . . . . . . . . . . . . 2

2.1 Miller capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.2 Feedback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3 Active Feedback Block Scheme . . . . . . . . . . . . . . . . . . . . . . . . 12

2.4 Resistive degenerated amplifier . . . . . . . . . . . . . . . . . . . . . . . . 14

2.5 Different impedance configurations: (a) receiver and (b) transmitter chain 16

2.6 Amplifier signal swings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.7 Third order intercept point . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.8 two-ports network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.9 Stability regions in the ΓL plane . . . . . . . . . . . . . . . . . . . . . . . 22

3.1 Chosen VGA topology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.2 Fixed gain amplifier topology . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.3 Variable gain amplifier schematic . . . . . . . . . . . . . . . . . . . . . . . 28

3.4 PMOS I-V characteristic curves . . . . . . . . . . . . . . . . . . . . . . . . 29

3.5 Feedback block schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.6 Active feedback effect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.7 Buffer topology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.8 Current mirror schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.9 DC Block (a) schematic and (b) Bode plot . . . . . . . . . . . . . . . . . . 34

3.10 Layout of the active area . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.11 VGA AC response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.12 Controlling voltage gain dependency . . . . . . . . . . . . . . . . . . . . . 39

3.13 P1dB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.14 Input third-order intercept point . . . . . . . . . . . . . . . . . . . . . . . 40

3.15 Edwards stability factors . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.16 VGA CMRR at different gain levels . . . . . . . . . . . . . . . . . . . . . 41

3.17 Noise Figure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.18 Monte Carlo simulation of VGA gain . . . . . . . . . . . . . . . . . . . . . 43

3.19 Monte Carlo simulation of VGA bandwidth . . . . . . . . . . . . . . . . . 44

3.20 Monte Carlo simulation of VGA CMRR . . . . . . . . . . . . . . . . . . . 44

A.1 Whole circuit layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

ix

i

A mio padre. . .

x

i

Chapter 1

Introduction

The importance of high speed communications is becoming greater and greater as mobile

devices get more powerful. Multimedia applications get involving larger and larger data

amount to be exchanged during the last years. Wireless communications offer a much

greater mobility with respect to cabled ones. However, the second ones still offer a much

greater data rate.

When data rate in the gigabit range is required, high frequency signals have to be

used. When looking at unlicensed frequency bands, the one around 60 GHz is a good

candidate for high speed communications. 60 GHz signals suffer indeed from a large free-

space attenuation due to the peak in the oxigen absorption spectrum and this makes this

frequency particularly suitable for high-speed short-range, i.e. indoor, communications:

no more than few meters should divide the trasmitter from the receiver in order to

correctly receive the sent signal. Furthermore, very high attenuation has been proved

for 60 GHz signals when passing through common materials walls, which would make

this technology communications limited to one room only.

IEEE Std 802.15.3c standard classifies 60 GHz communications as ones for WPAN (Wire-

less Personal Area Newtorks) use. This standard divides the whole band, from 57 GHz

to 66 GHz, into four channels, whose carrier frequencies are separated by 2.16 GHz.

This would allow data rate larger than 2 Gbit/s, depending on the modulation scheme.

Efforts have been made in last years in order to design a working 60 GHz transceiver and

some papers giving an overview of the different blocks design can be found in literature

[1] - [6]. Considering the use that has to be done of them, integrated, low-power and

cheap systems are needed.

Even if a lot of interest is put in these systems, 60 GHz circuits design keeps being very

challenging: because of the mm-wavelength, mismatch effects have a very strong impact

1

Chapter 1. Introduction 2

on the signal. Large care must be put when considering parasitics and other unwanted

effect, such as the skin one. Moreover, following the RF approach with distributed

parameters, a whole set of phenomena, like the inductive behaviour of every trasmission

line, should be kept in mind.

1.1 Transceiver architecture

The transceiver is being designed with a superheterodyne topology (Figure 1.1). This

topology has been chosen because, even if more complex, more power consuming and

more area demanding in comparison to the homodyne one, its use avoids issues such as

self-mixing and DC offsets. In addition, the design of an intermediate frequency phase

locked loop (PLL) is easier with respect to the one of a 60 GHz PLL.

Figure 1.1: Transceiver simplified schematic

The incoming signal at the antenna of the receiver is pre-amplified by a low-noise am-

plifier whose aim is to bring the signal to a wider amplitude, in order to be able to

distinguish it from the collected noise. The signal gets then shifted to an intermediate

frequency (IF) by a first mixer. The mixer receives a reference signal from the PLL at

the frequency of about 40 GHz. The downconversion will then bring the signal at a

center frequency of about 20 GHz. This signal is amplified by the IF-Buffer just before

passing through another mixer. This second downconversion is made with a reference

signal that, before reaching the mixer, goes through a frequency divider. Both the IF

and this reference signal are at about 20 GHz and the information is therefore brought in

baseband. Just before the analog-to-digital converter a variable gain amplifier is placed.

Concerning the transmitter chain, the incoming signal from the DAC gets amplified by

Chapter 1. Introduction 3

the variable gain amplifier of an extent that depends on the power that has to be trans-

mitted. Two following upconversions, with the same frequency values as the receiver

branch, bring the signal up to 60 GHz where, thanks to a power amplifier, it is fed to

the antenna and finally radiated. The digital to analog conversion is to be made with

the Analog Devices AD9739, while the chosen ADC is EV10AQ190, produced by e2v

Semiconductors. Both are high speed converters, with differential low impedance inter-

facing connections toward the transceiver circuitry.

A monolithic integration of the system starts after the antenna and ends with the VGA.

At the antenna a power of −40 dBm is expected. The transmitted power level should

reach the maximum value of 10 dBm.

Even if some 60 GHz transceivers can already be found in the literature, several of them

omit the baseband part from the integrated solution [4] - [5]; some complete solutions,

including the baseband circuitry, can already be found [6].

1.1.1 Variable Gain Amplifiers

As introduced, this work focuses on the design of the variable gain amplifier that is put

just at the edge of the chip, before the digital converters. This VGA has expressely

been designed in order to work within the transceiver framework and therefore all its

specifications are determined by the global system required performance.

US Federal Communications Commission (FCC) defines as Ultra Wide-Band (UWB) a

signal whose bandwidth is broader than 500 MHz or than 20% of its center frequency.

Because of standard requirements, i.e. channel width of 2 GHz, the amplifier can be

classified as a UWB one.

Because of its application, the VGA has to be designed in order to handle signal span-

ning from MHz to GHz range frequencies. The fact that the amplifier is working both

at low and at RF regions, constitute one of the most challenging aspects of this design.

In fact, during the development of this work, some techniques typically when dealing

with high RF were not suitable because of the lower frequencies signals, e.g. impedance

matching techniques (Section (2.3)). On the other hand, obtaining high gain at GHz

frequency is much more complicated than for signals in the MHz range. As a bright

side, at frequencies of few GHz, high RF annoying effects, such as coupling and strong

parasitics effects, are much more soften and do not require the same amount of care that

Chapter 1. Introduction 4

a 60 GHz designer is used to take.

1.2 Technology

The chosen technology is always a compromise between performances and costs. 60

GHz systems are not easy to be realized because of the very high working frequencies.

Some technologies, such as III/V ones, are the best candidates for high frequency system

because of the high speed transistors and excellent RF performances and have been often

used in the mm-wavelength tranceivers found in literature [1], [4], [7].

Because of their high cost though, CMOS technology is still the more desiderable and

several high frequency transceivers have been designed using this technology [3], [2], [6].

In fact, CMOS is the cheapest available technology and with the scaling of its transistors

dimensions, its transistor have in the last years reached speed high enough to make them

suitable for RF designers, still with some difficulties to be solved such as the lowering

of the breakdown voltage which because a critical issue when designing power stages.

If willing to monolithically integrate the transceiver analog part with the digital one,

CMOS offer the additional advantage of a simplified integration.

The technology chosen for the transceiver project is the TSMC 90nm CMOS one. TSMC

offers low cost but reliable technology. The circuit model implemented for simulations is

based on BSIM4, which addresses the MOSFET physical effects into sub-100nm regime.

TSMC provides a slightly modified MOSFET model, in order to better fit their transis-

tors behaviour.

This technology offers 9 metal layers, the last of which being thicker than the other and

therefore called Ultra Thick Metal (UTM). This layer allows designer to decrease the

parasitic resistance when lines are longer. Moreover, since this layer is the furthest from

the substrate, the parasitic capacitance to the bulk is as well minimized. Low resistance

and low capacitance make this layer the best candidate to realize inductors with.

1.3 Methods and Equipment

To design the ampilfier, Cadence Virtuoso has been used for both the schematic and

the layout steps. All the simulations have been performed with the integrated simulator

GoldenGate. The chip has been designed to be measured with the HP8510C newtwork

Chapter 1. Introduction 5

analyzer for what concerns the gain and the bandwidth. Linearity measurements are

to be done with the HP83650L sine generator and the Rohde&Schwarz FSU spectrum

analyzer.

Chapter 2

Design Specifications

Before starting with the amplifier design, goals have to be defined: the VGA spec-

ifications have been derived by the transceiver ones starting from the whole system

requirements. Several compromises have to be considered when designing any electronic

circuit: hints of theory required in order to understand where they come from will be

given.

During the work, some parameters have been considered as more important than others.

Linearity, bandwidth and gain range have been thought as primary goals and checked at

every design modification. On the other hand, other parameters have been less focused

on during the preliminary steps because, according to the VGA function, less impor-

tant. Once completed the VGA architecture, their values have been though simulated

and checked to be in an acceptable range for the system requirements.

Considering the input required at the stage following the VGA, i.e. the ADC when

speaking of the receiver chain, and according to the signal that the VGA will receive

from its previous stage, the needed gain range has been calculated. The mixer will feed

the amplifier a signal which is expected to vary from 15 mVp to 70 mVp while the signal

that must be put in input at the ADC should be of 125 mVp constant amplitude in

order to exploit its whole available input swing, that is to say the whole range of voltage

values that can be coded in a different discrete digital sequence. This requires the VGA

to be able to vary its gain from 5 to 18.5 dB. In the transmitter, a variable gain could be

used in order to irradiate different power levels. Typically, this is not made, as eventual

amplitude modulation is obtained thanks to other blocks. However, an adjustable gain

level could be exploited in order to compensate for the variations of the gains of the

following VGA blocks, in the different transmitters. The needed variable range for this

purpose is much smaller than the one required for the receiver chain.

6

Chapter 2. Design Specifications 7

The required bandwidth has been directly obtained by the IEEE standard instructions:

the communication channel exploits signals from 10 MHz to 2.16 GHz to carry the

information and therefore the VGA is needed to have bandwidth of more than 2 GHz.

Since the requirements for the VGA in the receiver chain are more strict and more

challenging to be satisfied, the design goals have been derived for this component. The

same amplifier in the transmitter chain will in fact be used, with the due modifications

that will be in the course this work highlighted.

Table 2.1 resumes the entire set of design goals for the receiver VGA.

Parameter Value

Gain [dB] 5 - 18.5

Bandwidth [GHz] > 2

OP1dB [dBm] −5

OIP3 [dBm] 5

Table 2.1: Receiver VGA design goals

Parameters such as the power consumption and the chip area were not part of the prior-

to-design specification: these values have been though minimized as much as possible.

The same way, the noise factor was not considered as a primary parameter to design

according with, because of some simple considerations: when in the trasmitter, the VGA

will receive by the DAC a wide signal with a good signal-to-noise ratio; on the other

hand, considering the receiver, the position of the VGA in the chain, as last element,

explains its non-critical role in the noise generation. In fact, when cascading several two-

port stages, the overall noise factor can be calculated thanks to Friis formula (Formula

2.1) which shows how the main contribute to the noise factor Ftot is due to the first

elements of the chain, as the other contributes are divided by the previous stages gain

G.

Ftot = F1 +F2 − 1

G1+F3 − 1

G1G2+ ...+

Fn − 1

G1G2...Gn−1(2.1)

Chapter 2. Design Specifications 8

Consequence of the Friis formula is the presence of a low-noise amplifier straight after

the antenna, in typical receivers architectures.

According to the system specifications, the VGAs are required to have both differential

inputs and outputs. The use of a differential architecture, instead than a single-ended

one, leads to several advantages: common mode noise is rejected and even-order har-

monics are suppressed. Moreover the signal swing is doubled for a given supply voltage.

Before starting to work on the design, literature has been scanned in order to analyse

the state-of-the-art adopted solutions that have been exploited to acheive performance

comparable or better than the goal-specified ones.

2.1 Bandwidth

As introduced in the previous chapter, the amplifier is required to have a large band-

width. This aspect has been one of the most challenging problems while designing the

VGA: in addition to the high-frequency problems already introduced, the lower limit of

the passband is required to be at least of 10 MHz which makes several of the RF-design

techniques unusable and complicates the design some more.

The communication channel is 2 GHz wide and therefore this value is the smallest

required value for the amplifier to be implemented in the transceiver. A deeper con-

sideration will make it clear how a 3 dB-bandwidth at the upper limit of the channel

is not advisable as a wide section of the functional signal will be attenuated and phase

distorted (Section 2.6). Therefore the amplifier has been designed to have a gain which

is as flat as possible in the entire range of frequencies it works at.

As well known from the theory, the gain of a common source amplifying stage is pro-

portional to the resistance seen at the output node (Formula 2.2). This node happens

to be the critical one in terms of bandwidth: the dominant pole frequency in the Bode

plot is function of this output resistance as well (Formula 2.3).

G = gm ·Rout (2.2)

fp =1

2πRoutC(2.3)

This inverse dependancy gives rise to a compromise that is well known to any amplifier

designer: higher the gain, lower the bandwidth.

Chapter 2. Design Specifications 9

At the output node, significative capacitance is seen as to the load capacitance, typically

a transistor gate, several parasitic capacitors are added. The total capacitance, together

with the high resistance seen at the same node generates a pole that is indeed located

around the GHz frequencies.

Techniques exist in order to reduce the parasitic capacitances: cascoding transistors will

avoid the Miller effect to amplify the differential pair capacitances. In addition, the use

of smaller transistors, both in the stage and for the next-stage differential pair, i.e. the

load, will push the pole toward higher frequencies.

For a given technology, working on capacitances cannot though solve the problem beyond

a certain extent: transistor sizes are chosen according to several other parameters and a

cascode solution could be ineffective due to the increased resistance seen at transistors

drains which will again lower the pole frequency.

Considering the output resistance, some optimization can be done as well: lowering this

resistance will in fact push the pole frequency to higher values, but a compensation for

the lower gain of the stage has to be found. Working on both resistances and capacitances

can lead to performant 2 GHz band simple amplifiers with still interesting gain levels

[16]. When willing to push the amplifiers performance, a very common approach consists

in cascading several amplifier stages: the gain, in dB, of the total network is in fact the

sum of the single stages ones. Thus the single stages can have a lower gain: if this is

acheived via a lower load resistance, a wider bandwith can be obtained.

Cherry-Hooper amplifiers exploit a different topology in order to lower the resistance

seen at the output node and to push the pole toward high frequencies [17]. Several

amplifiers in literature exploit modified versions of the Cherry-Hooper topology as a

base which to start from for high speed systems [13], [14], [23].

In this work, both the capacitive and the resistive load have been optimized, in order to

push the pole generated between the several stages as far as possible. Details of the used

solution will be presented in Chapter 3. Working on the pole frequency in this manner

is though not sufficient to reach bandwidths much broader than the required ones. In

fact, literature presents promising topologies that exploit other techniques in order to

acheive bandiwidths up to several GHz [8] - [15].

One of the techniques that have been used to extend the bandwidth consists in a multi-

stage amplifier that exploits a capacitive feedback in order to compensate the capacitance

responsable for the generation of the dominant pole [8]. With the capacitive neutral-

izazion configuration, the Miller effect is exploited to vary the capacitance seen at the

input of an amplifier that will be placed as load of another stage (Figure 2.1). In fact, if a

capacitive impedance Cp is connected in parallel to an amplifying stage, the capacitance

seen at the input of the stage is varied from its original value (Figure 2.1).

Chapter 2. Design Specifications 10

Figure 2.1: Miller capacitance

The resulting capacitance at the input node can be calculated and shown to be linked

to the gain of the amplifier A with a linear relation (Formula 2.4).

Cin,tot = Cin + (1−A) · Cp (2.4)

If the amplifier is a non-inverting one, the total capacitance at the input node Cin,tot is

then reduced and if the gain of the stage is large enough, a negative capacitive value,

that can be exploited to compensate the one seen at the previous stage output, can be

obtained.

As a drawback, because of the same effect, the capacitance at the output node is ampli-

fied. It is though possible to compensate Cout,tot thanks to a similar capacitive feedback

on the following stage. Also, this technique can be used to reduce the capacitive load at

the most critical node, at the cost of increasing it on another one, which, because of the

design could not give rise to a critcal pole. Since the negative capacitance rises at the

amplifier input node, this kind of feedback can be used to extend the bandwidth only

when using a cascade architecture.

Another way to reduce the capacitive load at the output node exploits the use of induc-

tors in order to compensate for the node reactance at the working frequency. Historically,

the use of inductive loads to generate a peak in the region close to the bandwidth edge,

extending it of a certain amount, has been studied and implemented [9], [10]. The cre-

ation of a parallel resonant circuit associated with the capacitance seen at the output

neutralizes it and results in a bandwidth broading. Inductive peaking techniques re-

quires careful design in order to extend the bandwidth without generating an high peak

close to the bandwidth edge and ruin the gain flatness.

In integrated technology, inductors become very expensive in terms of area consumption.

Moreover they are the most difficult components to be designed because of the strong

Chapter 2. Design Specifications 11

parasitics effects. In order to overcome inductors area drawbacks, the use of active in-

ductance elements has been proposed: some active load topologies are shown to act as

an inductive load in the high frequency region [11], [12].

2.1.1 Feedback Amplifiers

A very common solution that has been proposed in the past is the use of a feedback

chain. In a feedback amplifier part of the output signal is taken and fed at the input.

If the two signals are combined when in phase opposition, the feedback is said to be

negative. Because of this feedback, the amplitude of the signal entering the amplifier

is reduced. When creating this loop, the overall gain becomes dependent on both the

original amplifier gain, A0, and the feedback factor β, which depends on the feedback

topology (Formula 2.5).

Aloop =A(jω)

1 + βA(jω)(2.5)

Inserting in (2.5) the gain expression of an amplifier whose frequency behaviour is of

a high-pass filter characterized by a single pole, it is easily shown that the closed-loop

amplifier will show a lower gain (Formula 2.6), but a different cut-off frequency fcut

(Formula 2.7).

Aloop,DC =A0

(1 +A0β)(2.6)

fcut = f0,cut · (1 +A0β) (2.7)

The bandwidth can then be broadened at the cost of a reduced gain (Figure 2.2). Since

both the quantities vary of the same amount (1 +A0β), the Gain-Bandwidth product is

kept constant. This kind of feedback can be implemented thanks to a resistor networks

in a very easy way. With this implementation, the β factor will vary in a range from 0 to

1. A resistive feedback will though present some drawbacks. First of all, if a very wide

band is required, the amplifier stage has to be designed with a very high gain, since its

reduction is of a significative amount when compared to the extent of the consequent

bandwidth broadening. In addition, this kind of feedback will couple the DC operating

point at the input with the one at the output, which could be a problem according to

the amplifier topology. The use of a DC block is not suitable to solve this problem, as

Chapter 2. Design Specifications 12

Figure 2.2: Feedback

this will give rise to undesired high-pass active filters, resulting in a cut of the lower

limit of the bandwidth.

On the other hand, the use of an active feedback solves the problems of the resistive one

(Figure 2.3).

Figure 2.3: Active Feedback Block Scheme

This kind of feedback has been used in literature in the last years, with interesting results

[13], [14] , [15]. The way an active feedback works differs from the one of a resistive one.

Several ways to implement it exist, the simplest one being a common source transistor.

When the ouput signal is fed to the gate of the feedback transistor, its drain will follow

it with a reverse polarity, therefore creating a signal exploitable for a negative feedback.

However, this is a simplified view and it should be considered that this is true only for

low frequency signals. In fact, high frequency signals will accumulate a certain phase

delay while going through the feedback block and will not be therefore fed back in total

Chapter 2. Design Specifications 13

phase opposition. This frequency dependance of the active feedback network can be

exploited to extend the bandwidth. More details will be given in Chapter 3.

The use of an active feedback lets the designer solve the DC coupling problems rising

with a resistive network, since the input and the output of a common source amplifier

are DC decoupled.

2.2 Variable Gain

In the past years several approaches have been reported in literature in order to acheive

variable gain stages. The different techniques present advantages and drawbacks and

not all of them can be used together with a given bandwidth extension method.

A simple mathematical derivation can be made in order to understand on what is pos-

sible to work when willing to vary the amplifier gain. As already said, the DC gain

of an amplifier stage is proportional to both the output resistance and the transisor

transconductance (Formula 2.8).

G = gm ·Rout (2.8)

The transconductance gm is not a constant but depends on several parameters, both

technology, i.e. gate capacitance and carriers mobility, and design dependant ones, it

is to say the transistor dimensions. It is clear that once the design is chosen and the

circuit realized, no one of those parameters can be varied and therefore none of them

can be exploited in order to obtain a variable gain.

gm shows a dependency on the current that is flowing in the transistor channel at the

biasing point. This dependency is not fixed and changes according to the transistor

working region: when the voltage on a transistor gate reaches values around the threshold

one, the channel begins to be created and the transistor works in weak inversion (W.I.)

regime. In this regime, the gate voltage is still not high enough to attract a large amount

of inversion carriers at the interface, but depletion of the majority carriers around the

oxide surface is already acheived. As the gate voltage is increased the channel is fully

created and the transistor is said to be in strong inversion (S.I.). When the transistor

moves from one regime to the other, its transconductance dependency on the current

varies: an exact mathematical fit for this transition is not given, but a linear to square

root link with ID is shown when going from weak inversion toward strong inversion.

Chapter 2. Design Specifications 14

Inserting in (2.8) the transconductance expressions for both regimes, new expressions

for the gain are obtained (Formulas 2.9 - 2.10).

G =ID

n · UT·Rout (W.I.) (2.9)

G =

√2β · IDn

·Rout (S.I.) (2.10)

Formulas show all the parameters that can be exploited to vary the gain: the bias current

ID as well as the output resistance Rout. Moreover when varying the gate biasing voltage

the gain dependancy on the biasing current will change from one expression to the other.

Examples of gain variation by gate biasing voltage can be found in literature [16]. A more

common approach consist though on working on the output resistance. More than one

way to vary the load impedance exist, however resistors in integrated technologies are

usually implemented with active elements, i.e. MOSFETs, because of smaller process

tolerances and the lower area requirements they exhibit with respect to their passive

counterpart. Using a MOSFET as a variable resistor has though a major drawback:

non-linearities are introduced. In fact, the I-V characteristic of a MOSFET is non-linear

and can be linearized to emulate a variable but Ohmic behaviour only when in triode

region.

Other techniques to obtain variable gain stages exist. For example, adding a degenera-

tion resistance will affect the gain level as well (Figure 2.4).

Figure 2.4: Resistive degenerated amplifier

Indeed, when a degeneration resistance is added, the gain expression becomes:

Chapter 2. Design Specifications 15

G =gm ·Rout

1 + gm ·Rdeg(2.11)

Degeneration resistances are usually implemented because of the increased stage linearity

and because of the stabilization the gain, due to the weaker dependency on the transistors

transconductance. If Rdeg is implemented as a variable resistor, the gain can be varied

as well. It should be noticed that with this technique the gain can be only reduced

from the value the stage would have withouth Rdeg. Therefore this solution should be

implemented on high gain stages that could give rise to problems in terms of bandwidth.

Variable feedback networks can be used as well. As stated in the previous paragraph,

feedback nets extend the bandwidth at the cost of a reduced gain: connecting a feedback

will indeed vary the output resistance, changing it from the open loop value. As a

drawback, a variable feedback network will result in a variable bandwidth according to

the gain level. Since a constant badnwidth for all the gain levels is usually preferrable,

this tecnhinque is usually discarded.

A last solution that has been investigated consists in the employ of several fixed gain

stages that can be included or excluded in the amplifier chain by switches, driven by a

digital controller. Examples can be found in literature, where this architecture has been

exploited in order to make the gain vary in discrete steps and not in a continuous way

[7], [18]. In [18] the use of coarse and fine gain stages has been implemented in order to

obtain a gain range from 0 to 45 dB with a 3dB step.

The digital controller can be used not only to include or exclude amplifier stages, but as

well to select the number of passive resistors that can be connected at one node, avoiding

the use of variable resistances. When using this technique, the introduction of the mosfet

due non-linearities will be avoided and a very linear amplifier can be obtained.

2.3 Impedance Matching

As stated in the previous chapter, two VGA types will be needed. One of them will be

placed in the receiver chain, while the second one in the trasmitter one. According to the

VGA position, the amplifier will see different impedances at its inputs and outputs and

therefore the two of them could require additional hardware to be properly interfaced

(Figure 2.5). The chosen ADC has a low input impedance, i.e. 50 Ω. On the other side,

considering the transmitter, the upconverter will offer high impedance at its inputs.

Speaking of the VGA inputs, the same issue occurs: as the output impedances of the

Chapter 2. Design Specifications 16

previous stages changes from high to low in the two chains, the input impedance of the

amplifier has to be matched.

(a)

(b)

Figure 2.5: Different impedance configurations: (a) receiver and (b) transmitter chain

Although all these considerations have been taken in account while designing the am-

plifier, for measurements purposes both the input and the output impedances have to

be matched at 50 Ω.

Radio frequency designers are very used to impedance matching problems, as they be-

come more and more critical while going toward higher frequencies. Typical approaches

to match impedances include LC networks, where impedance resonances are exploited

to match at a particular frequency. As already stated, inductors can become a trouble-

some component to be used in integrated technology: in fact, in addition to parasitics

problems, low frequency resonating inductors become prohibitive in terms of area re-

quirements and therefore not feasible. Furthermore, resonating circuits are used to

match impedances at specific frequencies and are not easily exploitable for broadband

matching.

To match over a 2 GHz span at relative low frequencies, resistive feedbacks can be used:

when connecting resistors to the VGA terminals the seen impedance is changed and

matching can be acheived. The feedback resistor values will anyway affect as well the

amplifier performance and all those effects should be considered when matching with

this technique.

Buffer stages are one of the possible and most exploited solutions. This is to say that

an additional stage, able to properly load the wanted impedance, is put at the interface

with the circuit, preventing an unproper loading and avoiding interference with the

Chapter 2. Design Specifications 17

desired operation. Voltage buffers are ideally required to have unity gain at all the

passband frequencies and very high linearity. Common Drain (CD) configurations are

usually chosen as buffer stages when in the need to match to low impedances. This is

thanks to the fact that the impedance seen through the transistor source is much lower

than the one seen through the drain. CD topologies present though some drawbacks:

while consuming a large amount of current, the signal gets attenuated if loaded on a

low resistance, i.e. 50 Ω,. This is because the voltage gain of a CD stage has an upper

limit at 1, that is to say that ideally a CD topology can adapt the impedance without

affecting the signal amplitude. This ideal limit is more approached the more the load

resistance RL is high (Formula 2.12).

Av =gmRL

gmRL + 1(2.12)

In case of a 50 Ω load resistance the common drain will then attenuate. Since the larger

the attenuation of the buffer, the bigger the needed signal swing at the previous stage

output, this issue has to be carefully handled while designing.

The adopted soluton will be shown in the Chapter 3 where the VGA schematic will be

discussed in detail.

2.4 Linearity

Linearity is one of the most important aspect of an amplifier: if the signal in the passband

gets amplified but too much distorted, it could be of no use as no more processable.

Furthermore VGA linearity will affect the whole system performance.

Starting from the maximum expected power at the antenna, the requirements in terms

of linearity for the several blocks have been calculated. Still, since the amplifier is at the

end of the receiver chain, its estimated properties depend on the ones of the different

preceding stages. These stages designs have not yet been finalized and therefore an

accurate estimation is difficult. This explains why the required linearity properties have

been obtained starting from the digital converters side.

Regarding linearity, two parameters are usually exploited to quantify the amplifier per-

formance: the large-signal 1 dB compression point (P1dB) and the small-signal third-

order intercept point (IP3).

P1dB is directly related to the signal compression and usually starts becoming an issue

when large signal swings are to be handled.

Chapter 2. Design Specifications 18

A 250 mVpp single-ended signal swing is the largest signal that can be correctly processed

by the ADC, without saturating it. As anticipied in Section 2.3, if a buffer stage, such

as CD, is exploited to adapt the impedance, it must be taken in account that, due to its

attenuation, an even larger signal has to be handled. Speaking of the transmitter, the

DAC will feed at the amplifier inputs a wide signal that should not cause compression

distortion. However, the used DAC has a programmable output current. In order to

grant the proper working, the amplifier should at least be able to process the signal

coming from the converter with the smallest available amplitude, i.e. 150 mVp on the

single signal.

In order to assure proper working, large care has to be put when choosing the working

points, i.e. bias currents and transistor dimensions, since it is around their value that

the signal will swing, both at the inputs and at the outputs (Figure 2.6).

Figure 2.6: Amplifier signal swings

The compression of the gain concerns the input of every amplifier stage: for the transistor

not to turn off, the threshold voltage must be granted at its gate. Therefore, considering

the topology of Figure 2.6, VB,in > Vth. The threshold voltage should be assured not

only while in bias condition, but also when the signal is applied, that is to say when

Vgs 6= VB,in. In particular, when the signal gets its minimal value the transistor has to

be checked not to go in subthreshold regime: the condition to be assured is therefore

Vmin,in > Vth. On the other hand, if Vgs becomes too high when reaching its maximum,

the transisor could offer such a small channel resistance not to grant its self channel

saturation anymore.

Similar considerations can be made at the output node, where the critical situation is

reached when Vds assumes its minimal value Vmin,out that has to be larger than the

Chapter 2. Design Specifications 19

transistor saturation voltage Vds,sat not to bring the transistor in the triode regime.

When considering more complex topologies, with biasing structures and active loads,

the issue becomes more problematic as each component requires a part of the total

voltage headroom in order to properly function. In designs where the supply voltage is

low, cascoding becomes an unexploitable technique: when handling large signals, non-

linearity effects appear and the gain gets compressed.

P1dB simulations have been made to check the proper amplifier working.

Careful transistor dimensioning and bias point choice let the designer handle pretty

ample signals, up to a certain amplitude. When willing to overcome the described

limitations, less common amplifier topologies can be exploited: in literature other ar-

chitectures, known as push-pull amplifiers, have been proposed and seem to be able

to handle almost rail to rail signals. An interesting study on the topic, enlighting the

advantages and the drawbacks, has been developed in the last year [19].

Linearity issues do not rise only from compression, but as well from small signal distor-

tion. In fact, amplifiers are linear elements just in first approximation. It is possible

to model the amplifier non-linearities with a polynomial expansion. Exploiting the

equivalence of (2.15), it is easy to show with few mathematical steps that, if a signal

x(t) = X1cos(2πf1t) is fed to an amplifier whose polynomial characteristic shows cubic

terms (Formula 2.13), signals at three times the input frequency will be seen at the stage

output.

y = k0 + k1x+ k3x3 + ... (2.13)

−→ y(t) = k0 + k1 ·X1cos(2πf1t) + k3 ·X31cos

3(2πf1t) (2.14)

with cos3(x) =3

4cos(x) +

1

4cos(3x) (2.15)

As these components grow with the cube of the input signal amplitude, increasing the

input power will degrade the ratio between the first order and the third order sig-

nals power. In addition to third harmonics generation, if a multi-tone signal x(t) =

X1cos(2πf1t) +X2cos(2πf2t) is fed to the amplifier, intermodulation products rise and

signals at frequencies that are sum or difference of f1 and f2 can be observed. If the

amplifier shows poor linearity, the wanted signal could be too distorted at the work

point because of the other frequency components.

Input IP3 (IIP3) measures the signal power that has to be fed in input in order to

obtain an output power of equal magnitude for both first and third order signals. As at

Chapter 2. Design Specifications 20

high input power the output of the amplifier will eventually saturate, the IIP3 is ob-

tained via an extrapolation and is therefore a theoretical parameter (Figure 2.7). Even

though theorethical, it can be used to succesfully quantify linearity VGA performance.

Not only third order harmonics gets generated due to the non-linearities, but second

Figure 2.7: Third order intercept point

and higher order ones as well. Third order harmonics constitute anyway the main issue

because of the techniques that exist and are commonly used to suppress the even-order

harmonics, such as differential designs.

Concerning amplifiers, it is possible to demonstrate that the IP3 has a link with the

compression point: the first one is 10 dBm higher that the P1dB. Starting from the ADC

requirements, the needed input IP3 values for the VGA in the different gain configura-

tions has been obtained. A value larger than -13 dBm has to be achevied when in high

gain setting, while 0 dBm is the minimum that has to be obtained when in low gain

level.

When small-signal linearity requirements are not met, techniques to boost it exist: in-

creasing the transistors gate bias and lowering the gain, as well as using larger flowing

currents, are commonly exploited tricks.

2.5 Stability

Stability is a big issue for any amplifier design. When dealing with feedback amplifiers,

both resistive and active, phase and gain margin are usually considered in order to assure

Chapter 2. Design Specifications 21

that the amplifying block will not start to oscillate because of the feedback network.

When speaking of RF-VGAs, greater care should be put during design and when carrying

on simulations to guarantee stability at all the gain levels. In fact, going toward radio

frequencies, other effects such as strong signal cross-coupling could lead the circuit to

the instability.

The understanding of stability issues involve not trivial theory and calculations that are

not to be presented in this work. Some hints are anyway to be given in order to catch

how the stability has been tested for the VGA.

Figure 2.8: two-ports network

Considering a two-ports with both load and source connected to a passive network

(Figure 2.8), the circuit is granted not to oscillate, therefore to be stable, if the signal

reflected at the two ports meet the conditions of formula (2.16), that is to say that the

reflected power will not be larger than the incident one at the same port.

|Γin| < 1 and |Γout| < 1 (2.16)

This condition is equivalent to state that the admittance of either port remains positive

for any arbitrary passive termination on the other port. In this case one speak of

unconditional stability. If there are specific terminations at one port that can brake the

condition, one speaks of conditional stability. Unconditional stability is advisable when

designing any circuit because of the larger margin of safety that it grants, as well as for

the easier techniques that exist to check it.

It is possible to map on the complex plane, for example in the ΓL one, the values for

which |Γin| = 1, that is to say the limit condition for the circuit to be stable. Similarly,

it is possible to map on the ΓS plane the values for which |Γout| = 1. This mapping will

lead to the trace of circles that will divide the regions of instability from the others. If

|S11| < 1 the stability regions lie outside these circles and therefore, in order to assure

unconditional stability, these circles should lie entirely outside the Smith chart (Figure

2.9).

Chapter 2. Design Specifications 22

Figure 2.9: Stability regions in the ΓL plane

Calculations of stability circles center and radius are difficult and prone to errors. Be-

cause of the not trivial theory beneath the understanding of stability issues, a practical

and simple way to check whether the stage is unconditionally stable consists in the use

of S-matrix-derived parameters. Both Rollett and Edwards proposed two different pa-

rameters that can be used, whose derivation can be made for all the linear two-ports

networks [20],[21].

In this work, Edwards µ parameter is preferred with respect to Rollett k one as the first

one has a direct geometrical meaning, measuring how far from the instability circles the

center of the Smith chart is. Therefore a two-ports with larger µ parameter will be more

stable than one with a smaller µ. Edwards identifies two parameters, µ and µ′: the first

one defines the minimum distance between the center of the unit Smith chart and the

unstable region in the ΓL plane, while the second one refers to the ΓS plane. Therefore,

µ > 1 and µ′ > 1 will assure that no impedance seen at both the two-ports terminations

will make it oscillate, that is to say that the circuit is unconditionally stable.

2.6 Group Delay

Signal phase distortion is another amplifier property that should be taken in account.

The origin of this distortion is due to a dependency of the transit time of a signal within

a block on its frequency.

Phase distortion shows up when going closer to zeros or poles in the Bode plot. In fact,

Chapter 2. Design Specifications 23

the zero/pole frequencies can be defined as those frequency values for which the phase

of the gain changes of 45. Therefore, a broader bandwidth will usually lower the phase

distortion in a given range of frequencies. For example, when a 3 dB bandwidth of 2

Ghz is obtained, signals at the edge of the band will experience a large phase distortion.

If the bandwidth is increased up to several GHz, the phase distortion for the 2 GHz

signal will be reduced. This emphasizes the need of a VGA with flat gain characteristics

as broad as possible.

Equalizers exist in order to reduce the phase distortion. Therefore phase distortion is

acceptable in amplifier stages in a certain range, as long as it does not get so large not

to be recoverable anymore by following stages.

Chapter 3

Amplifier Design

3.1 VGA Architecture

In the previous chapter the goals have been established and a review on the existing

literature has been presented.

Designing the VGA requires as first steps the choice of the topology and therefore

the selection of literature solutions that best acheive the aim, considering both the

advantages and the limitations of each of them. Among the reasons that led to the

final topology, one that deserve to be mentioned is the design semplicity: solutions

can be found in literature that exploit several techniques together in order to acheive

good performances [15]. This approach could though result in an over-complicated

design because of the several effects that have to be studied, first singularly and then

all together, in order to fully understand the overall working. Moreover as the design

becomes more complex, the number of parameters that has to be optimized before the

chip production quickly increases.

Before the choice of the final achitechture, several solutions have been investigated.

Because of the large output swing needed, in a first time a push-pull amplifier, like

the one proposed by Keehr in [19], has been designed and simulated. Due to the non-

standard achitecture problems rised: the chosen topology has been proved to be too

sensible to load variations. In addition, push-pull amplifiers with variable gain cannot

be found in literature and their implementation is not trivial. Therefore, a more classical

topology with cascaded amplifying blocks has been selected.

Concerning the bandwidth extension techniques, inductive peaking was discarded in the

first steps as it did not look as appealing as other technique, mostly due to the mentioned

drawbacks (Section 2.1).

24

Chapter 3. Amplifier Design 25

Cascoded stages were then designed and simulated. Eventually, their use has been

discarded: Miller capacitance amplification becomes in fact more critical when the gain

of the stage is high. Since low-gain wide-band stages were to be designed, no large

benefit was obtained when cascoding. The large signal handling requirements became

then the reason which casoding implementation was avoided for.

As next trial, capacitive feedback networks to obtain negative capacitance compensation,

as proposed in [8], were used. Because of the use of inverting stages, one single-ended

signal was fed to the other branch. Thanks to this cross-feedback technique, a bandwidth

broadening was successfully simulated. The use of this kind of feedback in integrated

circuits requires though a very precise tuning of a small capacitors (≈ fF ) in order

to obtain the desired effects. Even more important than that, stability simulations

were performed and it was shown that the circuit was not unconditionally stable. Even

though a possible solution to these problems is proposed in literature [15], the use of the

capacitve feedback was discarded in favor of other more appealing and reliable topologies.

The chosen final achitecture is shown in Figure 3.1.

Figure 3.1: Chosen VGA topology

The whole VGA is composed by 8 amplifying cascaded stages plus an output buffer.

The number of stages has been chosen during the final steps of the design in order to

satisfy the gain requirements without exceeding in the required DC current. In fact,

cascading the same identical topology will allow wider gain range and higher reacheable

gain levels, but at cost of larger area and power consumption.

Two variable attenuation stages at the beginning of the chain are used to lower the

amplitude of too large incoming signals. Following variable and fixed gain stages are used

in order to bring the signal to the desired output amplitude. Two active feedback blocks

are exploited to let high frequency signals to be in the passband. An active feedback

has been chosen after some trials with a resistive one: the drawbacks of the resistive

feedback have been proved not to be easily solveable (Section (2.1.1)). Moreover, the

Chapter 3. Amplifier Design 26

active implementation seems to be capable of larger bandwidth broadening with respect

to the consequent gain loss, with respect to the passive counterpart.

The need of fixed gain stages beneath the feedback chains, rises from the active feedback

working principle and will be justified in Section (3.1.3).

Last, the buffer stage, as well as the 50 Ω resistors at the input, are used to lower

the impedance seen from the VGA terminations. Adapting the impedances with this

amplifier topology offers the major advantage of a versatile architecture: adding or

removing the border stages will vary the terminations impedances from low to high,

without affecting the core of the amplifier. In fact, if the output impedance is required

to be high, the removal of the output stage will improve the VGA gain performance

of a small amount (Section (2.3)). At the amplifier inputs, when removing the input

resistances, the seen impedance will become much higher and no change in the VGA

performance can be observed. This adaptibility lets the amplifier to be designed just

once in order for its performance to be tested, avoiding the need of the different designs

for the transmitter and the receiver chains.

3.1.1 Fixed Gain Stages

Fixed gain stages consist in a differential pair, with a common biasing tansistor and a

resistive load (Figure 3.2).

Figure 3.2: Fixed gain amplifier topology

Chapter 3. Amplifier Design 27

A resistive load, in these stages as well as in the variable gain ones, has been preferred

with respect to an active one. The choice is due to the linearity issues active loads could

introduce if their saturation voltage is not granted: because of the required output swing,

which increases while moving through the amplifier elements, this kind of load has been

simulated not to be the best candidate. On the other hand, when little currents are

handled, the output node can reach much higher values if not too high resistors are used

as load. In fact, the resistive voltage drop V = R · I can be appreciably smaller than the

VDD − Vds,sat limit imposed by active loads. Thanks to the resistive load, the high DC

output voltage of each block has been exploited to bias the following stage, avoiding the

use of intermediate DC blocks.

The fixed gain amplifiers have been designed with a gain of about 7 dB and, thanks to

a low resistive load of 220 Ω and small transistors, i.e. small capacitances, a high cutoff

frequency at the output node is simulated (Section (2.1)): 1dB-bandwith of 3 GHz is

obtained when the fixed-gain amplifier is loaded with an identical stage.

The power consumption of these stages is of about 2.5 mW, due to a bias current of

about 1.05 mA on each transistor of the differential pair. Little variations from this

value are shown, depending on the stage position: minor modifications have been done

in the different fixed gain stages in order to adjust the biasing voltages at the different

nodes at the optimal value.

3.1.2 Variable Gain Stages

As presented in the previous chapter, several techniques to vary the gain exist (Section

(2.2)). The chosen one consists in varying the load resistance: most of the other discussed

techniques, such as working point variations or variable feedback networks, have been

discarded because of their major drawback of varying the amplifier performace according

to the gain set level. In fact, because of the strict bounds due to the large-signal handling,

the DC working points of the different blocks should be changed with great care in order

to assure satisfying linearity in all the configurations. Varying the gain with a variable

feedback network will have a great impact on the amplifier bandwidth for the reasons

that have been previously explained.

Constant VGA performance at each gain level are advisable in most the situations and

a variable load can lead to good behaviour in these terms, when well designed.

Digitally controlled amplifiers have been as well excluded because of the additional area

required by the controller as well as the resistors array, if implemented. Moreover the

design would have become more complex because of the digital parts.

Chapter 3. Amplifier Design 28

Figure 3.3: Variable gain amplifier schematic

The variable gain stages have been designed starting from the fixed gain ones, adding

a PMOS in parallel to the load resistor (Figure 3.3). Because of the high voltage value

at the output node, this transistor will never reach the saturation: when its Vsg is lower

than the threshold value, the current coming from the biasing transistor will entirely

flow in the resistor, giving rise to a potential drop at its nodes, as well as at the PMOS

ones, which has be designed to be always lower than 100 mV. When a larger Vsg is put

on the PMOS, current can flow through it, reducing the amout of current that flows in

the resistor, thus further decreasing the value of the PMOS Vsd. The PMOS is therefore

always working in triode region, i.e. far from the saturation regime. In this region the

active element acts, in first approximation, as an Ohmic component, showing a linear

resistive behaviour.

In order to use the PMOS as a resistor, it has to be assured that it will not reach the

saturation even when the signal is applied, i.e. Vsd < Vsd,sat even when the output node

reaches its lower value. In fact, this condition is not fully satisfying as, just approaching

the saturation regime, the I-V characteristic of the transistor becomes non-linear (Figure

3.4).

Appreciable linearity can be observed when the PMOS Vsd is lower than a certain value.

This value is not constant, but varies according to the voltage applied on the transisor

gate. When higher Vsg is applied, the output resistance of the stage is lowered, therefore

lower gain is expected. In this configuration, the source-drain voltage that can be applied

at the PMOS terminals and assure a linear behaviour is wider, reaching values larger

Chapter 3. Amplifier Design 29

Figure 3.4: PMOS I-V characteristic curves

than 200 mV. Lower linearity is expected for high gain configurations where the limits

in terms of output swing become stricter. It is therefore clear that, with this kind of

architecture, variable-gain stages are unable to handle very large signals. This justiffies

the presence of the attenuation stages that have been put at the beginning of the whole

amplifier chain: handling small signals will preserve the signal from be distorted. On

the other hand, the stages that will handle the largest signals, i.e. the last ones, are

fixed-gain ones.

This variable resistors technique has been exploited in all the four VGA stages. Though,

because of different design parameters, i.e. PMOS sizes and resistors value, the first two

VGA of the chain can vary their gain in a range from 2 to −13 dB, while the other two

from 0.5 to 6.8 dB. The first two amplifiers are thus exploited as attenuation stages,

while the other two are used as gain stages.

In fact, using larger PMOS will increase the maximal conductance value that it can offer,

therefore letting the tunable gain range of the single stage become wider toward smaller

values. The upper limit of the gain is instead not linked to these transistors dimensions,

but only to the resistors values. The final dimensioning of the different PMOS has been

made considering these effects, as well as the parasitic capacitance that a wider PMOS

would have introduced and its consequences on the overall bandwidth.

The biasing current flowing in each transistor of the differential pair is close to 500 µA

for the attenuation stages and to 3 mA for the gain stages. In fact, the difference in the

gain levels mostly rises from the difference in the bias current. The power consumption

Chapter 3. Amplifier Design 30

of the attenuator blocks is then simulated to be 1.2 mW. The gain stages consume 7.8

mW.

3.1.3 Active Feedback

The feedback working principle has been already explained in the previous chapter, but

will be here covered in larger details.

Figure 3.5: Feedback block schematic

In order to decouple the DC a simple common source configuration has been used (Figure

3.5): the stage is designed in order to use the output resistance of the stage whom it

is connected at as its load. This stage is not a gain one, though, as explained, the

performance of the whole loop will be affected by the feedback gain (Section (2.1.1)).

In order to obtain a low gain, these stages have been designed with small transistors

dimensions and low biasing current. Moreover, to lower the gain some more, these stage

have been resistively degenerated. In fact, the resistive degeneration let the transistor

to be designed with larger dimensions, without increasing the gain. Larger transistors

and resistive degeneration have been preferred because of the smaller impact of process

fluctuations on larger structures.

To better understand how the feedback works, Figure (3.6) shows the Bode plot of the

stage at whose output the feeback output is attached.

When the feedback is connected, the signal at the variable gain stage output node gets

combined. This is why the gain of this stage, which by itself could vary from 0.5 to 6.8

Chapter 3. Amplifier Design 31

Figure 3.6: Active feedback effect

dB, is here shown to be significantly lower at low frequencies.

The plot shows a peak at high frequencies. In fact, at GHz frequencies signals experi-

ence a certain delay while travelling through the feedback loop. Because of this delay,

the combined signal is not anymore combined in total phase opposition and, as result,

signals are not completely subtracted, but a portion of them starts to be summed. With

the designed feedback network, signals at 8 GHz are combined in phase and they get

completely summed: the peak in the plot is observed. This peak will vary its amplitude

as well as its frequency according to several parameters. The peak frequency can be

slightly shifted by designing various feedback stages or connecting them over a different

number of fixed-gain amplifiers. The peak height is instead function of the amplitude

of the signals that gets combined, that is to say, it depends on the gain levels of all the

stages forming the loop, as well as on the gain of its preceeding stage. This explains

why fixed-gain stages have been used in the loop, instead of variable-gain ones: in fact,

using variable-gain stages would have led to a variable peak amplitude, resulting in a

variable bandwidth according to the gain level in the whole VGA.

This high peak compensates the lowering of the gain due to the frequency behaviour of

the other stages of the amplifier chain and, when the two effects are well balanced, it is

possible to acheive a flat bandwidth up to several GHz.

As well as the peak amplitude, the different gain levels affect the gain at low frequencies.

Transistor dimensions as well as the bias current values have been chosen in order to

optimize the overall frequency behaviour.

Chapter 3. Amplifier Design 32

Since no high gain is needed for the feedback stage, the current can be kept at a low

value: 300 µA is flowing in each transistor.

It is here reminded that feedbacks, especially when positive, have to be handled very

carefully concerning the stability aspects: in order to assure unconditional stability,

simulations have been made and results will be presented in next section.

3.1.4 Output Buffer

The output buffer has been designed with the same topology of a fixed gain stage (Figure

3.7).

Figure 3.7: Buffer topology

This stage has been included in the taped out system because of measurement purposes:

it will be removed in the transmitter amplifier, but however left in the receiver one.

First versions of the circuit implemented a common-drain buffer. Due to the large at-

tenuation values rising from this topology, another solution has been chosen: a common-

source stage with small resistive load and high current is used to drive the low output

impedance and obtain the desired output swing at its nodes. The cost of this impedance

transformation is an attenuation of about 1.5 dB over the whole bandwidth, which is a

better value compared to the one simulated with the common-drain.

Chapter 3. Amplifier Design 33

Because of the very large signal swing at the buffer input, i.e. about 150 mVp, care was

put while designing this stage not to bring the differential pair in subthreshold regime

and not to cause the signal to be distorted. 250 mVpp output swing has been obtained

with no significant distortion, but this stage keeps being the limiting one if larger signals

are to be handled.

Since this stage is the power one, larger power consumption was expected while designing

it: indeed to obtain such a large voltage swing on a small resitor, large current values

are required. The final version of the buffer requires 8.6 mA for each of the signal chains

to work properly and therefore consumes in total about 21 mW.

3.1.5 Additional Components

Additional blocks have been designed in order to assure the circuit to work properly.

Standard current mirrors to bias every block were required and have been implemented.

Resistively loaded NMOS mirrors have been designed (Figure 3.8).

Figure 3.8: Current mirror schematic

Thanks to different transistors ratios the desired current value has been mirrored in the

different blocks of the amplifier. While designing the biasing structures, care has been

put in obtaining the as low as possible saturation voltage for these transistors. In fact, a

lower VDS,sat for these components will let the output nodes reach lower voltage values,

without ending in linearity problems.

Impedance matching at the amplifier input is obtained thanks to two passive resistors

linked toward ground. As they are placed between the DC block and the signal generator,

no DC current will flow into them and therefore no DC power will be dissipated. Thanks

Chapter 3. Amplifier Design 34

to this simple matching technique the proper signal swing at the input will be obtained

when the measurement system, with an output impedance of 50 Ω, will be connected.

A more interesting stage that was required in order to correctly bias the amplifying

stages, is the DC block. DC blocks, even if very widely used and well known, can

become critical to be designed in integrated technology, when low frequencies signals

are required to be in the passband. This is because of the cut-off frequency of a high

pass filter, which is inversionally proportional to both the resistor and the capacitor used

to implement it (Formula 3.1).

fcut =1

2π ·RC(3.1)

In this work this frequency is required to be lower than 10 MHz, not to cut part of the

signal containing the information. To obtain such a low cut-off frequency, either very

large R or very large capacitance values are required. As big capacitors are extremely

area consuming, at first the system was thought not to implement any DC block, except