Riassunto Rete Vi sono dunque due ingressi (X1,X2) e ununica uscita; X1 e X2 non cambiano mai...

-

Upload

rodolfo-chiari -

Category

Documents

-

view

215 -

download

0

Transcript of Riassunto Rete Vi sono dunque due ingressi (X1,X2) e ununica uscita; X1 e X2 non cambiano mai...

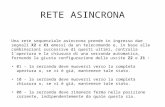

Riassunto Rete

• Vi sono dunque due ingressi (X1,X2) e un’unica uscita;

• X1 e X2 non cambiano mai contemporaneamente

• L’uscita va a 1 se viene rispettata la combinazione:00 - 01 - 00 – 10Altrimenti permane a 0

Codice VHDL• Nel codice si è inserito un Reset che si è

rivelato necessario per il corretto funzionamento della rete

• Tale reset ha la funzione di inizializzare i valori della rete a 0

• Nella simulazione Post-Route senza tale reset alcuni valori rimangono indefiniti o sconosciuti per tutta la durata della simulazione

Diagramma degli Stati (Moore)

A,0

00 01 00 10

B,0 C,0 E,1

F,0

D,0

10,01 00 01 00 10

10

00

11

1101,10

11

11

01

Tabella Stati X1,X0Stati

00 01 11 10 Z

A B A F A 0

B B C ---- A 0

C D C F ---- 0

D D A ---- E 0

E B ---- F E 1

F ---- A F A 0

Notiamo come X1,X0 non variano mai contemporaneamente e ciò causi delle indifferenze

Compatibilità fra stati

Abbiamo riscontrato solo la compatibilità fra A e F [A,F]Questa rappresenta una classe massima di compatibilità. Insieme alle classi massime [B], [C], [D], [E] otteniamo copertura e chiusura

Assegnazione

• [A,F] α

• [B] β

• [C] γ

• [D] δ

• [E] ε

X1,X0

Stati

00 01 11 10 Z

α β α α α 0

β β γ ---- α 0

γ δ γ α ---- 0

δ δ α ---- ε 0

ε β ---- α ε 1

Codifica X1,X0

Y2,Y1,Y0

00 01 11 10 Z

α 000 001 000 000 000 0

β 001 001 011 ---- 000 0

γ 011 010 011 000 ---- 0

δ 010 010 000 ---- 100 0

ε 100 001 ---- 000 100 1

In Rosso sono evidenziate le corse critiche. Tali corse sono risolte nella slide successiva.

Dopo aver risolto le corse critiche X1,X0

Y1,Y0

00 01 11 10 Z

00 001 000 000 000 0

01 001 011 000 000 0

11 010 011 001 --- 0

10 010 000 --- 110 0

X1,X0

Y1,Y0

00 01 11 10 Z

00 000 --- 000 100 1

01 --- --- --- --- ---

11 --- --- --- --- ---

10 --- --- --- 100 ---

Y2 = 0 Y2 = 1

Z = Y2 Y2 = Y1X1!X0 + Y2X1!X0 = X1!X0(Y1 + Y2);Y1 = Y0!X1X0 + !Y2Y1!X0;Y0 = Y1Y0X0 + !Y1Y0!X1 + !Y2!X1!X0!Y1 = !X1!Y1(Y0 + !Y2!X0) + Y1X0Y0;

VHDL

VHDL

VHDL

Codice Simulazione

Codice Simulazione

Codice Simulazione

Codice Simulazione

Simulazione Behavioral

Note …

• Nella simulazione Behavioral possiamo vedere il comportamento della rete

• Notiamo che l’uscita va a 1 precisamente nel momento in cui la combinazione arriva al suo termine (10)

• Vediamo ora i ritardi introdotti dalla tecnologia…

Simulazione Post-Route (1)

Simulazione Post-Route (2)

Note …

• Notiamo immediatamente di come l’uscita sia in ritardo rispetto alla simulazione Behavioral

• Osserviamo infatti che a seconda della velocità scelta per la tecnologia, sussistono dei ritardi di qualche ns