Progettazionedellalogicadi matchingdellamemoria ... lacella SRAM asei transistori, CRead contiene...

Transcript of Progettazionedellalogicadi matchingdellamemoria ... lacella SRAM asei transistori, CRead contiene...

Corso di Laurea in Fisica

Progettazione della logica di

matching della memoria

associativa del FastTracker per

l’upgrade di ATLAS

Relatore: Prof. Valentino Liberali

Correlatore: Dott. Alberto Stabile

Tesi di laurea di:

Luca Frontini

Matr. n. 743037

Codice PACS: 85.40.-e

Anno Accademico 2010 - 2011

Indice

1 Introduzione 51.1 Memoria associativa . . . . . . . . . . . . . . . . . . . . . . . 61.2 Circuito proposto . . . . . . . . . . . . . . . . . . . . . . . . . 7

2 AMchip04 92.1 Problematiche . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3 Layer singolo 113.1 Schema del circuito . . . . . . . . . . . . . . . . . . . . . . . . 11

3.1.1 Cella XORAM . . . . . . . . . . . . . . . . . . . . . . 133.1.1.1 Cella SRAM a sei transistori . . . . . . . . . 133.1.1.2 Circuito di lettura/confronto . . . . . . . . . 14

3.1.2 Logica combinatoria . . . . . . . . . . . . . . . . . . . 153.1.2.1 Scelta del circuito 3× 6 . . . . . . . . . . . . 16

3.2 Layout del circuito . . . . . . . . . . . . . . . . . . . . . . . . 193.2.1 Cella full custom . . . . . . . . . . . . . . . . . . . . . 19

3.2.1.1 Linee di alimentazione . . . . . . . . . . . . . 20Disegno delle metal6 . . . . . . . . . . . . . . . 21

3.2.2 Cella XORAM . . . . . . . . . . . . . . . . . . . . . . 223.2.2.1 Posizionamento transistori . . . . . . . . . . . 22

Grafo di Eulero . . . . . . . . . . . . . . . . . . 22Layout finale . . . . . . . . . . . . . . . . . . . . 23

3.2.3 Logica combinatoria . . . . . . . . . . . . . . . . . . . 253.2.3.1 Celle NOR e NAND . . . . . . . . . . . . . . 25

3.2.4 Costruzione del circuito . . . . . . . . . . . . . . . . . 25Orientamento delle celle . . . . . . . . . . . . . 25

3.3 Routing dei segnali . . . . . . . . . . . . . . . . . . . . . . . . 273.3.1 Routing dei segnali di input ed output . . . . . . . . . 27

3.3.1.1 XORAM . . . . . . . . . . . . . . . . . . . . 27Write Line. . . . . . . . . . . . . . . . . . . . . . 27Bit Line e Bit Line Negata. . . . . . . . . . . . . 28

3

INDICE INDICE

Output. . . . . . . . . . . . . . . . . . . . . . . 283.3.1.2 WL - celle NOR e NAND . . . . . . . . . . . 28

3.3.2 Routing fra le varie celle . . . . . . . . . . . . . . . . . 29

4 Simulazioni 314.1 Input ed Output . . . . . . . . . . . . . . . . . . . . . . . . . 314.2 Caso tipico . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

4.2.1 Funzionamento del circuito . . . . . . . . . . . . . . . . 324.2.1.1 Inserimento della WL nella logica di uscita . . 32

4.3 Worst case . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334.3.1 Simulazione slow-slow . . . . . . . . . . . . . . . . . . 344.3.2 Simulazione fast-fast . . . . . . . . . . . . . . . . . . . 344.3.3 Considerazioni worst-case . . . . . . . . . . . . . . . . 34

4.4 Frequenza massima . . . . . . . . . . . . . . . . . . . . . . . . 354.5 Sim. della corrente . . . . . . . . . . . . . . . . . . . . . . . . 36

4.5.1 Consumo corrente - A stato logico alto . . . . . . . . . 384.5.1.1 Consumo della cella di logica combinatoria . . 40

Corrente di crow-bar. . . . . . . . . . . . . . . . 424.5.1.2 Consumo della cella XORAM . . . . . . . . . 42

Percorso della corrente . . . . . . . . . . . . . . 424.5.2 Consumo corrente - A stato logico basso . . . . . . . . 43

4.5.2.1 Consumo della cella di logica combinatoria . . 434.5.2.2 Consumo della cella XORAM . . . . . . . . . 43

4.5.3 Consumo di corrente in simulazione di worst-case . . . 434.5.4 Considerazioni . . . . . . . . . . . . . . . . . . . . . . . 44

5 Conclusioni 49

Bibliografia 51

4

Capitolo 1

Introduzione

L’individuazione delle tracce negli esperimenti di fisica delle alte energie e ne-cessaria perche soltanto una piccola parte dei dati puo essere memorizzata.Questa operazione deve essere fatta in tempo reale e richiede grosse capacitadi calcolo online. Il FastTracker (FTK) e un processore che raccoglie i datidi un collisore di adroni e ne ricostruisce le tracce. Il chip FastTracker peri trigger dell’esperimento ATLAS e un’evoluzione del Silicon Vertex Tracker(SVT) [1], che ricostruisce le traiettorie grazie a celle di memoria associativa,dette Content Addressable Memory (CAM). Questo tipo di memoria com-para in parallelo gli eventi con i dati pre-calcolati che sono i pattern a bassarisoluzione precedentemente immagazzinati nella memoria e restituisce l’in-dirizzo dei pattern che coincidono con il dato. A questo punto un processorericeve i pattern che hanno trovato corrispondenza nei dati memorizzati e laloro traccia ad alta risoluzione per eseguire il fit finale della traccia (TrackFitter, TF).

Il nuovo chip FTK sara utilizzato per l’upgrade del rivelatore ATLAS,che avra una luminosita piu alta (1034 cm−2 s−1) e aumentera la complessitadegli eventi: di conseguenza sara necessario immagazzinare un numero moltopiu grande di dati. Per questo motivo si e ritenuto opportuno scegliere unatecnologia a 65 nm, che permette di immagazzinare molti piu dati rispettoa SVT (costruito con tecnologia a 180 nm). Grazie a cio ricostruira conmaggior precisione la traiettoria degli eventi.

Visto che l’insieme dei pattern di memoria occupa circa il 70% dell’interaarea, si e ritenuto ragionevole ridurne il piu possibile le dimensioni utilizzandoun disegno full custom, che offre inoltre la possibilta di introdurre nuovestrategie di riduzione dei consumi.

La memoria associativa opera in modalita sincrona, con un clock limitatoa circa 10 ns, a causa della complessita della cella; comunque sara possibileridurre il consumo di energia diminuendo ulteriormente il clock.

5

1.1. MEMORIA ASSOCIATIVA CAPITOLO 1. INTRODUZIONE

0

1

7

pattern

pattern 0 layer 0 FF layer 1 FF layer 2 FF layer 7 FF

FF FF FF FFpattern 1

FF FF FF FFpattern 2

FF FF FF FFpattern 3

FF FF FF FFpattern n

Bus_Layer<0> Bus_Layer<1> Bus_Layer<2> Bus_Layer<7> ....

HIT HIT HIT HIT

HIT

MA

JOR

ITY

FIS

CH

ER

TR

EE

Figura 1.1: AMchip array

L’obiettivo di questa tesi e la progettazione di una cella di memoria as-sociativa che consumi meno corrente e possibilmente occupi circa la stessaarea, rispetto a quella utilizzata nell’AMchip04. La cella di memoria e basataesclusivamente su circuiti digitali: un circuito di immagazzinamento SRAMed un circuito XOR che effettua il confronto dei bit. E stata inoltre svi-luppata una logica combinatoria che processi i dati provenienti dalle celle dimemoria che corrispondono alla medesima traccia.

1.1 Principio di funzionamento del chip di

Memoria Associativa

Come molte memorie, la memoria associativa usata per questo chip (AMchip)e basata su un modello a matrice (Fig. 1.1).

Vengono usate le colonne per distribuire informazioni di hit tramite busverticali chiamati search bit line e le righe per le write line (il segnale cheabilita l’operazione di scrittura) e per le match lines (il segnale che identificala presenza in memoria del dato cercato). Ogni bus e formato da 36 fili: 18search bit line e 18 search bit line negate. Ogni riga della matrice corrispondead un pattern. Ogni pattern e formato da otto layer, ognuno dei quali eorganizzato in 18 sotto-blocchi CAM. Si potra quindi identificare una tracciache attraversa fino a otto strati di detector. Se i 18 dati di ognuna delleotto celle corrisponde al dato della search bit line, allora il confronto ha esitopositivo.

6

CAPITOLO 1. INTRODUZIONE 1.2. CIRCUITO PROPOSTO

1.2 Circuito proposto

Il circuito, e stato progettato in tecnologia CMOS. E composto da una me-moria SRAM, dove viene immagazzinato il dato, da un circuito di confrontoche esegue un’operazione XOR bit a bit fra il dato proveniente dalle searchbit line ed il dato immagazzinato, e da una logica combinatoria che prov-vede a processare i dati provenienti dalle celle di memoria associativa ed atrasmettere un bit di output.

Si e disegnato lo schema circuitale ed il layout per la realizzazione susilicio dell’intero circuito; si sono poi effettuate una serie di simulazioni percontrollare il corretto funzionamento del circuito nelle condizioni tipiche edin situazione di worst case. Successivamente sono state effettuate simulazioniper determinare il consumo di corrente.

7

1.2. CIRCUITO PROPOSTO CAPITOLO 1. INTRODUZIONE

8

Capitolo 2

Layer di memoria associativapresente nell’AMchip04

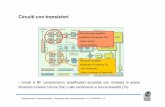

Il circuito AMchip04 e il candidato per la costruzione del chip FastTracker perl’upgrade di ATLAS. L’intero layer di memoria e formato da 4 celle NAND-CAM e 14 celle NOR-CAM ed un flip-flop verso l’uscita (Layout e disegnodei blocchi in Figura 2.1).

Il generatore di corrente carica la match line con un valore costante dicorrente solo se il dato immagazzinato nelle celle coincide con il dato di inputsulle bit line [2]. Se invece il dato di almeno una delle quattro celle NANDnon coincide con quello delle bit line, si interrompe la match line evitandoche si carichi. Se una cella NOR non ha match, si crea un cammino versoterra e quindi la match line si scarica. Il fatto di bloccare la precarica, se unadelle prime quattro celle non ha matching, permette un notevole risparmiosul consumo di corrente.

In termini di voltaggio dei nodi, se il matching di tutte le celle ha avuto

4 NAND

cells:

2,6 x 1.8 μm

each14 NOR cells:

2.6 x 1.8 μm each

Latch SR + ML discharge:

4.7 x 1.8 μm

Full layout: 53 μm x 1.8

Figura 2.1: Schema circuitale e layout del singolo layer

9

2.1. PROBLEMATICHE CAPITOLO 2. AMCHIP04

esito positivo, la match line e caricata ad un valore logico alto (circa 1 V).Se invece il matching di una qualunque delle 18 celle ha esito negativo, lamatch line non viene caricata ed il voltaggio risulta circa 0 V.

Il circuito e stato disegnato con un approccio full custom, ma si e mante-nuta la compatibilita con le parti del circuito in standard cell. Si e usata unaaltezza di cella ed una larghezza delle linee di alimentazione pari a quelle distandard cell. Le misure del layer sono riportate in Tabella 2.1.

Tabella 2.1: Dimensioni del layer e delle celle che locostituiscono

Dimensioni (in µm)

Generatore di corrente 2,6 × 1,8Cella NAND 2,6 × 1,8Cella NOR 2,6 × 1,8Flip-Flop 3,6 × 1,8Intero Layer 53 × 1,8

2.1 Problematiche presenti in AMchip04

Sono presenti delle problematiche ancora irrisolte nel progetto del circuitodi memoria associativa AMchip04, le piu importati sono la possibilita cheparte del circuito, quando non si ha matching delle quattro celle NAND, masi ha match di tutte le 14 celle NOR, possa diventare floating e la presenzadi una logica complessa per pilotare il generatore di corrente che carica lamatch line. Per ovviare a questi inconvenienti si e deciso di creare una diversatipologia di memoria associativa, che non facesse uso di precarica, ma chefosse progettata totalmente fully CMOS.

10

Capitolo 3

Layer Singolo basato su celle dimemoria XORAM

3.1 Schema del circuito

Si e progettato un circuito costituito da due blocchi principali: il blocco dellamemoria, che contiene il circuito di lettura e il blocco di logica combinato-ria che confronta i dati provenienti da un singolo layer del rivelatore conquelli pre-memorizzati nella memoria basata su celle di memoria XORAM(Figura 3.1).

Tale modulo a layer singolo si interfaccia con i circuiti periferici mediantei seguenti canali: diciotto canali input BL〈17 : 0〉 e diciotto di BLN〈17 : 0〉, rispettiva-

mente search bit line e search bit line negata, che trasmettono il datoed il dato negato per scrittura e confronto; un canale di input WL (writeline) che seleziona con un segnale alto lascrittura e con un segnale basso la lettura del blocco di memoria; un canale di output O, questa uscita deve essere a uno stato logico altose il dato immagazzinato coincide con il dato distribuito dalle bit line,basso negli altri casi.

Il modulo, chiamato “layer”, sara quindi formato da diciotto celle dimemoria XORAM ed una logica combinatoria di uscita a diciotto ingressi(Figura 3.2).

11

3.1. SCHEMA DEL CIRCUITO CAPITOLO 3. LAYER SINGOLO

Figura 3.1: Schema dell’intero layer singolo.

Figura 3.2: Schema circuitale dell’intera memoria con espli-citati i due blocchi: a sinistra quello delle celle XORAM, adestra quello di logica combinatoria.

12

CAPITOLO 3. LAYER SINGOLO 3.1. SCHEMA DEL CIRCUITO

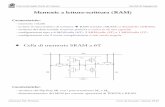

Figura 3.3: Schema della singola cella XORAM dove si evi-denziano i vari blocchi, gli input e gli output; CWrite contienela cella SRAM a sei transistori, CRead contiene la porta logicaXOR per il confronto.

3.1.1 Cella XORAM

Si e pensato di costruire una cella costituita da una memoria SRAM a seitransistori collegata ad una logica XOR con cui effettuare il confronto deldato immagazzinato con quello proveniente dalle bit line.

La cella e stata progettata prestando attenzione al risparmio di correnteed all’occupazione della minor area possibile sul silicio. Un circuito XORa pass-transistor con un anello in cui viene immagazzinato il dato e parsola soluzione che permettesse di conciliare un basso consumo di corrente conun’occupazione di area accettabile.

Il circuito, disegnato in Figura 3.4, puo essere diviso in due parti: una diconfronto ed una di memoria SRAM (Figura 3.3).

3.1.1.1 Cella SRAM a sei transistori

Questa parte del circuito (Figura 3.5) e in grado di memorizzare il datotramite due inverter connessi in un anello. La scrittura avviene quando ilsegnale di writeline (WL) assume uno stato logico alto: questo mette in con-duzione i due NMOS creando una corrente che fluisce dall’esterno della cella(da BL e BLN) verso l’interno (A e NA). In tal modo si esegue la scritturadei dati, che vengono immagazzinati nei nodi A e NA. Precedentemente siera pensato, per risparmiare area di silicio, di utilizzare un solo transistoreNMOS con una sola entrata costituita da BL per scrivere il dato. Questo

13

3.1. SCHEMA DEL CIRCUITO CAPITOLO 3. LAYER SINGOLO

Figura 3.4: Schema circuitale della cella XORAM.

pero comprometteva la corretta scrittura: se BL era uguale a 0 la scritturariusciva, ma se BL era uguale a 1, A non veniva inserita correttamente. Cioera dovuto al fatto che il transistore NMOS permette una scrittura di uno0 forte, ma di uno stato 1 debole, quindi non in grado di sostituire il datoprecedente.

3.1.1.2 Circuito di lettura/confronto

La cella ha la funzione di lettura e di confronto tra il dato immagazzinato eil dato proveniente dalle bit line, e composta da una porta logica XOR, il cuifunzionamento e riportato nella Tabella 3.1.

La porta logica XOR e realizzata con lo schema a sei transistori illustratoin Figura 3.6. Questo schema, basato su una logica a pass-transistor inveceche fully-CMOS [3], permette

di ridurre l’area utilizzata garantendo comunque il corretto funzionamen-to. Nel circuito finale, come si vede in Figura 3.7, si e eliminato l’inverter,poiche A e NA sono gia presenti nell’anello di memorizzazione.

14

CAPITOLO 3. LAYER SINGOLO 3.1. SCHEMA DEL CIRCUITO

Figura 3.5: Schema circuitale dell’anello di retroazione doveviene immagazzinato il dato, i due transistori NMOS pilotatida WL selezionano la modalita scrittura o lettura

Figura 3.6: Schema circuitale di un circuto XOR a seitransistori.

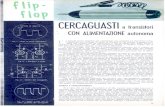

3.1.2 Logica combinatoria

La logica combinatoria serve a processare la serie di dati che arrivano dallediciotto celle XOR. La funzione logica che permette di avere un output finalecon valore logico alto se e solo se tutte le celle hanno output con valore logicobasso e la NOR, infatti l’uscita di questa funzione e a un valore logico altosolo se tutti gli input sono a valore logico basso. In Tabella 3.2 e descritta unafunzione NOR a 3 input, che puo essere facilmente generalizzata a diciotto,

15

3.1. SCHEMA DEL CIRCUITO CAPITOLO 3. LAYER SINGOLO

Figura 3.7: Schema circuitale del circuito XOR per ilconfronto in lettura

il circuito delle singole porte e in Figura 3.10. Vista l’impossibilita della co-struzione di un circuito NOR a diciotto ingressi costituito da diciotto PMOSin serie, e stato costruito un circuito con tecnologia fully-CMOS avente seiporte NOR a tre ingressi, collegate fra loro a tre a tre, tramite due porteNAND (in Tabella 3.2 e descritta una funzione NAND a 3 input, il circuitoe in Figura 3.10). Queste ultime a loro volta sono collegate in cascata ad unNOR a tre ingressi. Il circuito e rappresentato in Figura 3.8. Si e inserito ilsegnale di WL come ingresso nel NOR finale per non avere transazioni spuriein output durante la scrittura della cella.

3.1.2.1 Scelta del circuito 3× 6

Inizialmente, per la logica di uscita, si era optato per uno schema del tipo4 × 4 + 2 (50 transistori) (Fig. 3.9) in modo da minimizzare il numero ditransistori utilizzati (e di conseguenza l’area). Il maggior numero di ingressi-quattro- per ogni porta logica pero avrebbe potuto causare dei problemi dicaduta di tensione all’interno delle celle NAND e NOR in corrispondenza

Tabella 3.1: Funzione logica combinatoria XOR

A B 0

1 1 01 0 10 1 10 0 0

16

CAPITOLO 3. LAYER SINGOLO 3.1. SCHEMA DEL CIRCUITO

Figura 3.8: Schema circuitale della logica in output

delle serie di MOS, soprattutto in condizioni di funzionamento in aree pros-sime ai limiti di worst case. Pertanto si e preferita una configurazione conmeno MOS, tre in serie, che, pur occupando una porzione maggiore di area,comunque solo il 3,5% avendo 4 transitori in piu, assicura una notevole ro-bustezza nel funzionamento, oltre ad essere perfettamente simmetrica (tuttii segnali in ingresso hanno lo stesso numero di porte logiche verso l’uscita).Questo evita che i vari segnali in ingresso accumulino differenti ritardi dovutia percorsi logici diversi.

17

3.1. SCHEMA DEL CIRCUITO CAPITOLO 3. LAYER SINGOLO

Figura 3.9: Schema circuitale della logica combinatoria4× 4 + 2, configurazione successivamente scartata

Figura 3.10: Schema circuitale dei circuiti NOR (a sinistra) eNAND (a destra)

18

CAPITOLO 3. LAYER SINGOLO 3.2. LAYOUT DEL CIRCUITO

Tabella 3.2: Funzione logica NOR e NAND a tre ingressi.

A B C O-NOR O-NAND

1 1 1 0 01 1 0 0 11 0 1 0 11 0 0 0 10 1 1 0 10 1 0 0 10 0 1 0 10 0 0 1 1

3.2 Layout del circuito

Al momento della progettazione del layout si e dovuto scegliere fra due diversemetodologie di disegno: compatibilita con le Standard Cell, utilizzando le misure standard

di altezza della cella (1.8 µm), le alimentazioni in metal1 di spessore0,33 µm; Full Custom, senza limiti di dimensione nella progettazione, con lapossibilita di ridurre il piu possibile l’area su silicio, con l’inconvenientedi perdere la compatibilita con le altre parti del circuito costruite instandard cell.

Si e optato per la tipologia full custom, per cui la compatibilita con altrezone del processore realizzate in standard-cell passera in secondo piano. Ilgran numero di celle di memoria presenti nel processore (81 920) fa propen-dere maggiormente verso riduzione dell’area, potendo attivare ad una cellacon altezza pari a 1,535 µm.

3.2.1 Cella full custom

Le misure si sono determinate dalla minima distanza fra i contatti di gatedei transistor NMOS e PMOS (Figura 3.11).

19

3.2. LAYOUT DEL CIRCUITO CAPITOLO 3. LAYER SINGOLO

0.12um

Figura 3.11: Distanza minima fra i gate, fattore principaledell’altezza minima di cella

3.2.1.1 Linee di alimentazione

L’alimentazione e portata attraverso le linee in metal6, per permettere disovrapporla ai transistori o ad altre metallizzazioni di routing1; inoltre lametal6 e piu alta ed ha spessore maggiore, quindi presenta una resistenzaminore e cio comporta una conduzione migliore della corrente. Lo svantag-gio e che bisogna far scendere l’alimentazione fino alla metal1 mediante vieverticali.

Si pone a questo punto un problema: le interconnessioni fra le varie me-tallizzazioni hanno una resistenza non trascurabile i cui valori sono riportatiin Tabella 3.3). Per ovviare a cio si e cercato di piazzare il numero piu altopossibile di via fra un livello e l’altro, cosı da avere piu resistenze in paralleloal fine di ridurre la resistenza totale. Per esempio per passare dalla metal1alla metal6 inserendo una sola via si ha una resistenza totale di 12.3 Ω, invecemettendone quattro ed una fra metal5 e metal6 si hanno 3, 3 Ω (esempio inFigura 3.12). Cosı facendo si ridurra la probabilita di mancato contatto infase di costruzione, aumentando la resa del processo. Affiancando le variecelle si e fatto inoltre attenzione, ove possibile, ad unire le varie metal dellevia fra loro, in modo di aumentare maggiormente il numero di connessioni.

Le via5, che connettono la metal5 con la metal6, essendo piu grandi, sonomolto meno resistive, possono essere quindi inserite in numero minore: lavia5 e stata posta a cavallo fra le due celle cosı da averne una in comune fradue celle adiacenti (una a destra ed una a sinistra come in Figura 3.13).

1Con routing si indica il collegamento, tramite metallizzazioni, delle varie celle fra loro

e del layer di memoria con il resto del chip di memoria associativa.

20

CAPITOLO 3. LAYER SINGOLO 3.2. LAYOUT DEL CIRCUITO

Tabella 3.3: Valori delle resistenze delle varie via, estratte conCALIBRE

Metal Resistenza

M1-M2 3 ΩM2-M3 3 ΩM3-M4 3 ΩM4-M5 3 ΩM5-M6 0,3 Ω

Figura 3.12: Esempio della connessione fra le varie via, inviola quelle fino alla metal4 ed in giallo con il riquadro fra lametal5 e la metal6, la linea verticale viola indica la fine dellacella.

Disegno delle metal6 Nel posizionare le via5 si deve tener conto della ne-cessita di lasciare di 0,25 µm liberi da metallizzazione per la metal5, che serveper il routing dei segnali. I contatti di via5 devono essere coperti da metal6la cui larghezza minima, pari peraltro alla distanza minima fra metallizza-zioni diverse, e 0,4 µm. L’osservanza di queste regole di disegno si ottienesagomando la metal6 in corrispondenza delle varie via5 come raffigurato inFigura 3.14.

21

3.2. LAYOUT DEL CIRCUITO CAPITOLO 3. LAYER SINGOLO

Figura 3.13: Esempio delle via5 in comune fra due celle.

Figura 3.14: Forma della metal6 (azzurra) nelle celle XORAMin corrispondenza delle via5 (gialle)

3.2.2 Cella XORAM

La cella XORAM e composta dall’anello di retroazione e dal circuito di lettura(v. paragrafo 3.1.1).

3.2.2.1 Posizionamento transistori

Il circuito e stato disegnato sul silicio in un’unica cella. Per ottenere unaconnessione efficace che permette di risparmiare area e di facilitare le inter-connessioni si e fatto ricorso ad un grafo di Eulero (Figura 3.16).

Grafo di Eulero Si costruisce assegnando ai nodi i nomi dei nodi elettricied agli archi i nomi dei transistori eseguendo l’operazione per gli NMOSed i PMOS . Si considerano poi i cammini che permettono di unire i vari

22

CAPITOLO 3. LAYER SINGOLO 3.2. LAYOUT DEL CIRCUITO

Figura 3.15: Circuito della cella XORAM con i transistorinumerati per eseguire l’algoritmo del grafo di Eulero.

nodi cercando di sceglierli in modo da non interromperli troppe volte, percheogni volta che si interrompe il cammino non si possono usare transistoristaggered2. Si e cercato ove possibile di avere le alimentazioni a destra e asinistra e non al centro cosı da poter collegare le alimentazioni sui lati dellacella, dove e presente piu spazio per piazzare delle via. Nella Figura 3.16sono evidenziati i percorsi utilizzati.

Layout finale Il disegno per la successiva realizzazione su silicio (Figu-ra 3.17) e formato da sei NMOS staggered e da due blocchi di PMOS, unosingolo e 3 staggered; la larghezza finale (2,37 µm) e quindi determinata dal-la larghezza della regione p connessa ai transistori. Per quanto riguarda lealimentazioni, quella per la regione n risulta distaccata, quella per la regionep integrata.

Durante il disegno della cella XORAM, si e deciso di lasciare 0, 25 µm(Figura 3.21) liberi da qualunque metallizzazione (tranne la metal6 e la me-

2Dei transistori sono definiti staggered quando, data la simmetria dei transitori MOS,

il surce ed il drain del successivo vengono uniti in un unico blocco.

23

3.2. LAYOUT DEL CIRCUITO CAPITOLO 3. LAYER SINGOLO

Figura 3.16: Grafo di Eulero; i PMOS sono indicati in rossoe gli NMOS in nero; i nomi dei transistori corrispondono alloschema nella Figura 3.15.

WLNA

WL

NA

BL

BLA

Figura 3.17: Layout della cella XORAM, in cui sono indicatii contatti con i relativi nomi dei nodi.

tal4 di BL e BLN) per lasciare spazio al successivo routing di collegamentoverso la logica combinatoria che attraversera la cella proprio in questa zona.

Gli ingressi BL e BLN sono in metal4, WL e in metal3, l’output puouscire su qualunque metal. Per il routing si rimanda alla sezione 3.3.

24

CAPITOLO 3. LAYER SINGOLO 3.2. LAYOUT DEL CIRCUITO

A B C

OVSS

VDD

A B C

VSS

VDD

O

Figura 3.18: Layout della cella NOR (a sinistra) e NAND (adestra), in cui sono indicati i contatti con i nomi dei nodi.

3.2.3 Logica combinatoria

La logica combinatoria, il cui schema circuitale e rappresentato in Figura 3.8,e formata da un albero costituito da porte NAND e NOR collegate fra loroin modo da avere una funzione NOR risultante.

3.2.3.1 Celle NOR e NAND

L’altezza delle celle NAND e NOR e determinata dall’altezza della cella XO-RAM, quindi, essendo la cella meno densa ed avendo meno componenti, sipossono posizionare piu liberamente i transistori, si e pertanto deciso di av-vicinarli, liberando spazio verso il basso della cella, dove sono stati spostaticontatti di gate, in modo che siano piu facilmente accessibili per il routing.Il layout principale e in Figura 3.18.

La cella NOR e stata anche disegnata nella variante con input WL: sempli-cemente si e spostato il collegamento C nel mezzo della cella in corrispondenzacon la WL.

3.2.4 Costruzione del circuito

Le diciotto celle sono state collocate in modo da minimizzare la lunghezzadelle metallizzazioni di routing. Lo schema e riportato nel floorplanning diFigura 3.19.

Orientamento delle celle Le varie celle sono specchiate fra loro a cop-pie (Figura 3.20), per avere piu contatti di alimentazione in parallelo e unaquantita maggiore di metallo in prossimita di essi.

25

3.2. LAYOUT DEL CIRCUITO CAPITOLO 3. LAYER SINGOLO

ZOOM

Figura 3.19: Floorplanning dell’intero layer a 18 bit, in cuiciascuna delle celle illustrate sotto e costituita dall’insiemedelle quattro celle illustrate sotto. Il layout di ciascuna cellaverde e rappresentato in Figura 3.20.

Figura 3.20: Blocco di quattro celle in cui sono stati eviden-ziati gli assi di simmetria. Queste celle costituiscono i blocchiverdi in Figura3.19.

Per poter affiancare verticalmente diverse celle si dovra compiere unaspecchiatura delle stesse lungo il piano orizzontale di separazione.

26

CAPITOLO 3. LAYER SINGOLO 3.3. ROUTING DEI SEGNALI

0.05

0.1

0.1(0.25)

Figura 3.21: Distanze fra i contatti, le metallizzazioni dirouting ed il confine della cella, espresse in micron.

3.3 Routing dei segnali

Con routing si indica il collegamento, tramite metallizzazioni, delle varie cellefra loro e del layer di memoria con il resto del chip di memoria associativa.

Gli 0.25 µm liberi da metallo sui confini superiore e inferiore delle celleservono per il routing: la tecnologia in uso permette di costruire metallizza-zioni di spessore 0.1 µm (0.09 µm per la metal1), fra loro vicine non piu di0.1 µm (0.09 µm per la metal1) come illustrato in Figura 3.21).

3.3.1 Routing dei segnali di input ed output

Disegnando il circuito si e prestata molta attenzione nel posizionare gli in-gressi per i segnali in entrata e in uscita dalle singole celle, in modo daminimizzare la lunghezza delle varie metallizzazioni e non aumentare l’areaoccupata su silicio.

3.3.1.1 XORAM

Write Line. In ogni layer e presente una diversa WL che deve essere pro-pagata lungo l’intera lunghezza dello stesso fino alla cella NOR finale, dopola quale e posizionato un blocco di uscita che puo avere come input il segnaledi WL. Si e scelto di disegnare la WL orizzontale lungo la totalita delle celle(Figura 3.22), cosı da rendere immediato il collegamento di una cella con lasuccessiva. Si e usata la metal3 perche, nel percorso scelto per il routingrisulta priva di incroci con altri collegamenti.

27

3.3. ROUTING DEI SEGNALI CAPITOLO 3. LAYER SINGOLO

Figura 3.22: In evidenza la metal3, tramite la quale etrasmessa la WL, che attraversa tutte le celle al centro.

Figura 3.23: In evidenza la metal4, tramite la quale etrasmessa la BL e la BLN, che attraversa la cella in verticale.

Bit Line e Bit Line Negata. I trentasei ingressi di BL e BLN devonoessere collegati a tutte le celle XORAM nel chip di memoria associativa,quindi devono essere trasmessi in verticale da un layer a quello sopra e aquello sottostante. Si e utilizzata la metal4 perche, nel percorso scelto per ilrouting risulta priva di incroci con altre connessioni (Figura 3.23).

Output. L’uscita dalla singola cella XORAM e disegnata in metal1 cosı dapoterla collegare verso l’esterno con qualsiasi metallizzazione.

3.3.1.2 Routing della WL nelle celle NOR e NAND

La WL viene disegnata anche all’interno di queste celle anche se non vieneutilizzata (tranne che nella NAND piu a destra). Gli input delle celle vengonoportati direttamente sui gate dei transitori, perche si sono inseriti i contatti

28

CAPITOLO 3. LAYER SINGOLO 3.3. ROUTING DEI SEGNALI

Figura 3.24: In evidenza le metal1 e metal2 (nella parte bassadella cella) del routing fra tre celle XORAM e una delle seiporte NOR.

verso il basso. L’output e stato portato verso destra per facilitare il passaggiodelle metallizzazione.

3.3.2 Routing fra le varie celle

Per connettere le celle XORAM, la logica combinatoria e le singole celle dilogica fra loro viene utilizzato lo spazio lasciato libero dalle metallizzazioninella parte superiore ed inferiore delle celle (v. par. 3.2.2.1). Per connetterele celle XORAM alla logica combinatoria si sono usate le metal1 e metal2come in Figura 3.24.

Per le interconnessioni fra i componenti NOR e NAND si sono utilizzatele metal3 e metal5, sempre nello spazio nella parte inferiore della cella, conlo stesso metodo e schema utilizzato per le celle XORAM. Per le connessionifra le celle NAND intermedie e la NOR finale, invece, si utilizza lo spaziosovrastante le celle, con collegamenti in metal3 e metal5.

29

3.3. ROUTING DEI SEGNALI CAPITOLO 3. LAYER SINGOLO

30

Capitolo 4

Simulazione del Circuito

La simulazione del circuito descritto nel precedente capitolo e stata effettuatautilizzando il software di simulazione “Analog Design Environment Layout”(ADEL) di Cadence. Precedentemente si sono estratti i parassiti capacitivie resistivi dal layout grazie all’analisi Parassitic EXtraction (PEX) eseguitadal software CALIBRE di Mentor Graphics.

4.1 Segnali di input ed output

Il chip di memoria associativa lavora a 100 MHz [1]. Di conseguenza i segnalidi input (BL e BLN) hanno un periodo di circa 10 ns, (citazione articoloFTK), e un tempo di salita e di discesa di circa 300 ps, tipico della tecnologiain uso.

Il segnale di output deve essere a tensione 1,2 V se il dato e in uno statologico alto, circa 0 V in tutti gli altri casi e deve inoltre avere fronti di salitae discesa con durata minore di 300 ps. Il segnale di WL sara un impulsodi durata 5 ns, con tempo di salita e discesa 300 ps. Si sono scelti quindi ivalori riportati in Tabella 4.1, usati per tutte le simulazioni di questo capitolo.La BL〈0〉 e stata simulata con periodo doppio rispetto alle restanti BL perpoter effettuare tutti i vari casi di confronto possibile; si sono fatte anchesimulazioni in cui altre BL (anche piu di una) hanno un periodo di 20 ns; ilfunzionamento del circuito e corretto.

Le simulazioni effettuate sono di typical case (tt) e worst case, slow-slow(ss) e fast-fast (ff); tra le varie simulazioni cambiano i parametri interni deitransistori, la temperatura di esercizio e la tensione di alimentazione. Cioinfluenza la conduzione di corrente ed i tempi di commutazione delle portelogiche.

31

4.2. CASO TIPICO CAPITOLO 4. SIMULAZIONI

Tabella 4.1: Valori di input scelti per eseguire la simulazione

Input Periodo hi voltage low voltage rise time fall time

BL〈0〉 20 ns 1,2 V 0 V 300 ps 300 psBL〈1〉 . . . 〈17〉 10 ns 1,2 V 0 V 300 ps 300 ps

4.2 Simulazione nel caso tipico

La simulazione typical case viene effettuata con valore di temperatura di27 °C e con le caratteristiche dei componenti che costituiscono il circuitoal valore tipico medio. Questo tipo di simulazione e utile per verificare ilfunzionamento in condizioni normali.

4.2.1 Funzionamento del circuito

Nel grafico in Figura 4.1 si sono riportati i risultati della simulazione; ilgrafico riporta il caso in cui tutte le celle di memoria vengono scritte ad 1, cherisulta di piu facile comprensione. Sono state comunque eseguite simulazionicon molte combinazioni diverse di scrittura e confronto.

I nodi interni delle prime due celle di memoria A〈0〉 ed A〈1〉 (che risultauguale a tutti gli altri 16) vengono scritti correttamente ad un valore logicoalto. Le cadute di tensione, visibili in corrispondenza del cambiamento distato logico da alto a basso delle rispettive BL, sono dovute ad un prelievodi corrente, in corrispondenza della caduta, dall’anello costituito dai due in-verter. Queste cadute comunque non influenzano il corretto comportamentodel circuito: il picco piu basso e uguale a 1,080 V, sempre in stato logico altoed i nodi A risalgono molto velocemente al valore corretto.

L’uscita risponde correttamente, e la transizione e molto ripida nella salitae nella discesa.

4.2.1.1 Inserimento della WL nella logica di uscita

Come gia spiegato nel capitolo precedente, il segnale d’ingresso WL vieneinserito anche nell’ultima porta NOR dell’albero della logica, in modo chel’output non abbia mai uno stato logico alto mentre il circuito e in fase discrittura. Questo perche altrimenti si avrebbero delle false transizioni inuscita durante la lettura, non avrebbe peraltro senso avere un confronto frail dato ed il segnale che lo sta scrivendo.

32

CAPITOLO 4. SIMULAZIONI 4.3. WORST CASE

0 25.0 50.0 75.0 100.0 125.0 150.0time (ns)

1.5

1.25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .225

1.2

1.175

1.15

1.125

1.1

1.075

V (

V)

V (

V)

1 .225

1.2

1.175

1.15

1.125

1.1

1.075

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

/O

/ I1 / I1 / I<0> /A

/ I1 / I1 / I<1> /A

/BL<1>

/BL<0>

/WL

time (ns)

Figura 4.1: Grafico della simulazione nel caso tipico.

4.3 Simulazioni di worst case

Le simulazioni di caso peggiore si effettuano per studiare il comportamen-to del circuito in condizioni al limite della zona di funzionamento; possono

33

4.3. WORST CASE CAPITOLO 4. SIMULAZIONI

emergere malfunzionamenti, ritardi e consumi di corrente differenti rispettoal funzionamento in typical case.

4.3.1 Simulazione slow-slow

La simulazione slow-slow (abbreviata con la sigla ss) si utilizza per studiare ilfunzionamento nel caso in cui i transistor PMOS ed NMOS siano lenti nellasalita e nella discesa. Si devono utilizzare transitori con costanti di tempopiu alte, resistenze, capacita interne ai componenti e piu elevate e differenzadi potenziale minore. La temperatura deve essere alta, nel caso in cui iltransistore risulta piu lento. I modelli dei componenti sono stati cambiati datt (typical case) a ss (slow-slow), la temperatura e stata alzata a 120 °C. Latensione di alimentazione viene ridotta del 10%.

Il grafico in Figura 4.2 non presenta differenze rilevanti rispetto al typicalcase; i tempi di salita e di discesa e le cadute di tensione dei dati A aumentanodi poco (i valori sono in Tabella 4.2); la cella funziona correttamente.

4.3.2 Simulazione fast-fast

La simulazione fast-fast (abbreviata con la sigla ff) si utilizza per studiareil funzionamento nel caso in cui i transistor PMOS ed NMOS siano velocinella salita e nella discesa. Si devono utilizzare transitori con costanti ditempo piu basse, quindi resistenze e capacita basse e differenza di potenzialemaggiore. La temperatura deve essere bassa, dove il transistore e piu veloce.I modelli di transitori sono stati cambiati da tt (typical case) a ff (fast-fast),la temperatura e stata abbassata 0 °C. La tensione di alimentazione vieneaumentata del 10%.

Il grafico in Figura 4.3 non presenta differenze rilevanti rispetto al typi-cal case; tempi di salita e discesa e i picchi di caduta di tensione dei datiA diminuiscono (i valori sono in Tabella 4.2); la cella funziona comunquecorrettamente.

4.3.3 Considerazioni riguardo alle simulazioni di worst

case del segnale

Il segnale di output non subisce variazioni importanti con il variare dellatemperatura e dei componenti, anche il tempo si salita e di discesa non siscosta piu del 30% - 40%, valori che risultano accettabili. Le differenze frai picchi del dato A risultano irrilevanti in quanto si attestano circa sul 5%.Si puo definire il circuito robusto rispetto alla variazione della temperaturae dei componenti.

34

CAPITOLO 4. SIMULAZIONI 4.4. FREQUENZA MASSIMA

0 25.0 50.0 75.0 100.0 125.0 150.0time (ns)

1.5

1.25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .125

1.1

1.075

1.05

1.025

1.0

.975

.95

.925

V (

V)

V (

V)

1 .125

1.1

1.075

1.05

1.025

1.0

.975

.95

.925

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

/O

/ I1 / I1 / I<0> /A

/ I1 / I1 / I<1> /A

/BL<0>

/BL<1>

/WL

time (ns)

Figura 4.2: Grafico della simulazione slow-slow.

4.4 Frequenza massima di funzionamento

Per verificare la frequenza massima di funzionamento sono state eseguitesimulazioni con segnale in ingresso avente periodo sempre minore, allo scopo

35

4.5. SIM. DELLA CORRENTE CAPITOLO 4. SIMULAZIONI

Tabella 4.2: Caratteristiche del dato in output nelle varieconfigurazioni

Valore tt ss ff

rise time di O 140 ps 200 ps 108 psfall time di O 20 ps 28 ps 17 pscaduta di tensione di A 1,082 V 0,953 V 1,211 V

di trovare il punto in cui il circuito non funzioni piu correttamente. Lafrequenza piu alta per cui il circuito risulta funzionante e 1 GHz (grafico inFigura 4.4). Ovviamente una velocita maggiore comporta un consumo piualto.

4.5 Simulazione della corrente

Per la simulazione della corrente si sono prima utilizzati gli stessi input dellesimulazioni precedenti, poi, dopo aver osservato che il consumo della correntenon dipende dallo stato di uscita o dal dato di output delle singole celleXORAM, per comprendere meglio la provenienza e le cause del consumo dicorrente, si sono utilizzati come input diciotto segnali tutti uguali con periodo10 ns.

A causa dell’asimmetria del circuito si ha un consumo di corrente diversoin base al dato immagazzinato: se A e in uno stato logico alto si hannoconsumi molto piu alti. In Figura 4.5 si nota la differenza fra l’altezza edil numero dei picchi fra il primo e secondo grafico ed il quarto e quinto.Questa differenza di consumo e dovuta alla parziale asimmetria del circuito,in Figura 4.6 sono infatti disegnati i due blocchi, rosso e blu, che si attivanorispettivamente quando A e in stato logico alto e quando A e in stato logicobasso.

Quando A e nello stato logico alto, la corrente puo fluire da VDD o VSSe caricare i poli capacitivi del circuito; quando invece A e nello stato logicobasso, entra in funzione solo il ramo di circuito blu, che non permette ilpassaggio di corrente da VDD e VSS, in quanto A ed AN sono collegati coni gate dei transistori m8 ed m9.

36

CAPITOLO 4. SIMULAZIONI 4.5. SIM. DELLA CORRENTE

0 25.0 50.0 75.0 100.0 125.0 150.0time (ns)

1.75

1.5

1.25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .35

1.325

1.3

1.275

1.25

1.225

1.2

V (

V)

V (

V)

1 .35

1.325

1.3

1.275

1.25

1.225

1.2

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

/O

/ I1 / I1 / I<0> /A

/ I1 / I1 / I<1> /A

/BL<1>

/BL<0>

/WL

time (ns)

Figura 4.3: Ggrafico della simulazione fast-fast.

37

4.5. SIM. DELLA CORRENTE CAPITOLO 4. SIMULAZIONI

0 2.5 5.0 7.5 10.0 12.5 15.0time (ns)

1.25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

6 00

400

200

0

−200

−400

I (u

A)

I (u

A)

1 .5

1.25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1 .225

1.2

1.175

1.15

1.125

1.1

1.075

V (

V)

V (

V)

/WL

/I1/VDD /I1/VSS / I1/VDD /I1/VSS

/O

/BL<1>

/BL<0>

/ I1 / I1 / I<1> /A

time (ns)

Figura 4.4: Risultati della simulazione con frequenza 1 GHz.

4.5.1 Consumo di corrente nei vari blocchi del circuito

quando A e nello stato logico alto

Al consumo di corrente, come si vede in Figura 4.7, concorrono in mododifferente il blocco XORAM e quello della logia combinatoria.

38

CAPITOLO 4. SIMULAZIONI 4.5. SIM. DELLA CORRENTE

0 25.0 50.0 75.0 100.0 125.0 150.0time (ns)

600

500

400

300

200

100

0

−100

I(u

A)

I(u

A)

100.0

0

−100.0

−200.0

−300.0

−400.0

I(u

A)

I(u

A)

1 .25

1.0

.75

.5

.25

0

−.25

V(V

)V

(V)

/ I1/VDD

/I1/VSS

/BL<0>

time (ns)

200

150

100

50.0

0

−50.0

−100

I(u

A)

I(u

A)

2 00

100

0

−100

−200

−300

−400

I(u

A)

I(u

A)

1 .25

1.0

.75

.5

.25

0

−.25

V(V

)V

(V)

/ I1/VDD

/I1/VSS

/BL<0>

Figura 4.5: I primi tre grafici dall’alto si riferiscono alla cor-rente nel caso in cui A e in stato logico alto, gli altri trequando A e in stato logico basso.

I picchi di corrente da VDD sono intervallati ogni mezzo periodo, hannoaltezza 250 µA e larghezza 350 ps, mentre per VSS i valori sono –129 µA

39

4.5. SIM. DELLA CORRENTE CAPITOLO 4. SIMULAZIONI

WL

VDD

A

NA

BL BLN

VSS

OUT

m1

m3

m2

m7

m4

m5

m8

m9

m6

m10

Figura 4.6: Circuito in cui sono state evidenziate le parti checreano asimmetria.

e 190 ps. Il grafico della corrente assorbita dall’intera cella e naturalmentela somma dei grafici delle correnti della cella XORAM e della cella di logicacombinatoria.

4.5.1.1 Consumo della cella di logica combinatoria

Il consumo della cella di logica e dovuto sia alla corrente di crow-bar, che siriconosce dai picchi simultanei provenienti da VDD e VSS, sia alla correntenecessaria per caricare le capacita dei nodi.

I picchi di corrente hanno valore massimo di 231µA e durata di 66 ps perquanto riguarda VDD, e –356µA e 75 ps per VSS.

Il picco di corrente proveniente da VDD e minore in modulo rispetto aquello proveniente da VSS (Figura 4.8); questo perche la capacita dei nodiche si caricano (le connessioni fra le sei celle NOR e le due celle NAND edil nodo di output finale ) e maggiore di quella dei nodi che si scaricano (idiciotto output provenienti dalle celle XORAM e le connessioni fra la cellalogica NAND e la porta NOR finale). Cio e dovuto alle diverse lunghezzedelle interconnessioni metalliche fra una cella logica e le altre. Il picco visibilepiu a destra nella figura risulta di altezza minore ma di larghezza maggiore,essendo le transizioni corrispondenti maggiormente distribuite nel tempo; la

40

CAPITOLO 4. SIMULAZIONI 4.5. SIM. DELLA CORRENTE

0 25.0 50.0 75.0 100.0 125.0 150.0time (ns)

600

500

400

300

200

100

0

−100

I (u

A)

I (u

A)

100.0

0

−100.0

−200.0

−300.0

−400.0

I (u

A)

I (u

A)

4 00

300

200

100

0

−100

I (u

A)

I (u

A)

100.0

0

−100.0

−200.0

−300.0

−400.0

−500.0

I (u

A)

I (u

A)

2 50

200

150

100

50.0

0

−50.0

I (u

A)

I (u

A)

100.0

0

−100.0

−200.0

−300.0

−400.0

I (u

A)

I (u

A)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

/ I1/VDD

/I1/VSS

/ I1/I1/VDD

/I1/I1/VSS

/ I1/I0/VDD

/I1/I0/VSS

/BL<0>

time (ns)

Figura 4.7: Grafico del consumo di corrente nel caso in cuiA sia ad uno stato logico alto: la prima coppia di grafici siriferisce al layer intero, la secondo all’insieme delle diciottocelle XORAM, la terza alla sola logica; nell’ultimo grafico erappresentato il segnale di BL di riferimento.

41

4.5. SIM. DELLA CORRENTE CAPITOLO 4. SIMULAZIONI

Tabella 4.3: Valori dei picchi di corrente nel caso in cui A siaalto

IDD ISSCella altezza durata altezza durataIntero layer 250 µA 350 ps –129 µA 190 psLogica c. 231 µA 66 ps –356 µA 75 psCelle XORAM 347 µA 260 ps –419,6 µA 190 ps

quantita di carica utilizzata e quindi l’area sottostante il picco e uguale aquella del picco a sinistra.

Corrente di crow-bar. Questo fenomeno si presenta quando il blocco ditransistori pull-up e quello pull-down risultano accesi contemporaneamente,permettendo cosı alla corrente di fluire da VDD a VSS.

L’accensione simultanea dei circuiti pull-up e pull-down e dovuta allasalita ed alla discesa non istantanea degli output provenienti dalle celle XO-RAM; infatti si puo identificare un intervallo di tempo in cui il segnale e inuno stato logico intermedio fra alto e basso, che permette l’accensione dei ped nMOS contemporaneamente.

4.5.1.2 Consumo della cella XORAM

Il consumo della cella XORAM e dovuto principalmente al caricamento escaricamento dei nodi capacitivi A e NA, infatti i picchi di carica e scaricasono intervallati da un semi-periodo del segnale di input.

I picchi di corrente hanno valore massimo di 347µA e durata di 260 psper quanto riguarda VDD, e –419,6µA e 190 ps per VSS.

Percorso della corrente Quando la BL ha uno stato logico basso ed ildato A alto, i transistori m2, m3 ed m4 risultano in conduzione (per leetichette dei transistori si rimanda alla Figura 4.6), la corrente fluisce da VDDe carica il nodo A; quando poi BL assume valore logico basso, i transistoriin conduzione saranno m1, m7 ed m5, quindi la corrente puo fluire da VSS ecaricare il nodo NA.

In Tabella 4.3 sono riassunti i valori di picco delle correnti.

42

CAPITOLO 4. SIMULAZIONI 4.5. SIM. DELLA CORRENTE

Tabella 4.4: Valori dei picchi di corrente nel caso in cui A siabasso

IDD ISSCella altezza picco altezza piccoIntero layer 125 µA 600 ps –323 µA 220 psLogica c. 196 µA 105 ps –245 µA 70 psCelle XORAM ±87 µA 320 ps ±74,7 µA 320 ps

4.5.2 Consumo di corrente nei vari blocchi del circuito

quando A e nello stato logico basso

In Figura 4.9 sono rappresentati i grafici di consumo di corrente dell’interolayer di memoria nel caso in cui A sia nello stato logico basso. Come nel casoprecedente si evidenziano delle differenze nell’utilizzo della corrente da partedella cella di logica combinatoria e della cella di memoria XORAM.

4.5.2.1 Consumo della cella di logica combinatoria

Il comportamento della logica combinatoria e sostanzialmente identico conla presenza delle correnti di crow-bar e della corrente utilizzata per caricarele capacita. I picchi risultano alti 196 µA e –245 µA, e larghi 105 ps e 70 ps.Risultano piu bassi e larghi rispetto alla simulazione precedente, perche letransizioni avvengono in un intervallo di tempo maggiore (Figura 4.10).

4.5.2.2 Consumo della cella XORAM

Il comportamento cambia significativamente rispetto al caso in cui A e instato logico alto: sono presenti piu picchi (uno ogni semi-periodo) di altezzaminore (misure in Tabella 4.4).

4.5.3 Consumo di corrente in simulazione di worst-case

Nelle simulazioni worst-case il consumo di corrente varia rispetto al typicalcase, perche sia la temperatura che i componenti interni cambiano modifi-cando i consumi di corrente. Nel caso slow-slow il consumo di corrente saraminore, nel caso fast-fast maggiore, perche variano le capacita e le resistenzeinterne dei dispositivi (grafico in Figura 4.11).

43

4.5. SIM. DELLA CORRENTE CAPITOLO 4. SIMULAZIONI

Tabella 4.5: Valori medi di corrente per singolo layer (asinistra) e per i 655 360 layer (a destra)

IDD ISS IDD ISS

A alto 2,71 µA 3,26 µA A alto 2,62 µA 2,65 µAA basso 4,00 µA 4,04 µA A basso 2,14 µA 1,78 µAMedia 3,36 µA 3,65 µA Media 2,21 µA 2,16 µA

4.5.4 Considerazioni sul consumo di corrente

Il consumo di corrente varia in base al dato immagazzinato nella cella. Perquantificare correttamente il consumo medio dell’intero circuito si e decisodi calcolare la media del valore assoluto delle correnti nei due casi in cui, Ae nello stato logico alto, ed A e nello stato logico basso in tutte le diciottocelle del layer.

Considerando l’insieme degli 81 920 pattern, per un totale di 655 360 layer,sufficientemente grande da poter ipotizzare la meta dei dati immagazzinatiin stato logico alto e l’altra meta basso, si e effettuata la media fra i valori diconsumo con A in stato logico alto e A in stato logico basso. I valori riportatiin Tabella 4.5.

Per quanto riguarda i consumi di picco (i cui valori sono riportati nellesezioni precedenti) non sarebbe indicativo calcolarli per il circuito intero, poi-che, essendo il chip abbastanza esteso, il segnale di clock risulterebbe avereuno skew nelle diverse zone del circuito, quindi i layer non commuterebbe-ro tutti istantaneamente. In fase di progettazione dell’intero chip si potraimpostare il clock skew in modo da avere un buon rapporto fra consumi dipicco e sincronia del circuito.

44

CAPITOLO 4. SIMULAZIONI 4.5. SIM. DELLA CORRENTE

30.0 32.5 35.0 37.5 40.0 42.5time (ns)

200

100

0

−100

−200

−300

I (u

A)

I (u

A)

1.5

1.25

1.0

.75

.5

.25

0

V (

V)

V (

V)

1.5

1.25

1.0

.75

.5

.25

0

V (

V)

V (

V)

/I1/I0/VSS /I1/I0/VDD /I1/I0/VSS /I1/I0/VDD

/ I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ... / I1/ I0/net38<0> / I1/I0/net44<0> /O / I1/ I0/net32<0> / I1/ I0/net26<0> ...

/ I1/I0/net50 /I1/I0/net56 / I1/net11<0><0> / I1/net11<0><1> / I1/I0/net50 /I1/I0/net56 / I1/net11<0><0> / I1/net11<0><1> / I1/I0/net50 /I1/I0/net56 / I1/net11<0><0> / I1/net11<0><1> / I1/I0/net50 /I1/I0/net56 / I1/net11<0><0> / I1/net11<0><1>

time (ns)

Figura 4.8: Blocco di logica combinatoria: grafico della cor-rente e grafico di tutti i nodi che si scaricano e caricano; ildato A e nello stato logico alto.

45

4.5. SIM. DELLA CORRENTE CAPITOLO 4. SIMULAZIONI

0 25.0 50.0 75.0 100.0 125.0 150.0time (ns)

200

150

100

50.0

0

−50.0

−100

I (u

A)

I (u

A)

2 00

100

0

−100

−200

−300

−400

I (u

A)

I (u

A)

2 50

190

130

70.0

10.0

−50.0

I (u

A)

I (u

A)

50.0

0

−50.0

−100.0

−150.0

−200.0

−250.0

−300.0

I (u

A)

I (u

A)

1 00

75.0

50.0

25.0

0

−25.0

−50.0

−75.0

−100

I (u

A)

I (u

A)

1 00

75.0

50.0

25.0

0

−25.0

−50.0

−75.0

−100

I (u

A)

I (u

A)

1 .25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

/ I1/VDD

/I1/VSS

/ I1/I0/VDD

/I1/I0/VSS

/ I1/I1/VDD

/I1/I1/VSS

/BL<0>

time (ns)

Figura 4.9: Grafico del consumo di corrente nel caso in cuiA sia nello stato logico basso: la prima coppia di grafici siriferisce al layer intero, la seconda alla sola logica, la terzaall’insieme delle diciotto celle XORAM.

46

CAPITOLO 4. SIMULAZIONI 4.5. SIM. DELLA CORRENTE

10.0 12.5 15.0 17.5 20.0time (ns)

300

200

100

0

−100

−200

−300

I (u

A)

I (u

A)

1.5

1.25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

1.5

1.25

1.0

.75

.5

.25

0

−.25

V (

V)

V (

V)

/ I1/I0/VDD /I1/I0/VSS /I1/I0/VDD /I1/I0/VSS

/BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13> /BL<0> / I1/net11<17> / I1/net11<15> / I1/net11<16> / I1/net11<14> / I1/net11<13>

/ I1/I0/net26 /I1/I0/net32 /I1/I0/net44 /I1/I0/net38 /I1/I0/net20 /I1/I0/net14 ... / I1/I0/net26 /I1/I0/net32 /I1/I0/net44 /I1/I0/net38 /I1/I0/net20 /I1/I0/net14 ... / I1/I0/net26 /I1/I0/net32 /I1/I0/net44 /I1/I0/net38 /I1/I0/net20 /I1/I0/net14 ... / I1/I0/net26 /I1/I0/net32 /I1/I0/net44 /I1/I0/net38 /I1/I0/net20 /I1/I0/net14 ... / I1/I0/net26 /I1/I0/net32 /I1/I0/net44 /I1/I0/net38 /I1/I0/net20 /I1/I0/net14 ... / I1/I0/net26 /I1/I0/net32 /I1/I0/net44 /I1/I0/net38 /I1/I0/net20 /I1/I0/net14 ... / I1/I0/net26 /I1/I0/net32 /I1/I0/net44 /I1/I0/net38 /I1/I0/net20 /I1/I0/net14 ...

time (ns)

Figura 4.10: Blocco di logica combinatoria: grafico della cor-rente e grafico di tutti i nodi che si scaricano e caricano; ildato A e nello stato logico basso.

47

4.5. SIM. DELLA CORRENTE CAPITOLO 4. SIMULAZIONI

600

500

400

300

200

100

0

−100

I(u

A)

I(u

A)

100.0

0

−100.0

−200.0

−300.0

−400.0

I(u

A)

I(u

A)

/ I1/VDD

/I1/VSS

300

250

200

150

100

50.0

0

−50.0

−100

I(u

A)

I(u

A)

100.0

50.0

0

−50.0

−100.0

−150.0

−200.0

−250.0

−300.0

I(u

A)

I(u

A)

/ I1/VDD

/I1/VSS

0 25.0 50.0 75.0 100.0 125.0 150.0time (ns)

1000

800

600

400

200

0

−200

I(u

A)

I(u

A)

100.0

0

−100.0

−200.0

−300.0

−400.0

−500.0

−600.0

I(u

A)

I(u

A)

1 .25

1.0

.75

.5

.25

0

−.25

V(V

)V

(V)

/ I1/VDD

/I1/VSS

/BL<0>

time (ns)

Figura 4.11: Consumo di corrente nelle varie tipologie di si-mulazione, dall’alto verso il basso: typical case, slow-slow efast-fast

48

Capitolo 5

Conclusioni

In questo elaborato e stata descritta la progettazione di una memoria associa-tiva a 18 bit le cui singole celle sono formate da una memoria SRAM ed unalogica di confronto XOR. I diciotto segnali provenienti dalle calle XORAMvengono processati da una logica combinatoria che esegue una operazioneNOR verso l’uscita.

Dell’intero layer e stato disegnato lo schema circuitale, il layout per larealizzazione su silicio e sono state eseguite simulazioni di funzionamento edi consumo corrente.

Il circuito e stato disegnato con tecnologia a 65 nm, utilizzando cellefull custom, giudicate il metodo migliore per minimizzare l’area occupata susilicio. Le alimentazioni sono portate in metal6.

Le dimensioni del layer progettato sono: 56, 84 µm×1, 535 µm = 87, 25 µm2,mentre quelle del circuito attuale sono 49, 945 µm × 1, 8 µm = 89, 90 µm2;la differenza fra le due aree si attesta circa al 3%.

Il funzionamento risulta corretto a 100 MHz, sia in tipycal case sia in worstcase, con valori logici ben definiti. Il circuito e in grado di funzionare anchealla velocita di 1 GHz, mentre il circuito attualmente in fase di prototipazione,essendo basato su una logica a precarica, potrebbe non arrivare a questevelocita di funzionamento.

Il consumo di corrente e quindi la potenza dissipata risultano abbastanzaalti rispetto a quelli del chip attuale: circa 2,2 A (2,6 W) contro 0,6 A(0,7 W). Questo consumo, e dovuto per la maggior parte al caricamento deinodi capacitivi della logica XOR ed alla corrente di crow-bar.

La potenza istantanea di un solo layer risulta poco indicativa in quanto,grazie alla possibilita di progettare la propagazione del segnale di clock inmodo da avere un determinato skew, e possibile distribuire la potenza dissi-pata nei picchi lungo un intervallo di tempo maggiore mantenendo il correttofunzionamento dell’intero chip.

49

CAPITOLO 5. CONCLUSIONI

Tabella 5.1: Caratteristiche dei due circuiti di memoriaassociativa.

Layer XORAM AMchip04

Larghezza 56, 84 µm 49, 945 µmAltezza ×1, 535 µm 1, 8 µmArea 87, 25 µm2 89, 90 µm2

Consumo 2,6 W 0,7 W

Il circuito attuale (AMchip04) ha un consumo medio piu basso in quantoe stato ottimizzato, prevedendo che in caso del mancato matching del datoimmagazzinato nelle prime quattro celle di memoria, non venga accesa larestante parte del layer.

Nella Tabella 5.1 sono stati riassunti i parametri principali di entrambi icircuiti.

Per diminuire i consumi del circuito sviluppato in questa tesi si potrebbeprocedere in futuro in maniera analoga a quanto fatto per il chip AM04, disa-bilitando parte del circuito in caso di mancato matching; infatti la quantitadi matching fra i dati immagazzinati ed i dati di bit line e molto bassa: vienestimata in circa cento pattern in tutto il chip.

50

Bibliografia

[1] A. Annovi, R. Beccherle, M. Beretta, E. Bossini, F. Crescioli, M. Del-l’Orso, P. Giannetti, J. Hoff, T. Liu, V. Liberali, I. Sacco, A. Schoe-ning, H. K. Soltveit, A. Stabile, R. Tripiccione, G. Volpi, “Asso-ciative Memory Design for the FastTrack Processor (FTK)at ATLAS” in Proc. IEEE Nuclear Science Symposium and MedicalImaging Conf. (NSS-MIC), Valencia, Spain, Oct. 2011, in press.

[2] K.Pagiamtzis and A. Sheikholeslami, “Content-addressable memo-ry (CAM) circuits and architectures: A tutorial and survey”IEEE, J. Solid State Circ., vol. 41, no. 3, pp. 712-727, Mar. 2006.

[3] T. Sharma, K. G. Sharma, B. P. Singh, and N. Arora, “New EfficientDesign for XOR Function on the Transistor Level” AIP Conf.Proc. 1324, 346 (2010); doi: 10.1063/1.3526229.

51

BIBLIOGRAFIA BIBLIOGRAFIA

52

Ringraziamenti

A conclusione di questo lavoro di tesi, e doveroso ringraziare:

Prof. Valentino Liberali, perche e stata una guida, nel mio primo lavorodi progettazione, sempre disponibile per chiarimenti e spiegazioni.

Dott. Alberto Stabile, che con pazienza mi ha guidato, sostenuto, consi-gliato e aiutato durante tutto lo svolgimento della tesi.

I miei genitori, mia sorella Chiara, nonni e zii, che mi hanno supportatoin questi anni di universita.

I miei amici, che mi sono stati vicino in questi anni, condividendo le gioiee sdrammatizzando i momenti di difficolta.

53