I dispositivi attivi lunedì 11 dicembre 2017pessina.mib.infn.it/Corsi_del_III_anno/I transistori in...

Transcript of I dispositivi attivi lunedì 11 dicembre 2017pessina.mib.infn.it/Corsi_del_III_anno/I transistori in...

1Le Logiche e le interfaccegpessina

I dispositivi attiviL’utilizzo di dispositivi logici di varia natura e l’interfaccia tra elementi con varia tipologia di uscita richiede la conoscenza del principio di funzionamento dei più comuni elementi attivi noti.

Il funzionamento di un elemento attivo, o transistor, è basato sulle proprietà conduttive del materiale di cui è composto.

Al fenomeno della conduzione rispondono in modo differente i materiali a seconda della composizione della loro struttura cristallina.

Quando gli atomi vengono avvicinati tra loro per formare il solido i livelli energetici ammessi agli elettroni si dividono in bande. Le bande formate conterranno N livelli ammessi che potranno essere riempiti al più da 2N elettroni, secondo il principio di esclusione di Pauli.

Le bande più profonde, ovvero vicine ai nuclei, saranno completamente piene. Gli elettroni non potranno muoversi tra i vari livelli di una banda perché tutti pieni.

Le cariche potranno quindi muoversi solo all’interno delle bande non completamente piene, che si troveranno alle energie più elevate, lontano dai nuclei. Al riguardo abbiamo 3 possibilità.

In funzione delle caratteristiche delle bande, si distinguono 3 differenti tipi di materiali: conduttori, semiconduttori ed isolanti.

Al fenomeno della conduzione partecipano solo le 2 bande più esterne, che vengono definite come banda di valenza e banda di conduzione.

La banda di valenza è la banda energetica più esterna completamente occupata da elettroni: in questa banda non potrebbe esserci movimento di carica, pertanto la conduzione è fortemente inibita qui.

La banda di conduzione è la banda più esterna non completamente piena di elettroni dove quindi il fenomeno della conduzione può verificarsi.

lunedì 11 dicembre 2017

2Le Logiche e le interfaccegpessina

Le bande energetiche nei solidi 1

Conduttori

SemiconduttoriIsolanti

I conduttori si presentano secondo 2 caratteristiche: banda di conduzione non completamente piena di elettroni, ma separata in energia dalla banda di valenza, oppure banda di valenza e conduzione non completamente separate in energia, con livelli liberi in banda di conduzione. In entrambi i casi sono presenti molti elettroni disponibili alla conduzione: sotto praticamente qualsiasi condizione i conduttori sono in grado di sopportare grandi flussi di carica.

I semiconduttori hanno le bande di valenza e conduzione separate in energia, in genere tra meno di 1 eV a poco meno di 2 eV, però sono presenti pochi elettroni in banda di conduzione: in condizioni normali sono debolmente conduttivi e non lo sono affatto a basse temperature.

Gli isolanti hanno le bande di valenza e conduzione separate in energia. A differenza che con i semiconduttori la separazione è in genere maggiore di 5 eV. Perciò la loro disponibilità alla conduzione è praticamente fortemente inibita.

L’aspetto rivoluzionario che caratterizzò l’elettronica negli anni ’50 fu il fatto che i semiconduttori possono essere trattati inmodo che il fenomeno delle conduzione possa essere modulato in funzione dell’alterazione delle caratteristiche fisiche imposte al reticolo cristallino.

3Le Logiche e le interfaccegpessina

Le bande energetiche nei solidi 2

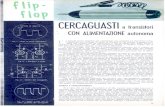

Fino a che non si sono introdotti i semiconduttori l’unico modo di implementare circuiti elettronici era basato sull’uso delle valvole:

Valvola= 1 transistor ARM= milioni di transistor

E’ eloquente l’evoluzione tecnologica ottenuta con lo sfruttamento dei semiconduttori.

4Le Logiche e le interfaccegpessina

Le bande energetiche nei solidi 3

Ecco qui un altro esempio: una delle prime memorie a nuclei magnetici di 4 x 18= 72 bit confrontata con una stecca di memoria di un PC attuale che contiene diversi GByte!

5Le Logiche e le interfaccegpessina

Le bande energetiche nei solidi 4

In sostanza abbiamo questa proporzione:

ENIAC: il primo PC (1946)

ENIAC: Electronic Numerical Integrator and Computer

6Le Logiche e le interfaccegpessina

I Semiconduttori drogati 1Consideriamo il Si (altri semiconduttori hanno comportamenti simili e vengono sfruttati in modo simile). Rispetto alle proprietà di conduzione elettrica il cristallo di silicio è formato da atomi che mettono in legame i 4 elettroni più esterni. Secondo questo schema i 4 elettroni considerati fanno parte della così detta banda di valenza e non possono girovagare per il materiale quando sottoposti a campo elettrico.

La scoperta fondamentale fu di capire che introducendo un atomo avente 5 elettroni di valenza in luogo di 4 nel reticolo cristallino il quinto elettrone rimane legato debolmente all’atomo intruso. Anche una piccola energia termica libera l’elettrone che può ora navigare per il materiale: questo elettrone può compiere il salto nella banda di conduzione.Introducendo una certa concentrazione N di atomi ‘donori’ per unità di volume si dice che il materiale è drogato con cariche negative.

All’opposto, introducendo nel reticolo cristallino atomi aventi 3 elettroni di valenza si forma una sorta di lacuna predisposta ad accettare l’arrivo di un elettrone che gli salta dentro. La lacuna a tutti gli effetti si può considerare come una carica positiva che si muove in verso opposto all’elettrone che gli salta dentro. La localizzazione della lacuna è proprio appena sopra la banda di valenza.Introducendo P atomi ‘accettori’ per unità di volume si dice che il materiale è drogato con cariche positive.

7Le Logiche e le interfaccegpessina

I Semiconduttori drogati 2

Banda di conduzione

Banda di valenza

Elettroni liberi nella banda di conduzione.

Atomi donori ionizzati, rimasti carichi positivamente.

Semiconduttore drogato N

Il livello energetico introdotto dai donori, Ed, è poco sotto la banda di conduzione, ca 50 meV nel Silicio.

Semiconduttore drogato P

Lacune libere di muoversi nella banda di valenza.

Atomi accettori ionizzati rimasti carichi negativamente

Il livello energetico introdotto dagli accettori, Ea, è poco sopra la banda di valenza, ca 50 meV nel Silicio.

Banda di valenza

Banda di conduzione

8Le Logiche e le interfaccegpessina

I Semiconduttori drogati 3

Banda di conduzione

Banda di valenza

Semiconduttore drogato N

Il livello energetico introdotto dai donori, Ed, è poco sotto la banda di conduzione, ca 50 meV nel Silicio.

Semiconduttore drogato P

Il livello energetico introdotto dagli accettori, Ea, è poco sopra la banda di valenza, ca50 meV nel Silicio.

Banda di valenza

Banda di conduzione

Gli el e le lacune sono dei gas a tutti gli effetti e soddisfano la statistica di Boltzmann che stabilisce che la probabilità di possedere una energia E per una particella è proporzionale a:

A temperatura ambiente l’energia termica KBT è pari a 26 meV e quindi sia gli el che le lacune sono in grado di compiere il saltino per andare a finire nella banda di conduzione e di valenza e potersi muovere.Il fenomeno della conduzione dei semiconduttori drogati è quindi possibile grazie all’ambiente che fornisce l’energia necessaria.I nostri dispositivi sono in grado di operare in modo parassita all’ambiente.

÷ e − ⁄E KBT

9Le Logiche e le interfaccegpessina

Il diodo 2Cosa significa in pratica:

- - - - - -- - -

-= lacuna= atomo ionizzato, fisso-

Lacune che se ne vanno

Lacune chearrivano

- - - - - -- - -- - - - - -- - -

+ + + + + + + + ++ + + + + + + + ++ + + + + + + + +

+ + + + + + + + +Elettroni cheescono

Elettroni cheArrivano -

= elettrone= atomo ionizzato, fisso+

p

n

In una barretta di tipo “p” applicando una differenza di potenziale si mettono in moto lacune: da una parte fuoriescono, dall’altra entrano per compensare le fuggitive.

In una barretta di tipo “n” applicando una differenza di potenziale si mettono in moto elettroni: da una parte fuoriescono, dall’altra entrano per compensare i fuggitivi.

IMPORTANTE: la quantità di carica che si mette in gioco, sia che siano elettroni o lacune, è uguale al numero di atomi o impurità droganti.

Qui vale quindi la legge di Ohm:

I ÷ SPρqv, v = µE

S=sezione trasversale ortogonale al moto, q= carica del singolo portatore, ρ=densità degli atomi introdotti, v=velocità dei portatori, µ=mobilità, E=VB/L campo elettrico applicato con L=lunghezza sbarretta.

VB

10Le Logiche e le interfaccegpessina

Il diodo 1La cosa più semplice che si possa realizzare con la tecnica del drogaggio dei semiconduttori sono le resistenze. Infatti il valore «Homico» di una resistenza risulta inversamente proporzionale alla densità dei portatori presenti nel materiale:

WL

q1

N1R

nµ=

La prima struttura più complicata che si possa realizzare è invece la così detta giunzione pn che si ottiene accoppiando tra loro 2 regioni drogate in modo opposto.

Il funzionamento è basato sul fenomeno del moto di diffusione e di deriva. Se non applichiamo nessun campo elettrico gli elettroni tenderanno a diffondere verso la zona P, dove ce ne saranno pochissimi, mentre le lacune tenderanno a diffondere verso la zona N, dove vale la stessa situazione. Nel processo la zona N si caricherà positivamente (un atomo scoperto per ogni elettrone che migra), mentre la zona P negativamente. Il processo di diffusione terminerà quando si costituirà un campo elettrico che cercherà di indurre un moto di deriva che si opporrà al moto di diffusione.All’equilibrio la corrente sarà ovviamente nulla.

Alla fine rimarranno 2 zone, dette di svuotamento e cariche una N ed una P, dove non saranno presenti cariche libere.

(µn(p)=mobilità degli elettroni (lacune)).

11Le Logiche e le interfaccegpessina

Il diodo 3

-= lacuna= atomo ionizzato, fisso-

- - - - - -- - -

- - - - - -- - -- - - - - -- - -

p

+ + + + + + + + ++ + + + + + + + ++ + + + + + + + +

+ + + + + + + + +

n

All’equilibrio la corrente è nulla. La cosa interessante si ha quando si applica una campo elettrico. La condizione di equilibrio si interrompe, ma il risultato è differente a seconda che si incoraggi o meno la promiscuità.

+-Vbi

-= elettrone= atomo ionizzato, fisso+

Gli elettroni e le lacune si comportano come un gas.

Non appena si affiancano le 2 barrette si instaura un modo di diffusione. In sostanza le lacune e gli elettroni si ricombinano come mandrilletti e continuerebbero a farlo se non nascesse una campo elettrico, ovvero la differenza di potenziale Vbi, che si oppone al moto che deriva dalla presenza di carica fissa (invidiosa)

Quindi cosa succede quando 2 barrette “n” e “p” si accostano.

ppo=concentrazione delle lacune nella zona p in condizioni di equilibrio, ppo ≅P;pno=concentrazione delle lacune nella zona n in condizioni di equilibrio, pno<<ppo;nno=concentrazione degli elettroni nella zona n in condizioni di equilibrio, nno ≅N;npo=concentrazione degli elettroni nella zona p in condizioni di equilibrio, npo<<nno.

12Le Logiche e le interfaccegpessina

Il diodo 4

n p- - - - -+ + + + + + +

+ + + + + + ++ + + + + + ++ + + + + + ++ + + + + + +

--- - - - - --- - - - - --- - - - - --- - - - - --

Applicando una polarizzazione così detta inversa, collegando il polo positivo del generatore alla zona “n”, si allontanano ulteriormente le cariche libere dalla giunzione le 2 barrette si impoveriscono a non c’è conduzione di corrente, ovvero la corrente è molto piccola: il dispositivo si comporta come un circuito aperto (impedenza ∞).

In sostanza, gli elettroni escono da sinistra, attirati dal polo positivo della batteria, ma non possono essere compensati a destra, perché la parte “p” non riesce a condurre elettroni, ovvero la attraversano in molto molto pochi. Il risultato è che tutti gli elettroni liberi se ne vanno lasciando gli ioni fissi caricati positivamente.

Un discorso perfettamente duale si può fare per le lacune nella zona “p”. Il risultato è che le 2 zone si trovano svuotate di cariche libere. Le uniche cariche in moto sono quelle poche che si creano nelle 2 zone per agitazione termica.

13Le Logiche e le interfaccegpessina

Il diodo 5

n p-+

++++

----

Se invece polarizziamo il dispositivo in modo diretto, con il polo positivo del generatore connesso alla zona “p”, siamo in grado di iniettare cariche che compensano gli atomi ionizzati e possono diffondere nella zona opposta, la regione svuotata si riduce molto: in questa situazione la corrente che scorre può essere molto elevata.

Ora favoriamo la promiscuità: gli elettroni entrano da sinistra e vanno verso la giunzione, attraversandola, qui si ricombinano con le lacune della zona “p”. A questo punto dalla parte destra altre lacune vengono immesse per compensare la ricombinazione.

Un ragionamento duale vale per le lacune che attraversano la giunzione.

Molto importante: la corrente totale è contribuita sia dalle lacune che si muovono in un senso che dagli elettroni che si muovono in senso opposto:

pn III +=

Dove con In intendiamo la corrente degli elettroni che dalla zona n sono spinti nella zona p dal campo applicato. Viceversa, con Ipintendiamo invece la corrente dovuta alle lacune che dalla zona p sono spinte nella zona n dallo stesso campo applicato.

14Le Logiche e le interfaccegpessina

Il diodo 6L’ipotesi di partenza, e quello che succede in pratica per costruzione tecnologica, è che la corrente che si instaura quando polarizziamo direttamente il diodo mette in moto una quantità di carica molto piccola rispetto a quella presente nel semiconduttore. Si dice che si lavora in condizioni di bassa iniezione.

Allo stesso modo la carica che si muove nella parte p è data in parte dalle lacune spinte dal campo elettrico ad attraversare la barriera, Ip, ed in parte è data dalle lacune che devono compensare gli elettroni che sopraggiungono dalla zona n, che attraversano la barriera, Ipn, e che non sopravvivono e si ricombinano prima di arrivare alla fine della zona p.

Ovviamente abbiamo che Inp=Ip e che Ipn=In.

Si è detto che la densità di droganti introdotta nelle 2 zone non deve necessariamente essere simile. Questo implica che le 2 correnti possono avere intensità molto diversa.

La corrente in un conduttore/semiconduttore è in fondo in fondo legata al campo elettrico dalla legge (di Ohm):

n p-+

++++

----

Ip

In Ipn

Inp

Ip+IpnIn+Inp

Quindi, nella parte n gli elettroni si muovono in parte spinti dal campo elettrico, In, ed in parte sono quelli che devono compensare la corrente delle lacune che provengono dalla zona p, che attraversano la barriera, Inp, e che non sopravvivono e si ricombinano prima di arrivare alla fine della zona n.

I ÷ ρ × e × µ × E

Dove ρ è la concentrazione di carica libera. Perciò, a parità di campo elettrico applicato, E, la corrente sarà tanto più elevata quanto più alta sarà la concentrazione di carica.

15Le Logiche e le interfaccegpessina

Il diodo 7

Nel caso del nostro diodo, quindi, se applichiamo una differenza di potenziale, ovvero un campo elettrico, capace di generare la corrente voluta IB ed abbiamo che n >> p, è chiaro che ci aspettiamo che questa corrente sarà in massima parte dovuta agli elettroni, un esercito più cospicuo, visto che il campo elettrico applicato agli elettroni ed alle lacune è il medesimo, ma la concentrazione molto differente.

In effetti si può mostrare che nel diodo vale che:

Quindi è possibile fare in modo che la corrente dominante sia quella di un tipo di portatori, agendo sul rapporto dei drogaggi.

Questa proprietà è sfruttata nella realizzazione dei transitori bipolari, come vedremo tra poco.

p n-+

++++

----

Inp

Ipn In

IpIn+InpIp+Ipn

In ÷1P

expqVa

KT

Ip ÷1N

expqVa

KT

Va

IB

16Le Logiche e le interfaccegpessina

Il diodo 8

n p- - - - -+ + + + + + +

+ + + + + + ++ + + + + + ++ + + + + + ++ + + + + + +

--- - - - - --- - - - - --- - - - - --- - - - - --

n p-+

++++

----

Di nuovo: la corrente è contribuita da 2 flussi: lacune che si muovono in un senso ed elettroni che si muovono in senso opposto. Questo sia che la polarizzazione sia diretta che inversa.

qVa0 KT

I I exp 1 = −

Riassumendo: corrente praticamente nulla nel caso di polarizzazione inversa e dipendente esponenzialmente dalla tensione applicata in caso di polarizzazione diretta. Si dimostra che:

Il ginocchio è a circa 0.6 – 0.7 V per i diodi standard. Esiste una categoria speciale di diodi detti Schottky in cui il ginocchio è a 0.2 -0.3 V.

Polarizzazione inversa

Polarizzazione diretta

Con:pn0 III +=

I= scala logaritmica

17Le Logiche e le interfaccegpessina

Riassunto diodi

Il diodo è un dispositivo a 2 terminali così detto rettificatore.

Quando polarizzato inversamente non si lascia attraversare da corrente, ovvero si lascia attraversare da una corrente trascurabile, detta parassita. Offre una impedenza resistiva elevata, ed una capacità che dipende dalla tensione applicata:

( )Abiss VV

NPPN

q2 WA

WC −

+ε=

ε= A=area della giunzione

Quando polarizzato direttamente il diodo si può modellizzare come un generatore di tensione, di valore circa 0.7 V per il Silicio, ed impedenza dinamica (KT/q)/ID:

VBB>Vbi

RVVI biBB −

=

RVO≈Vbi≈0.7 VRD≈VT/I, VT=KT/q

IMPORTANTE

C’e’ una tipologia di diodo in cui la parte p viene realizzata con un metallo avente opportune proprietà. Questo fa si che la barriera di potenziale alla giunzione sia più bassa. Quello che si ottiene è:

Vbi≈0.3 VMaggiore velocitàMaggiore corrente parassita in regione inversa.

Questi diodi vengono chiamati diodi Schottky ed hanno una grossa importanza nei circuiti digitali:

==

∆∆

=

KTqI

R1

VI ,expII

DKTaqV

o

18Le Logiche e le interfaccegpessina

Rbias Vbias

Il diodo LED 1Il diodo LED ( Light Emitting Diode) è divenuto un dispositivo estremamente importante che sta rivoluzionando completamente il mondo dell’illuminazione.

Il processo di generazione della luce in un diodo LED è statistico e legato alla quantizzazione.Polarizziamo direttamente un diodo. Avremo elettroni che scorreranno nella banda di conduzione e lacune nella banda di valenza a generare la corrente.Durante il percorso però alcuni elettroni potranno cadere dalla banda di conduzione alla banda di valenza, ricombinandosi con lacune. In quel caso si deve liberare un’energia pari alla differenza tra banda di conduzione e valenza, EG. Questa energia sfuggirà portata via da un fotone: EG=hν, con ν essere la frequenza.

Se la frequenza ν sta nello spettro visibile noi la percepiremo attraverso un colore che dipenderà quindi da EG, ovvero dal semiconduttore. Quindi la selezione del semiconduttore ci permette di ottener luce del colore desiderato: bianco, giallo, verde, …

Questo fenomeno statistico dipende dalle caratteristiche fisiche del materiale e riguarderà qualche % di tutti gli elettroni che attraversano il diodo.

19Le Logiche e le interfaccegpessina

Il diodo LED 2

Qui possiamo vedere le caratteristiche del fotone emesso dal diodo in funzione del materiale per i diodi LED più diffusi nelle applicazioni nel così detto spettro visibile.

La tensione che si sviluppa ai capi del diodo quando polarizzato direttamente dipende molto dal gap di energia EG,

20Le Logiche e le interfaccegpessina

Il diodo LED 3

Qui si vede in modo ancora più evidente il comportamento delle curve tensione-corrente in relazione al tipo di diodo.In ogni caso la corrente è sempre esponenzialmente dipendente dalla tensione ai capi del diodo:

I = I0expqVbias

KT

21Le Logiche e le interfaccegpessina

Rbias Vbias

Il diodo LED 4

Dal punto di vista pratico il successo del diodo è la sua capacità di produrre luce sprecando poca energia, al contrario di quello che avviene nelle normali lampadine a filamento o alogene.

All’atto pratico l’efficienza del funzionamento del diodo come sistema di illuminazione la si massimizza se la potenza è essenzialmente dissipata dal diodo e non anche dalla resistenza Rbias che è inserita per limitare la corrente.

La potenza totale dissipata è infatti:

Ibias

+ -Vdiode

WT = Wdiodo + Wres = VdiodeIbias + Ibias2 Rbias

Per cui se la resistenza fosse nulla avremmo il minimo di energia spesa.

22Le Logiche e le interfaccegpessina

Rbias=0 Vbias

Il diodo LED 5

Perché serve la resistenza di limitazione, a meno di adottare tecniche ad hoc. Se Rbias fosse nulla la corrente nel diodo sarebbe esponenzialmente dipendente da Vbias:

I = I0expqVbias

KT

Ibias

+ -Vdiode

Quindi accadrebbe che un piccolo errore di polarizzazione, o la semplice dispersione in produzione del valore di Vdiode, potrebbe comportare grosse variazioni di corrente che potrebbe portare ad una debole illuminazione o la rottura, o eccessiva usura, del componente.

23Le Logiche e le interfaccegpessina

Il diodo LED 6

La presenza della resistenza Rbias di valore opportune determina che:

Vbias = IbiasRbias + Vdiode

Perciò, siccome Vdiode dipende dal log della corrente, si può ritenere pressoché costante e quindi la corrente viene a dipendere linearmente da Vbias, piuttosto che esponenzialmente.

In questo modo anche se Vbias non fosse precisa, non si rischierebbe di dovere erogare una corrente esagerata. Il collo di bottiglia di questa soluzione è che ai capi della resistenza si instaura una differenza di potenziale che determina una aumento della potenza dissipata: IbiasRbias. Tutte le soluzioni circuitali attuali nei sistemi di alimentazione sono dedicate alla minimizzazione di questa potenza inutilizzata a generare luce.

Rbias Vbias

Ibias

+ -Vdiode

24Le Logiche e le interfaccegpessina

Il diodo LED 7

In questo modo la resistenza da porre in serie è molto più piccola perché si aumenta la differenza di potenziale necessaria a fare circolare la corrente nella serie di diodi: quando l’onda parte da zero si usa solo un diodo, poi se ne mette in serie un secondo quando l’onda supera VD, poi un terzo quando l’onda supera 2VD, e così via.

Una tecnica recente è indicata come AC bias e consiste nel mettere in serie stringhe di diodi di cui una parte viene mantenuta cortocircuitata fino a che la corrente, ovvero la tensione applicata, non supera un certo valore.

25Le Logiche e le interfaccegpessina

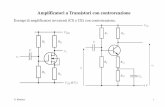

Il Transistor Bipolare 1

P1In ÷

N1Ip ÷

+ + + ++ + + ++ + + ++ + + ++ + + +

n p+++++

-----

Polarizzazione diretta

-----

-----

Emettitore Base Collettoren

Possiamo capire come funziona un transistore bipolare, formato da 2 giunzioni così dette back-to-back:

Cominciamo col polarizzare la giunzione Base-Emettitore direttamente, lasciando non connesso il Collettore.

Facciamo in modo che l’Emettitore sia molto più drogato della Base, così che la corrente di Emettitore sia molto più grande di quella di base. Se il Collettore non è connesso il comportamento è quello di un diodo.

Notiamo che alla giunzione Base Collettore si forma una regione di svuotamento derivante dalla diffusione.

Quello illustrato è il così detto transistore npn. Esiste ovviamente il duale, il transistore pnp, per il quale le correnti sono tutte capovolte.

26Le Logiche e le interfaccegpessina

Il Transistor Bipolare 2

A questo punto polarizziamo inversamente la giunzione Base Collettore:

+ + + + + + ++ + + + + + ++ + + + + + ++ + + + + + ++ + + + + + +

n p+++++

-----

Pol. diretta

-----

-----

Emettitore Base Collettoren

Pol. inversaPol. diretta Pol. inversa

In questo caso gli elettroni che arrivano nella Base si trovano attirati dal campo elettrico applicato al Collettore e sono favoriti ad attraversarla e passare nel Collettore.

Ma attenzione: gli elettroni per potere arrivare al Collettore devono sopravvivere al passaggio nella Base. Questo è possibile solo se 1) la Base è molto stretta.

Se questo è il caso allora la corrente di Collettore è pressoché uguale a quella di Emettitore e:

2) Il Rapporto NE/PB si riesce a fare di un fattore che può spaziare da 100 a 500.

Il risultato è che con una piccola corrente di Base (l’ingresso o terminale di controllo) si riesce a controllare una grossa corrente di Collettore (l’uscita o terminale di uscita), il guadagno di corrente essendo il termine hFE trovato sopra, dipendente da parametri tecnologici, i drogaggi di Base e Collettore.

Più precisamente:

IC ≈ IE ÷1PB

, IB ÷1

NE⇒

IC

IB÷

NE

PB= 𝐡𝐡𝐅𝐅𝐅𝐅

IE = IB + IC = IB 1 +IC

IB= 1 + hFE IB

27Le Logiche e le interfaccegpessina

Il Transistor Bipolare 3

Riassumendo:

+ + + + + + ++ + + + + + ++ + + + + + ++ + + + + + ++ + + + + + +

n p+++++

-----

Pol. diretta

-----

-----

Emettitore Base Collettoren

Pol. inversaPol. diretta Pol. inversa

La ricetta per costruire un transistore bipolare segue 2 passi fondamentali: drogaggio dell’Emettitore molto più corposo della base e Base molto stretta per minimizzare la ricombinazione delle cariche che provengono dall’Emettitore.

Abbiamo che:

Dal momento che:

Cioè, se vogliamo controllare la corrente di Collettore attraverso la tensione di Base abbiamo una dipendenza esponenziale.

IC

IB÷

NE

PB= hFE e IE = IB + IC = 1 + hFE IB

IB = IB0 expqVBE

KT− 1

IC = hFEIB = hFEIB0 expqVBE

KT− 1

28Le Logiche e le interfaccegpessina

Uso del Transistor Bipolare: la configurazione E comune

Vi

VoRL

RB

Il Tr. Bipolare è quindi un dispositivo a 3 terminali dove la corrente di collettore è controllabile, entro certi limiti, in modo lineare da una piccola corrente di base.

Il potenziale di collettore, per grandi correnti, dipenderà perciò dall’impedenza connessa secondo la legge:

VCC

Dal punto di vista digitale interessano più che altro i grandi segnali, visto che occorre commutare tra 2 stati ben definiti.

Cosa succede quando si ha che hFEIBRL>VCC?

Ciò che accade è che la giunzione B-C non è più polarizzata inversamente, sia l’E che il C inondano ora la B di cariche: il guadagno di corrente diviene ora poco significativo. Le 3 correnti vengono ad avere valore simile. Questo regime è detto di saturazione.

BE

C

VCC

LCC

RV

Se VBE=0 V, quindi IB=0 A, ovviamente VOdiviene uguale a VCC perché in RL non passa corrente.

Dalla relazione sopra sembrerebbe che VO dovrebbe diventare < 0 V: impossibile visto che la tensione minima di lavoro nel circuito è proprio 0 V.

Vo = VCC − ICRL = VCC − hFEIOBexp ⁄qVBE KT RL

29Le Logiche e le interfaccegpessina

Uso del Transistor Bipolare: la configurazione E comune

NOTE IMPORTANTI:

1. Il comportamento riscontrato dimostra che il guadagno di corrente dipende dal valore della corrente di ingresso;

2. I tr. Bipolari sono dispositivi controllati con una corrente di ingresso: non va mai trascurata la presenza di una resistenza RB in serie alla base per limitare la corrente di base nei circuiti digitali.

Abbiamo ottenuto che:

Se VBE, o IB è grande l’uscita diventa un valore basso, mentreSe VBE e quindi IB sono zero l’uscita assume un valore elevato:

Il transistor si comporta come invertitore, nella configurazione considerata.

RB

Vi

Vo

VCC Dal punto di vista digitale il transistor bipolare possiamo cederlo come un interruttore comandato: se Vi=0 V l’interruttore è aperto, cioè l’uscita è alta, se Vi= VCC l’interruttore è chiuso, cioè l’uscita è 0 V.

Ora, c’e’ una questione fondamentale: se Vi=0 V il circuito di ingresso non assorbe nessuna corrente, quindi non dissipa potenza.Se Vi=VCC nel circuito di ingresso scorre la corrente ∼VCC/RB, per cui abbiamo una dissipazione di potenza.Abbiamo la necessità di avere presente la resistenza RB per limitare la corrente. Infatti se così non fosse avremmo una corrente di base esponenzialmente dipendente da VCC:

IB = IB0e ⁄qVCC KT

30Le Logiche e le interfaccegpessina

La logica TTL 1Un circuito logico deve operare per essere in grado di discriminare tra 2 stati in modo non ambiguo: 0 e 1.

Tuttavia abbiamo da considerare l’operazione di componenti attivi che lavorano agli estremi delle loro caratteristiche.

Pertanto non si può certamente pretendere che i 2 livelli logici corrispondano a 2 precisi valori di tensione.

Piuttosto dovremmo considerare una coppia di intervalli di tensione che possano essere i maggiori candidati.

Esistono differenti tipologie logiche: TTL, CMOS, ECL, ecc. ognuna avente caratteristiche particolari riguardanti la velocità, la dissipazione, ecc. Ciò che è importante tenere in conto quando si considera il passaggio tra una logica e l’altra sono appunto i differenti intervalli di riconoscimento dei 2 livelli logici.

I circuiti TTL utilizzano transistori bipolari. Le loro soglie si devono confrontare con la tensione di funzionamento di una giunzione B-E, 0.7 V.

La soglia alta si confronta anch’essa con 2VBE e per dare ulteriore margine viene indicata a circa 2 V, come soglia di scatto.

La soglia fissata a ±VBE rispetto al valore di paragone di 2VBE consente un buon margine di rumore. Se si sta entro I termini stabiliti non si incorre in nessuna interpretazione non desiderata del segnale di ingresso.

Di fatto la soglia bassa di un circuito TTL si confronta con 2VBE e viene indicata a 0.8 V come limite di scatto.

31Le Logiche e le interfaccegpessina

La logica TTL 2

Le soglie di ingresso si determinano considerando il comportamento di Q2Q5 e D1X e D1Y.

La tensione di uscita nello stato basso coincide con la tensione di saturazione di Q5 a meno del fatto che è un tr. Schottky. Quindi sarà circa compresa tra 0.4 V e 0.5 V.

La tensione di uscita nello stato alto al massimo coincide con VCC-2VBE, circa 3.8 V. Il livello minimo dipende dall’assorbimento del carico. Tale livello è limitato dalla resistenza R2. In genere la tensione di uscita difficilmente scende sotto i 2.7 V. Quando Vo è 2.7 V la tensione di collettore di Q3 è circa 3.8 V che equivale ad una corrente erogata di circa 10 mA, estremamente elevata.

Si osserva che i transistori bipolari esistono nelle 2 forme: npn e pnp, aventi comportamento complementare nel verso delle correnti.

32Le Logiche e le interfaccegpessina

La logica TTL 3

In un dispositivo digitale che fa uso di transistori bipolari occorre la presenza di resistenze in serie ai terminali di Base per limitare la corrente assorbita. Questo pone dei problemi di spazio occupato dai resistori.

Inoltre la corrente di base è un consumo di energia che rimane anche quando la porta non è usata, se un transistor non è interdetto ma in saturazione.

I transistori bipolari non si adattano quindi alla integrazione su larga scala.

Per questo occorrono dispositivi pilotati in tensione, piuttosto che corrente, nelle applicazioni digitali.

33Le Logiche e le interfaccegpessina

I transistori MOS 1I transistori MOS sono i dispositivi ideali nelle applicazioni digitali perché pilotati in tensione. Si basano ancora sull’idea di un elettrodo che consente di modulare la corrente del canale di uscita. Ma questo elettrodo assolve al controllo in tensione, piuttosto che in corrente.

Il principio di funzionamento è sensibilmente differente, anche più semplice, rispetto a quello dei diodi e dei dispositivi bipolari.

n+ n+

Ossido

p

VD

VG

sourcegate drain

VG<VTCorrente inibita

MetalIsolante

Pariamo dalla situazione di piccola o nulla polarizzazione.

Il dispositivo di controllo si chiama Gate ed è separato da quello che sarà il canale di conduzione da un isolante. In questo modo tra Gate e canale di conduzione si è formata una capacità.

Se la tensione VG è nulla tra i terminali di Source e Drain non c’e’ carica che possa muoversi perché il canale è un substrato “p” e si viene a formare una giunzione “pn” polarizzata inversamente tra Drain e canale.

Quindi VG sufficientemente piccola o nulla determina il dispositivo nello stato di interdizione.

34Le Logiche e le interfaccegpessina

I transistori MOS 2

Z(x)n+ n+

Ossido

p

VD

VG

sourcegate drain

VG<VT e VG>0Si crea uno strato di carica negativa fissa sotto l’ossido

x

ID

Co= capacità per unità si superficie.

Aumentiamo il valore della tensione di Gate. Abbiamo un effetto capacitivo: sulla metallizzazione di Gate si avranno cariche positive mentre nel canale si accumuleranno cariche negative.

Però attenzione: inizialmente quello che accade è che le lacune fuggono lontane dalla superficie isolante-semiconduttore e quello che rimane è carica negativa composta da atomi ionizzati, che non possono certamente muoversi.

Perciò per valori sufficientemente bassi di VG si forma uno strato di carica negativa, ma non c’è ancora possibilità di conduzione tra Source e Drain.

La carica che andiamo a formare nel canale è, ovviamente:

GoVCAreaQ ×=

Dove Co è la capacità per unità di superficie, e Area è la superficie sotto il Gate, di cui una dimensione è ortogonale alla superficie del foglio.

35Le Logiche e le interfaccegpessina

I transistori MOS 3

Z(x)n+ n+

Ossido

p

VD

VG

sourcegate drain

VG>VT si attirano elettroni, che possono ora muoversi tra Source e Drain.

x

ID

Co= capacità per unità si superficie.

Dobbiamo ancora fare qualche considerazione.

Aumentando ulteriormente la tensione di Gate le lacune fuggiranno tutte e, per compensare la carica positiva che si forma sulla parte superiore dell’ossido gli el sono attirati sotto l’ossido. A questo punto questi elettroni possono muoversi parallelamente all’ossido se si applica un campo elettrico tra drain e source.

Supponiamo di fissare VG ad un valore che ci crei un canale conduttivo e facciamo salire la tensione di Drain.

Come detto sopra, l’eccesso di carica negativa formata da elettroni è libera di muoversi, se applichiamo il campo elettrico tra Drain e Source: si è formato una canale di conduzione tra Drain e Source.

Questo canale è quindi attivo quando la tensione di Gate supera un valore così detto di soglia VT, oltre il quale vengono richiamati el liberi sotto l’ossido. VT dipende dal livello di drogaggio del substrato “p”:

TG VV ≥

36Le Logiche e le interfaccegpessina

I transistori MOS 4

Z(x)n+ n+

Ossido

p

VD

VG

sourcegate drain

x

ID

Co= capacità per unità si superficie.

Da dove provengono questi el che si accumulano sotto l’ossido? Sono i pochi elettroni provenienti dal substrato “p” a dai pozzetti “n” di Source e Drain.

Ora, se teniamo fisso VG, al crescere della tensione di Drain si rimpicciolisce la differenza di potenziale, ddp, tra Drain e Gate, ovvero si restringe il canale verso il terminale di Drain. Questa ddp potrebbe anche diventare minore di VT.

Quello che succede però, anche quando la ddp tra Drain e Gate diviene minore di VT non è uno strozzamento del canale con annullamento della corrente, per fortuna, ma il fenomeno sotto:

VDG < VT

37Le Logiche e le interfaccegpessina

I transistori MOS 5Vediamo che succede.Partiamo da valori piccoli di VDS. Il canale si comporta come un resistore e vale la legge di Ohm che si riassume nel dire:

S G D

Saturazione µRiduzione dellasezione Effetto dello Strozzamento

Per la conservazione della carica la corrente deve essere uguale in ogni sezione del canale. Al drain, se aumentiamo VDS, h si riduce, per cui, per mantenersi la corrente simile a quella nel resto del canale, la velocità vcdal drain deve aumentare.

Per ragioni fisiche la velocità non può aumentare all’infinito ed infatti satura ad un certo valore massimo vcdmax che si otterrà ad un certo valore hmin dell’ampiezza del canale al drain.

IDS ÷ AhρqvcdS G DS=Ah è la sezione ρ=densità di caricaq= carica elettronevcd=velocità dell’elettrone al D,vcd=µEd, µ=mobilità, Ed=campo elettrico al D

h

Quindi la corrente non aumenterà più in valore, ma resterà costante, limitata dalla saturazione della velocità:

A questo punto la legge di Ohm smette di valere.Aumentando ulteriormente la tensione VDS la velocità e la strozzatura rimarranno del medesimo valore, ma la stozzatura si estenderà verso il source:

IDS ÷ Ahminρqvcdmax

38Le Logiche e le interfaccegpessina

I transistori MOS 6

( )2TGSoD VVCL2

WI −µ≈

Essendo il canale di conduzione formato per effetto capacitivo. Ed essendo l’effetto capacitivo dipendente linearmente dalle tensioni in gioco si viene a dimostrare che la relazione tra corrente di Drain e potenziale di Gate è quadratica:

Però ora abbiamo ottenuto l’importante risultato che la corrente di uscita è controllata dalla tensione di ingresso e nel terminale di ingresso non prevediamo la presenza di corrente, se non quando si ha la commutazione perché dobbiamo aggiungere o togliere cariche: la potenza dissipata è sostanzialmente dinamica.

OSSERVAZIONE: quello che abbiamo studiato è un MOS di tipo N. Ovviamente il MOS a canale P è il suo duale, dove tensioni e correnti sono invertite.

39Le Logiche e le interfaccegpessina

I transistori MOS 7

VCC

Vi

Vo ( ) L2

TioCCLDCCo RVVCL2

WVRIVV −µ−=−=

Anche qui, come nel caso del transistore bipolare abbiamo che il MOS si comporta da invertitore: se Vi è grande l’uscita diventa piccola, mentre se Vi è di valore trascurabile l’uscita diventa VCC.

RL

ID

Abbiamo 2 significative differenze rispetto al transistore bipolare:

1. La transizione avviene con un guadagno che ora è quadratico piuttosto che esponenziale, ma questo non comporta svantaggi, almeno nei circuiti digitali.

2. Non serve nessuna resistenza in serie al Gate perché non è prevista corrente statica da limitare all’ingresso: questo ha fatto la fortuna dei transitori MOS nei circuiti digitali (ed ha cambiato il modus viventi nostro!), perché in questo modo la potenza dissipata nel circuito di ingresso è minimizzata e si risparmia l’area occupata dalla resistenza da porre in serie all’ingresso. Area che è in genere confrontabile se non maggiore a quella del transistore stesso.

Ma le cose sono ancora meglio se passiamo alla logica CMOS…

40Le Logiche e le interfaccegpessina

I transistori MOS 8

( ) L2

TioCCLDCCo RVVCL2

WVRIVV −µ−=−=

VCC

Vi

Vo

RL

ID

In questa configurazione se il segnale di ingresso fosse nello stato alto la tensione di uscita si porterebbe nello stato basso, visto che il MOS si comporterebbe come un interruttore chiuso:

VCC

Vi alto

Vo≈0 VRL

ID

La potenza dissipata è data da:

L

2CC

D RVP ≈

Se potessimo fare in modo che RL potesse assumere un valore ∞quando Vi si trovasse nello stato alto avremmo una potenza dissipata trascurabile: PD≈0 V.

VCC

Vi basso

Vo≈VCCRL

ID

Viceversa quando Vi è basso l’uscita diventa alta ed il MOS si comporta come un interruttore aperto.

In questo caso otterremmo una transizione veloce dell’uscita se RL fosse di valore piccolo e non dissiperemmo potenza statica perché la corrente che scorrerebbe in RL sarebbe trascurabile, trovandosi in serie ad un’impedenza elevata (il MOS aperto).

È possibile soddisfare entrambe le condizioni se RL fosse un carico “attivo” e non un semplice resistore:

41Le Logiche e le interfaccegpessina

MP

I transistori MOS 9Ora abbiamo che nel momento in cui Vi si porta basso MN si spegne ed il MOS P, MP, si accende: MN è un interruttore aperto mentre MP un interruttore chiuso:

Vo≈Vcc

La potenza dissipata è quindi trascurabile.

Per complemento, quando Vi si porta ad una valore alto è il MOS N, MN, a comportarsi come un cortocircuito, mentre il MOS P, MP, si comporta come un aperto circuito. La dissipazione è ancora trascurabile, almeno dal punto di vista statico.

Quello ottenuto è il funzionamento della logica CMOS (ComplementaryMOS) in cui sfruttando la dualità dei MOS P ed N si riescono ad ottenere porte logiche a dissipazione statica nulla. L’unico frangente in cui si ha assorbimento di corrente è durante la transizione, in cui si caricano/scaricano le capacità presenti ai nodi e scorre una piccola corrente nel breve istante in cui entrambi i MOS sono attivi contemporaneamente.

In questo approccio si usano solo transistori e non resistenze: l’ingombro è altresì minimizzato.

Regola fondamentale nei circuiti CMOS: il segnale di ingresso deve sempre essere alto o basso, mai stare nel mezzo, altrimenti entrambi i MOS sono operativi e la dissipazione aumenta a dismisura.

VCC

Vi

Vo

MP

MN

VCC

Vi bassoMN

MP

Vo≈0 V

VCC

Vi altoMN

42Le Logiche e le interfaccegpessina

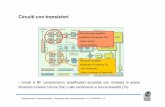

La logica CMOS 1

La soglia VT di un MOS dipende dal processo di fabbricazione. Nei CMOS a 5 V è sensibilmente differente che per la logica TTL:

Di conseguenza il mischiare dispositivi in logica CMOS con dispositivi in logica TTL va fatto con molta cautela.

I MOS tr. Si prestano in modo molto naturale alla realizzazione di circuiti logici:

Il circuito più semplice è l’invertitore che si può realizzare con solo 2 MOS senza la necessità che vi sia presente alcuna resistenza:

Quando VIN è alto il NMOS è in regime ohmico, mentre il PMOS risulta spento. La corrente assorbita dalla porta è nulla. Nel caso opposto, VIN basso, è il PMOS ad essere in regime ohmico, mentre lo NMOS è spento. Anche qui l’assorbimento di corrente della porta è nullo. Nei 2 stati la corrente può solo essere assorbita da un carico connesso all’uscita.

L’unico momento in cui la porta assorbe corrente di proprio è durante la commutazione, per un breve intervallo di tempo

43Le Logiche e le interfaccegpessina

La logica CMOS 2

=

=

NAND L’implementazione circuitale delle porte logiche in tecnologia CMOS è molto compatta. Questo ha determinato il loro successo.

Una porta NAND a 3 ingressi si realizza con solo 6 MOS, senza l’ausilio di resistori.

Cominciamo a vedere qualche definizione:il fan-in

Di principio al circuito sopra dovrei potere aggiungere ingressi. Basterebbe inserire una coppia di MOS complementari. In realtà dal punto di vista del buon funzionamento le cose vanno tutte bene fino a che non si hanno tutti gli ingressi alti, ovvero i MOS n sono tutti, o almeno uno, chiusi

I MOS accesi sono quelli che operano in regime Ohmico.

Nelle 2 resistenze di canale RN non scorre corrente perché Q1 è aperto.

La corrente scorre solo in RP visto che Q2 è chiuso. Se avessimo altri MOS p chiusi la condizione sarebbe ancora meglio perché le resistenze RP sarebbero tutte in parallelo e la corrente nel carico potrebbe essere adeguata..

RP

VCC

Q1

Q3

Q5

Q2

Q4 Q6

RN

RN

RL

CONSIDERAZIONE: implementando MOS di area piccola si riescono a realizzare circuiti molto densi di porte. Da qui la corsa alla realizzazione di MOS ultra piccoli; ovvero con distanza tra Source e Drain dell’ordine della decina di nm.

44Le Logiche e le interfaccegpessina

La logica CMOS 3

La cosa diventa critica quando tutti gli ingressi sono alti.In questo caso la presenza di un carico verso l’alimentazione positiva può determinare una partizione che potrebbe alzare troppo il potenziale di uscita.

Da: DSDS

TGSoD V2

VVVLWCI

−−µ≈

Per VDS piccole, tipiche dei regimi ohmici, l’impedenza RN risulta:

( ) ( ) MOSN del sogliaV ,VV

1WL

VV1

WLR TN

TNCCmk1

TNGSoC1

N =−

=−

≈ µ

RP

Q1

Q3

Q5

Q2Q4 Q6

RN

RN

RN

RL

VCC

La quantità km=µCo è un parametro tecnologico. RN può essere resa piccola predisponendo larghezze adeguate, o piccole lunghezze, o tensioni applicate elevate.

Non tutti questi parametri sono liberi. Infatti gate troppo corti pongono limiti sulla massima tensione applicata per via del campo elettrico sopportabile.

Considerando larghezze W elevate si occupa area e si introducono elementi capacitivi parassiti che possono limitare le velocità di transizione. Inoltre si aumenterebbe la corrente assorbita durante le commutazioni.

Per esempio per km=30 µA/V2 W/L=1 e VTN=1 V si ottiene:

RN=16.6 KΩ

Mentre per W/L=10 RN risulta 10 volte minore: RN=1.6 KΩ.

45Le Logiche e le interfaccegpessina

La logica CMOS 4Per cercare di ottimizzare e velocizzare il circuito si adotta una tecnica mista. Ovvero si usano MOS a piccola area all’interno del circuito dove le impedenze di carico sono note: possono essere solo gate. In questo modo viene consentita una maggiore elasticità nel numero di ingressi alle porte.

I terminali di uscita della rete vengono fatti pilotare da MOS di grande area, aventi impedenza in regime ohmico sufficientemente bassa. Qui si entra nel discorso del fanout, ovvero quante porte il circuito può pilotare?

NOR

VCC

R1

R2

Supponiamo per genericità che l’impedenza di uscita sia connessa verso massa e verso VCC.

Possiamo modellizzare sia il circuito di uscita che il carico connesso.

R1

R2

VCC VCC

RP

RN

MOS

Carico

Supponiamo l’uscita bassa, VCC=5 V, R1=1 KΩ e R2=3 KΩ e sia RN=500 Ω

VCC

RN

MOS

Carico

R1

R2 V 5.1VRR

RV

6.428RR

RRR

CC1E

Eo

N2N2

E

=+

=

Ω=+

= La tensione di uscita è al limite della soglia di rispetto tra stato basso e stato alto.

Solo uno dei 2 MOS è attivo in condizioni statiche

46Le Logiche e le interfaccegpessina

La logica CMOS 5

Gli effetti delle impedenze di carico si traducono in un livello della tensione di uscita che si discosta da quello agli estremi.

Questo fenomeno ha un doppio effetto: da un lato c’è pericolo che il livello in considerazione sconfini nello stato logico indesiderato. Dall’altra parte può provocare un incremento della potenza dissipata che potrebbe essere non trascurabile.

Infatti se l’ingresso da VDD si abbassa si ha che la RN aumenta, ma diminuisce la RP del MOS da un valore molto elevato. Vale a dire che i 2 MOS entrano entrambi in conduzione.

VIN

( )

( )

Ω≈−

≈

=−−≈

133VV 5.3

1WLR

mA 375.0VV 1.5kL2

WI

TNmk1

N

2TPmD

V 1VV

VA 30k 100LW V 5V

TPTN

2mCC

≈≈

µ===

( )Ω>

Ω≈−

≈

M R

83VV

1WLR

P

TNDDmk1

N

Parametri:

Se VIN=VDD:

Se VIN=3.5 V:

VOUT diviene circa 50 mV, ma la potenza dissipata dalla porta è di ben 1.9 mW!

ESEMPIO:

RP

RN

(RN ed RP sono le resistenze dinamiche di uscita, pensate connesse tra Drain e Source del MOS N e del MOS P, rispettivamente)

47Le Logiche e le interfaccegpessina

La logica CMOS 12

La potenza statica dissipata da un circuito CMOS è nulla. Solo durante le transizioni si ha assorbimento di corrente che determina dissipazione.

Una quantità di energia simile la spenderemo per riportare il condensatore al valore originale di 0 V.Se questa operazione vene effettuata ad una frequenza media f in un tempo t questa energia verrà spesa tf volte:

Quindi la potenza dissipata sarà:

Siccome nel nostro circuito vi saranno molte porte logiche e considerando come frequenza la frequenza del clock, il costruttore fornisce una sorta di capacità equivalente, riassuntiva:

VCC

Vi

Vo

MP

MN

Da questo punto di vista abbiamo visto che la nostra porta logica all’ingresso è un condensatore.Se commutiamo l’ingresso da 0 V alla tensione VCC spenderemo un’energia uguale a quella che troveremo ai capi del condensatore:

C

U =12

CVCC2

Ut = Uft

P =dUt

dt= Uf = CVCC

2 f

P = CDISVCC2 fclock

La conclusione importante è che la potenza dissipata dipende in modo quadratico dalla tensione di alimentazione ed è lineare, ed aumenta, con la frequenza.

48Le Logiche e le interfaccegpessina

La logica CMOS 13

Nei circuiti logici esistono 3 diverse tipologie di uscita da una porta. La prima l’abbiamo già vista: lo stadio di uscita è attivo sia nello stato alto che nello stato basso (active high e active low) ovverosia che la linea a cui l’uscita è connessa è sempre pilotata dalla bassa impedenza del MOS N o del MOS P.

La seconda tipologia di uscita è la così detta tri-state output: all’uscita la porta ha una modalità di funzionamento addizionale detta in high-state, Hi-Z. Questa modalità à abilitata o meno da un ingresso addizionale:

Quando EN è basso l’uscita del NAND si mantiene alta mentre l’uscita NOR si mantiene bassa per qualsiasi valore di A. Questa condizione mantiene contemporaneamente interdetti Q1 e Q2. La linea a cui l’uscita OUT è connessa si trova in alta impedenza rispetto a questa porta.

Ora un’altra porta potrebbe occupare la linea trasmettendo il proprio segnale senza che questa porta possa intralciare, ovvero possa tentare di forzare la linea in uno stato diverso da quello del dispositivo ‘master’ in quel momento.

Questa soluzione si adotta quando su un bus (insieme omogeneo di più linee) più dispositivi devono trasmettere i propri dati. La tipica situazione è il bus dati ed il bus istruzioni all’interno di un µ-controllore: solo un registro selezionato per volta può trasmettere sul bus, mentre più dispositivi potrebbero leggere il bus contemporaneamente.

49Le Logiche e le interfaccegpessina

La logica CMOS 14L’ultima modalità di funzionamento è l’open drain. La porta di uscita in questa situazione manca del MOS P, ovvero del dispositivo active high.

Nella porta open drain manca il MOS P. La connessione verso l’alimentazione positiva va stabilita con un resistore, pull-up resistor.

La connessione verso l’alimentazione positiva va stabilita con un resistore.Il valore del resistore non deve essere molto piccolo altrimenti l’assorbimento di corrente nello stato basso diviene elevato. Allo stesso tempo il resistore non deve essere troppo grande altrimenti la transizione dallo stato basso allo stato alto diverrebbe estremamente lenta.

Per esempio supponiamo che la porta sia caricata con 100 pF. Nello stato basso la RON del MOS N potrebbe essere 100 Ω, da cui si evince un fall time di circa 22 nsec. Con una impedenza di Drain di 1500 Ω il rise time diventa di ben 330 nsec.

50Le Logiche e le interfaccegpessina

La logica CMOS 15L’uscita di open drain è sfruttata nelle trasmissioni in cui le linee necessitano di essere pilotate da più master. Esistono diversi protocolli di comunicazione che sfruttano questa opportunità. Una proprietà importante del protocollo open drain è che le uscite non possono mai creare un conflitto di tipo elettrico, al più possono crearsi degli errori di trasmissione.

Solo una porta deve comunicare per volta. Le altre per lasciare libera la linea devono semplicemente porre la propria uscita alta.

Pur non facendo niente di speciale se non un AND cablato, questo tipo di uscita è sfruttato da diversi protocolli molto usati tipo I2C.

51Le Logiche e le interfaccegpessina

Sommario delle configurazioni

Configurazione PUSH-PULL:

MP

VCC

MNVi→0

MP

VCC

MNVi →1

Attenzione: non connettere mai 2 uscite tra di loro: si bruciano!

La porta è possibile impostarla in alta impedenza, così da non avere conflitti. Nell’esempio a fianco se EN=0 sia il MOSP che il MOSN sono OFF.

Infine, la porta può essere configurata in “open drain” o “open collector”. In questo caso occorre aggiungere un resistore tra l’uscita e l’alimentazione.

Più pin “open drain” connessi assieme formano una porta NAND.

Più pin configurati in “open drain” connessi tra di loro non vanno in conflitto elettrico.

Configurazione HIGH-IMPEDANCE:

Configurazione OPEN-DRAIN (OPEN-COLLECTOR):

52Le Logiche e le interfaccegpessina

Appendice A: I diodi nei circuiti raddrizzatori 1

Raddrizzatore a mezz’onda

VD= potenziale di built-in

VD

VSR

D VO

Se VS<0 il diodo non si lascia praticamente attraversare da corrente, per cui l’uscita rimane pressoché nulla.

Se 0<VS<VD la corrente che può scorrere nel diodo è molto bassa, per cui la ddp ai capi di R è trascurabile. Di conseguenza VO rimane piccola.

Se VS>VD la corrente nel diodo può fluire quasi liberamente. La ddp ai capi del diodo varia logaritmicamente con la corrente. Di conseguenza possiamo pensare la ddp ai capi del diodo quasi costante. Quindi VO≈ VS-VD.

Il risultato è che solo l’onda positiva viene trasmessa all’uscita. Il valore medio della tensione di uscita è diverso da zero: abbiamo una componente continua.

53Le Logiche e le interfaccegpessina

Appendice A: I diodi nei circuiti raddrizzatori 2

VD

VSR

D1 VO

D2-VS

Raddrizzatore ad onda intera

Inserendo un generatore con segnale di polarità opposta ed un diodo D2 con verso opposto a D1 si possono ottenere le 2 onde raddrizzate: l’energia disponibile all’uscita viene raddoppiata.

Ponte di diodi

VD

VSR

D1 VO

D2-VS

Inserendo il condensatore C in parallelo al carico R si può rettificare l’onda, purché sia verificato che la costante di tempo RC sia >> della frequenza della sinusoide.

C

R

Se l’onda è positiva la corrente scorre in questo verso.

Se l’onda è negativa la corrente scorre in questo verso.

Nel carico la corrente scorre sempre nello stesso verso: abbiamo realizzato un raddrizzatore con un solo generatore. In uscita però in questo caso si perde 2 volte la tensione presente ai capi dei diodi.

54Le Logiche e le interfaccegpessina

Appendice B: protezione da sovra tensione nei circuiti integrati

Circuito integrato

VEE

VCC

RD1

D2

VS

Se per malfunzionamento la tensione di ingresso VS sale sopra il valore della tensione di alimentazione positiva VCC il diodo D1 inizia a condurre, limitando l’escursione del pin a VCC+VD.

pin

Se VS scende sotto il valore della tensione VEE (che potrebbe essere anche massa) D2 conduce, limitando l’escursione del pin a VEE-VD.

La coppia di diodi viene inserita ad ogni pin di ingresso del circuito integrato. La coppia di diodi è residente all’interno del circuito integrato. A seconda delle applicazioni è anche prevista la presenza della resistenza. Altrimenti si deve prevedere la sua presenza esterna, se si pensa che possa esistere il pericolo di sovratensione.