Cella di memoria SRAM a 6T - unina.stidue.netunina.stidue.net/Circuiti Integrati...

-

Upload

hoangnguyet -

Category

Documents

-

view

259 -

download

0

Transcript of Cella di memoria SRAM a 6T - unina.stidue.netunina.stidue.net/Circuiti Integrati...

- memorie volatili

- scrittura del dato tramite oreazione positiva carica su di una capacità

- configurazioni tipo a e3 MOS/cella (3T) 1 MOS/cella (1T)6 MOS/cella (6T),

- configurazioni con o con2 uscite complementari uscita singola

- in base al meccanismo di scrittura RAM o� statiche (SRAM) dinamiche (DRAM)

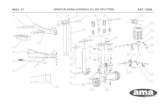

Cella di memoria SRAM a 6T

- struttura del flip-flop SR con i pass-transistors M e M5 6

- dimensionamento dei MOS per corrette operazioni di WRITE e READ

VDD

WL

BL BL

M1 M3

M4M2

M5

M6

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

Operazione di scrittura (WRITE)

supponiamo di volere che Q = 1 0�

- Dimensionamento di M e M (V =V /2, V =V ):4 6 M DD Tn Tp

- Dimensionamento di M e M (V =V /2, V =V ):1 5 M DD Tn Tp

V

V

DD

DD

Q=1Q=0

WL

BL=1 BL=0

M1

M4

M5

M6

� �k V VV

2

V

8k V V

V

2

V

8n M 6 DD T n

DD DD2

p M 4DD T p

DD DD2

� ��

��

�

� ��

���� �

�

��

�

�

Q =1 0 V <V

2k k

W

L0.4

W

LQDD

n M6 p M4n M6 p M4

� � � ����

��

���

��

� �kV

2V per V

V

2k V V

V

2

V

8n M5

DDTn SB

DDn M1 DD Tn

DD DD2

� ���

��

���

��

�

��

�

� � �

�

��

�

�

2

Q=0 1 V >V

2k 10k

W

L1

W

LQ

DDnM5 nM1

nM5 nM1

� � � ����

��

���

��

0

: per effetto del flip-flop, anche con (W/L) =(W/L) , si ha che Q =0 1M1 M5�

se

se

per V

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

Operazione di lettura (READ)

supponiamo che Q = 1

- Dimensionamento di M e M (V =V /2, V =V ):1 5 M DD Tn Tp

� �kV

2V per V

V

2k V V

V

2

V

8n M5

DDTn SB

DDn M1 DD Tn

DD DD2

� ����

�

���

�

�

��

�

� � �

�

��

�

2

condizione opposta a quanto richiesto (ma non necessario) per WRITE

V

V

DD

DD

VDD

Cbit

Q=1Q=0

WL

BL BL

M1

M4

M5

M6

V

precaricata precaricata

DD

Cbit

- Capacità delle linee di bit C dell' ordine dei pF V lentamente variabilebit DM5�

- Combinazione M -M come NMOS con carico ad arricchimento in saturazione1 5

- Valore di V deve restare <V /2 per evitare la distruzione del dato conservatoQ DD

per V

affinché Q 0 VV

2k 10k

W

L10

W

LQ

DDn M 5 n M

n M 5 n M1

� � � � ����

�

���

�1

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

Confronto tra i diversi pull-up

cella a 6T occupa troppa area

resistenze R di pull-up al posto dei PMOS area ridotta del 30%L �

- Resistenza R alta per evitare consumo di potenza statico polisilicioL �

- Se R alta t molto elevato e precaricate a VL pLH DD� � BL BL

- Se R troppo alta pull-up non compensa leakage pull-up in TFTL � �

Cella di memoria SRAM con carico resistivo

VDD

WL

BL BL

M1 M2

RLRL

M3M4

N° di transistors 6 4 4 (+2 TFT)

Dimensione cella

Corrente di standby (cella) 10 A-15

PMOS Resistenza TFT

58.2 m� 2 40.8 m� 2 41.1 m� 2

10 A-12

10 A-13

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

Cella di memoria DRAM a 3T

- la carica persa per leakage è rifornita con refresh anziché con pull-up (SRAM)

- rispetto SRAM, la cella è semplificata eliminando la ridondanza delle uscite

- contrariamente che in SRAM, non vi è nessun vincolo sulle dimensioni dei MOS

- l' operazione di lettura è non-distruttiva

- il valore di tensione in X corrispondente ad "1" è pari a V -V bootstrapWWL T�

X

WWL

RWL

BL1

CS

M2M1

M3

BL2

WWL

RWL

X

BL1

BL2

V -VDD T

V -VDD T�V

VDD

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

Cella di memoria DRAM a 1T

- per scrivere, la capacità C è caricata o scaricata abilitando eS WL BL

- per leggere, la carica si ridistribuisce tra la capacità C e la capacità CS BL

(V =tensione iniziale su C )S S

- il valore dello swing V è piccolo, tipicamente intorno ai 250 mV�

- siccome V è molto piccolo, occorre un sense amplifier per accelerare la lettura�

- è richiesta la capacità aggiuntiva C , da considerare anche nel progettoS

- l'operazione di lettura è distruttiva necessità di rigenerare il dato�

- il valore di tensione in X corrispondente ad "1" è pari a V -V bootstrapWL T�

X

WLBL

CS

M1

CBL

V -VDD T

VDD

VDD /2 VDD /2

WL

X

BL

GND

Scrive "1" Legge "1"

sensing

� ��V V V V VC

C CBL PRE S PRES

S BL

� � � ��

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

- parti del sistema dedicate all'indirizzamento in una cella di memoria

- insiemi di N=2 porte logiche, con N=n° di words e L=n° bit di ingressoL

- progetto strettamente connesso a quello delle celle di memoria (pitch matching)

n° porte

Usando pseudo-NMOS o porte dinamiche n° di transistors = (L+1)*2�L

In logica a rapporto o porte dinamiche n° di transistors = 11x1024=11.264�

: decodificatore di indirizzo a 10 bit (L=10)

(decodifica a porte NOR)

Decodificatore di riga

WL A A A A A A A A A A0 0 1 2 3 4 5 6 7 8 9�

WL A +A +A +A +A +A +A +A +A +A0 0 1 2 3 4 5 6 7 8 9�

WL A +A +A +A +A +A +A +A +A +A255 0 1 2 3 4 5 6 7 8 9�

WL A A A A A A A A A A255 0 1 2 3 4 5 6 7 8 9�

n° MOSper porta

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

Decodificatore dinamico a NOR da 2 a 4

Decodificatore dinamico a NAND da 2 a 4

progetto NAND minor area e consumo di potenza rispetto NOR

WL3

GND GNDpull-up

precaricati

WL2

WL1

WL0

VDD

�A0 A0 A1 A1

WL3

pull-upprecaricati

WL2

WL1

WL0

VDD

VDD

VDD

VDD

A0 A0 A1 A1

�

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

Decodifica a NAND mediante uso di predecoder

decodificatore di indirizzo a 10 bit (L=10)

(decodifica con NAND a 10 ingressi)

(decodifica con NAND a 5 ingressi,predecodifica con NOR a 2 ingressi)

WL A A A A A A A A A A0 0 1 2 3 4 5 6 7 8 9�

� �� �� �� �� �� �A +A A +A A +A A +A A A0 1 2 3 4 5 6 7 8 9

- riduzione n° MOS se predecoder FCMOS ne servono (1024x6)+(5x4x4)=6.224�

- poiché fan-in si dimezza (10 5) t si riduce di circa un fattore 4� � p

- carico su linee di indirizzo verticali si dimezza (2 2 ) ulteriore riduzione di t9 8� � p

linee di indirizzo verticali

A0A

1A

0A

1A

0A

1A

0A

1A

2A

3A

2A

3A

2A

3A

2A

3

A1

A0

A0

A1

A3

A2

A2

A3

WL0

WL1

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

ottima velocità, solamente 1 MOS aggiuntivo lungo il segnale dati

bassa velocità, poiché K MOS in serie

eccessivo n° di MOS, pari a (K+1)2 +2 se K=10, n° MOS pari a 12.288K K

�

ridotto n° di MOS, pari a 2 (2 -1) se K=10, n° MOS pari a 2.046K

�

Decodificatori di colonna e di blocco

Se K=n° bit di indirizzo di colonna multiplexer a 2 ingressi�K

Decodificatore di colonna a pass-transistors

Decodificatore di colonna ad albero

BL0 BL1 BL2 BL3

D

A0

A1

S0

S1

S2

S3

DE

CO

DIF

ICA

TO

RE

NO

RA

2IN

GR

ESSI

BL0 BL1 BL2 BL3

D

A0

A0

A1

A1

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

tenere basso il valore di t per velocizzare le operazioni della memoriap

utilizzare un amplificatore di sense

- in DRAM a 1T, necessario per amplificare la bassa V ( 250 mV)� �

- compensa le limitate capacità di pilotaggio in uscita della cella di memoria

- in altre memorie, consente di ridurre V su bit lines riduzione di t e P� � p D

- riducendo V su bit lines minore consumo per caricare e scaricare bit lines� �

- necessario per ripristinare sulle bit lines lo swing logico completo

t CV

Ip �

�

grandepiccolo

bisogna renderloil più piccolo possibile

piccola ampiezza

ingresso uscita

AMPLIFIC.DI SENSE

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

Schema per amplificazione in SRAM

- annulla gli effetti di diversi valori di tensione corrispondenti a "0" e "1"

- amplifica le differenze tra le due bit lines eBL BL

- applicabile direttamente solo a SRAM

- utilizzabile per più celle tramite decodificatore riduzione di area e potenza�

- sopprime il rumore dovuto alla V e ad accoppiamenti capacitivi tra eDD WL BL

Amplificazione differenziale

q- passa al valore basso entrambe le bit lines vanno a VPC � DD

- e passano al valore alto lettura del dato con o bassoPC WL BL BL�

- quando V 0.5V amplificatore di sense si attiva� � �

AMPLIF.SENSEDIFF.

BLBL

cella SRAM

x x

y y

D D

VDD

VDD

WL

PC

EQ

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

Valore tipico di A 10sense �

- struttura tipo DCVSL

- molto veloce (reazione positiva)

- sensibile a malfuzionamenti (alto guadagno dinamico)

Amplificatore di sense a specchio di corrente

Amplificatore di sense ad accoppiamento incrociato

VDD

x x

y

SE

M1 M2

M4M3

M5

VDD

xx

y

SEM5

M1 M2

M4M3

y

VDD

xx

y

SE M5

M1 M2

M4M3

� �A g r / /rsense m1 o1 o3� � � �A g r / /rsense m2 o2 o4� �

Amplificatore di sense basato su latch

VDD

BL

SE

SE

BLEQ

- inizializzato nel punto metastabile mediante EQ

- dopo la lettura di V=|V -V |, si abilital'amplificatore di sense mediante SE

� BL BL

- la reazione positiva conduce rapidamente l'uscitadel circuito verso un punto di equilibrio stabile

- configurazione idonea per rigenerazione in DRAM a 1T(necessaria interfaccia da single-ended a differenziale)

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria

- schema per cella DRAM a 1T

- matrice di celle divisa in due parti uguali riduzione di C� BL

- celle "fittizie" precaricate a V /2 tramite e ,DD EQ L R

- per lettura di L , L , ecc. (R , R , ecc.) abilitazione della sola cella fittizia L (R)0 1 0 1 �

- per celle (E)EPROM cella "fittizia" FLOTOX (FAMOS) con W/L dimezzato�

Conversione da single-ended a differenziale

Architettura "open bit-line" con cella "fittizia"

CELLA DIMEMORIA

AMPLIFICATOREDI SENSE

DIFFERENZIALE

BL

VREF+_

WL

x x

y yCome scegliere V ?REF

V deve sapersi adattare alle possibilivariazioni di tensione da cella a cellaREF

VDD

SE

SE

CS CS CS

L

...

CSCS

...CS

R

BLL BLR

L0

L1 R

0R

1

cella "fittizia"

EQ

cella "fittizia"amplificatore a latch

Giovanni Vito Persiano

Università degli Studi del Sannio

Corso di Circuiti e Sistemi VLSI

Facoltà di Ingegneria