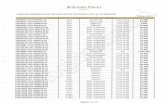

Descrizioni ortografiche : studio delle suerfici architettoiche nel metoto di Monge 1.

METODOLOGIA PER LA REALIZZAZIONE DI IP CORE BASATI SU DESCRIZIONI IN LINGUAGGIO C

description

Transcript of METODOLOGIA PER LA REALIZZAZIONE DI IP CORE BASATI SU DESCRIZIONI IN LINGUAGGIO C

Politecnico di MilanoPolitecnico di Milano

METODOLOGIA PER LA METODOLOGIA PER LA REALIZZAZIONE DI IP CORE REALIZZAZIONE DI IP CORE BASATI SU DESCRIZIONI IN BASATI SU DESCRIZIONI IN

LINGUAGGIO CLINGUAGGIO CRelatore: Prof. Fabrizio FERRANDI

Correlatore: Ing. Marco Domenico SANTAMBROGIO

Massimo Ratti MATRICOLA 653597

Fabio Rizzato MATRICOLA 653694

Ratti Massimo – Fabio Rizzato2

SommarioSommario

1. FPGA, FSM, FSMD, diagrammi ASM, EDK;1. FPGA, FSM, FSMD, diagrammi ASM, EDK;

2. Metodologia proposta;2. Metodologia proposta;

2a. Realizzazione del diagramma 2a. Realizzazione del diagramma ASM;ASM;

2b. Realizzazione del diagramma a 2b. Realizzazione del diagramma a blocchi;blocchi;

2c. Traduzione in VHDL;2c. Traduzione in VHDL;

2d. Interfacciamento sul bus OPB;2d. Interfacciamento sul bus OPB;

2e. Inserimento nell’architettura;2e. Inserimento nell’architettura;

2f. Definizione del device driver;2f. Definizione del device driver;

3. Risultati, conclusioni e sviluppi.3. Risultati, conclusioni e sviluppi.

Ratti Massimo – Fabio Rizzato3

Virtex II Pro Evaluation Board

Introduzione: FPGAIntroduzione: FPGA

Ratti Massimo – Fabio Rizzato4

Introduzione: FSMIntroduzione: FSM

MOORE

MEALY

(S, I, O, s0)

Ratti Massimo – Fabio Rizzato5

Introduzione: FSMDIntroduzione: FSMD

Ratti Massimo – Fabio Rizzato6

Introduzione: diagrammi ASMIntroduzione: diagrammi ASM

STATE BOX

DECISION BOX

CONDITION BOX

Ratti Massimo – Fabio Rizzato7

Introduzione: EDK e XPSIntroduzione: EDK e XPS

Ratti Massimo – Fabio Rizzato8

Metodologia propostaMetodologia proposta

REALIZZAZIONE DEL DIAGRAMMA ASM

REALIZZAZIONE DEL DIAGRAMMA

A BLOCCHI

DESCRIZIONE IN LINGUAGGIO C

TRADUZIONE DEL DIAGRAMMA A BLOCCHI

IN VHDL

CORE DEL COMPONENTE INTERFACCIAMENTO SU BUS

IP CORE

INSERIMENTO NELL’ARCHITETTURA

DEFINIZIONE DEL DEVICE DRIVER

IMPLEMENTAZIONE COMPONENTE SU FPGA

COMPILAZIONE E SINTESI

Ratti Massimo – Fabio Rizzato9

Realizzazione del diagramma ASMRealizzazione del diagramma ASM

for(int i=0;i<N;i++) for(int j=N-2;j>=i;j--) if(valore[j]>valore[j+1]) scambio=valore[j] valore[j]=valore[j+1] valore[j+1]=scambio end if end forend for

Ratti Massimo – Fabio Rizzato10

Realizzazione del diagramma a blocchiRealizzazione del diagramma a blocchi

Ratti Massimo – Fabio Rizzato11

Realizzazione del diagramma a blocchiRealizzazione del diagramma a blocchi

MACCHINA DI MEALY MACCHINA DI MOORE

Ratti Massimo – Fabio Rizzato12

Traduzione State box in VHDLTraduzione State box in VHDLSI DEFINISCE IL DATAPATH

0

1

2

3

8

7

4

5

6

PROCESSO DATAPATH CASE stato_presente IS WHEN 0 =>

operazioni stato 0 WHEN 1 => operazioni stato 1 … WHEN OTHERS => fine END PROCESSO

Ratti Massimo – Fabio Rizzato13

Traduzione Decision box in VHDLTraduzione Decision box in VHDLSI DEFINISCE IL CONTROLLORE

0

1

2

3

8

7

4

5

6

PROCESSO 2 CONTROLLORE CASE stato_presente IS WHEN 0 =>

definizione stato prossimo WHEN 1 => definizione stato prossimo … WHEN OTHERS => fine END PROCESSO

PROCESSO 1 CONTROLLORE if reset=1 then stato_corrente <= stato_reset elseif start=1 then stato_corrente <= stato prossimo end if END PROCESSO DATAPATH

Ratti Massimo – Fabio Rizzato14

Interfacciamento al busInterfacciamento al bus

REALIZZAZIONE DEL DIAGRAMMA ASM

REALIZZAZIONE DEL DIAGRAMMA

A BLOCCHI

TRADUZIONE DEL DIAGRAMMA

A BLOCCHI IN VHDL

DEFINIZIONE PSELECT

INTERFACCIAMENTOPSELECT CON OPB E

CON IP CORE

Ratti Massimo – Fabio Rizzato15

Inserimento nell’architetturaInserimento nell’architettura

PROCESSORE PPC

IP CORE

BUS OPB BUS PLB

Ratti Massimo – Fabio Rizzato16

Definizione del device driver (1)Definizione del device driver (1)

IP CORE

CORE

PSELECT

FILE SORGENTE

WRITE

2

1

3

REGISTRI OPB ASSOCIATI ALL’IP CORE

Ratti Massimo – Fabio Rizzato17

Definizione del device driver (2)Definizione del device driver (2)

IP CORE

CORE

PSELECT

FILE SORGENTE

READ

1

2

REGISTRI OPB ASSOCIATI ALL’IP CORE

Ratti Massimo – Fabio Rizzato18

Simulazione comportamentaleSimulazione comportamentale

INIZIO SIMULAZIONE FINE SIMULAZIONE

Ratti Massimo – Fabio Rizzato19

Conclusioni e sviluppi futuriConclusioni e sviluppi futuri

AUTOMAZIONE DELLA METODOLOGIA PROPOSTA ATTRAVERSO SOFTWARE

IMPLEMENTAZIONE DELL’ALGORITMO DI ORDINAMENTO CON UNA

MACCHINA DI MEALY

POSSIBILI SVILUPPI

LA METODOLOGIA CONSENTE DI DEFINIRE

UN IP CORE LOGICAMENTE CORRETTO

Ratti Massimo – Fabio Rizzato20

Fine presentazioneFine presentazione