PROGETTO DI UN REGISTRO AD APPROSSIMAZIONI SUCCESSIVE IN UN ASIC PER IMAGING FACOLTA DI INGEGNERIA...

-

Upload

celestina-falcone -

Category

Documents

-

view

231 -

download

3

Transcript of PROGETTO DI UN REGISTRO AD APPROSSIMAZIONI SUCCESSIVE IN UN ASIC PER IMAGING FACOLTA DI INGEGNERIA...

PROGETTO DI UN REGISTRO AD

APPROSSIMAZIONI SUCCESSIVE IN

UN ASIC PER IMAGING

FACOLTA’ DI INGEGNERIA

Laurea in Ingegneria Elettronica

Candidato: Alessandro Fina

Relatore: Prof. Lorenzo Colace

Co-relatore: Dott. Valentino Cencelli

• Introduzione alla medicina nucleare

• Cosa è un SAR

• Architettura

• CAD Elettronico

• Progettazione

• Dimensionamento

• Simulazione

• Layout

• Conclusioni

• Introduzione alla medicina nucleare

• Cosa è un SAR

• Architettura

• CAD Elettronico

• Progettazione

• Dimensionamento

• Simulazione

• Layout

• Conclusioni

Sommario

Introduzione alla medicina nucleareIntroduzione alla medicina nucleare

Fotomoltiplicatore

e-

Matrice di cristalli scintillanti

350nmFotone 140keV

Imaging molecolare: rilevazione spaziale e temporale di radiazioni gamma.

Rivelatore Hamamatsu H8500:

- matrice 8×8 di anodi→12 stadi si amplificazione

- Risposta spettrale: 300nm → 650nm

- area attiva 89% del dispositivo

Floor planning (struttura topologica) del chip completo

- Area disponibile di silicio è di 3mm×5mm

Introduzione alla medicina nucleareIntroduzione alla medicina nucleare

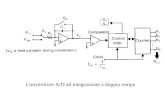

Il convertitore A/D è composto da:

- Comparatore

- Convertitore D/A interno (DAC)

- Registro ad approssimazioni successive (SAR)

Cosa è un SARCosa è un SAR

Cosa è un SARCosa è un SAR

Un SAR rappresenta un registro SIPO (serial input - parallel output) che viene utilizzato per la tecnica di approssimazioni successive:- Conversione di n bit in n cicli di clock implementando l’algoritmo di ricerca dicotomica

C. K. Yuen

SPECIFICHE DI PROGETTO:

- n = 10 bit

- fCLK = 500MHz

- Layout compatto

ArchitetturaArchitettura

- n+1 flip-flop di tipo JK- Due porte OR

• Schemi elettrici

• Simboli

• Simulazioni

• Layout

Cadence è da molti anni lo standard industriale più importante e riconosciuto in tutto il mondo.

CAD ElettronicoCAD Elettronico

tp∝ L²/VDD tempo di propagazione

DIMENSIONI SCELTE:• L=0.24μm - W=0.7μm NMOS• L=0.24μm - W=1.2μm PMOS

L = lunghezza del canale

W = larghezza del canale

iD = corrente di canale

tp = tempo di propagazione

DimensionamentoDimensionamento

NOT

ProgettazioneProgettazione Implementazione delle porte fondamentali

NOR

TRASMISSION GATE

NAND

OR

Implementazione del Flip-Flop di tipo JK

nCLR

CLK

K

Q

Qneg

J

TG

TG

TG

TG

I singoli Flip-Flop vengono connessi secondo il modello Yuen

ProgettazioneProgettazione

Verificare il corretto funzionamento del circuito

NANDING. USC.

A B C

0 0 1

0 1 1

1 0 1

1 1 0

ING. USC.

A B C

0 0 0

0 1 1

1 0 1

1 1 1

SimulazioniSimulazioni

OR

A

B

C

A

B

C

Time [ns]

Time [ns]

ING. USC.

nCLR Jn Kn Qn+1

0 X X 0

1 0 0 Qn

1 0 1 0

1 1 0 1

1 1 1 Toggle

- X: l’ingresso può essere indifferentemente 0 o 1, non influisce sull’uscita- Toggle: se Qn=0 allora Qn+1=1; se Qn=1 allora Qn+1=0

Flip-Flop JK a 500MHzSimulazioniSimulazioni

Time [ns]

CLK

nCLR

J

K

Q

Qneg

SAR a 500MHz

• Vengono analizzati sequenzialmente tutti i bit da MSB fino al LSB• Se DATA = “1” il bit analizzato viene riportato a “0” • Se DATA = “0” il bit analizzato viene lasciato ad “1”

Time [ns]

CLK

nCLR

DATA

MSB

Q8

Q3

Q1

Q6

Q5

Q4

Q2

Q7

LSB

EOC

SAR

DAC

CONVERTITORE I/V

COMPARATORE

Possiamo osservare come la tensione Vth, dopo le varie comparazioni, si avvicina sempre più alla tensione Vinput. Questo dimostra il corretto funzionamento di tutto il blocco e quindi anche del SAR

Convertitore Analogico/DigitaleSimulazioniSimulazioni

Rappresenta la distribuzione e connessione dei transistor sul wafer di silicio

Nella realizzazione di un layout bisogna:

• Ottimizzare le dimensioni

• Rispettare le regole di progettazione imposte dalla fonderia

Per la verifica del layout:

• DRC: verifica delle regole di progettazione

• LVS: confronto tra schema elettrico e layout

LayoutLayout

Flip-Flop JK

SAR 10bit

NAND

OR TRASMISSION GATE

NOT

Collegando opportunamente i transistor, secondo le indicazioni dello schema elettrico, è stato possibile realizzare

LayoutLayout

LayoutLayout

SAR 10bit

• Apprendimento del software di progettazione Cadence

• Progetto e simulazione di un registro ad approssimazioni successive a 10 bit alla frequenza di 500MHz

• Realizzazione e verifica del layout del registro di dimensioni 285μm×30.4μm • Il circuito verrà realizzato dall’INFN in fonderia nei prossimi mesi

ConclusioniConclusioni