Calcolatori Elettronici Esercitazione n 1staff.icar.cnr.it/spezzano/sor/lucidiese/esercita... ·...

Transcript of Calcolatori Elettronici Esercitazione n 1staff.icar.cnr.it/spezzano/sor/lucidiese/esercita... ·...

Corso di studi in Ingegneria Elettronica A.A. 2003/2004

Calcolatori ElettroniciEsercitazione n 1

Ing Giovanni Costa

2

Sommario:

Evoluzione dell’industria dei calcolatoriBreve storia dei calcolatoriLegge di Moore, Legge di NathanGamma di calcolatori disponibiliTipologie di computer

Esempi di famiglie di calcolatoriLa famiglia Intel: Il Pentium IILa famiglia Sparc: l’Ultra Sparc IILa famiglia picoJava: Il picoJava II

3

Generazione 0 (1600-1945)

Pascal (1623-1662)addizioni e sottrazioni

Leibniz (1646-1716)anche moltiplicazioni e divisioni

Charles Babbage (1792-1871)A) Macchina Differenziale

Algoritmo fisso (differenze finite)Output su piastra di rame

B) Macchina AnaliticaPrima macchina programmabilePrimo programmatore: Ada Lovelace (figlia di Lord Byron)Memoria: 1000 x 50 cifre decimaliMulino (CPU)I/O su schede perforateLimite: tecnologia meccanica

4

Generazione 0 (continua)Macchine elettromeccaniche

Konrad Zuse (~1930 Germania)Macchina a relèDistrutte nella guerra

John Atanasoff (~1940 USA)Aritmetica binariaMemoria a condensatori

Howard Aiken (~1940 USA)MARK 1: versione a relè della macchina di BabbageMemoria: 72 x 23 cifre decimalitempo di ciclo: 6 sec.I/O su nastro perforato

5

I Generazione (1945-1955)Tecnologia a tubi termoionici

COLOSSUS (~1940 GB)Gruppo di Alan TuringDecifrazione del codice EnigmaProgetto mantenuto segreto

ENIAC (~1946 USA)J. Mauchley, J. Eckert18.000 valvole30 tonnellate di peso140KW assorbimentoProgrammabile tramite 6000 interruttori e pannelli cablati20 registri da 10 cifre

EDVAC (~1950 USA)Successore dell’ENIACMai giunto a termine

6

La Macchina di Von Neumann

IAS (~ 1950, Princeton USA)Programma memorizzatoAritmetica binariaMemoria: 4096 x 40 bitFormato istruzioni a 20 bit:

OPCODE INDIRIZZO8 12

7

II Generazione (1955-1965)Tecnologia a transistor

TXO e TX2 macchine sperimentali costruite al MITUno dei progettisti del TX2 fonda una propria società:Digital Equipment Corporation (DEC)La DEC produce il PDP-1 (1961):

Memoria: 4K parole di 18 bitTempo di ciclo di 5 µsecPrestazioni simili all’IBM 7090Prezzo meno di un decimoSchermo grafico 512 ⋅ 512 pixel (primi videogiochi)Comincia la produzione di massa

8

Il Minicomputer

DEC PDP-8 (1965)Successore diretto del PDP-1Interconnessione a bus, molto flessibileArchitettura incentrata sull’I/OPossibilità di connettere qualsiasi perifericaProdotto in oltre 50.000 esemplari

9

III Generazione (1965-1980)

Tecnologia LSI e VLSI

Evoluzione dell’architettura HWMicroprogrammazioneUnità veloci floating-pointProcessori ausiliari dedicati alla gestione dell’I/O

Evoluzione dei Sistemi OperativiVirtualizzazione delle risorseMultiprogrammazione: esecuzione concorrente di più programmiMemoria Virtuale: rimuove le limitazioni dovute alle dimensioni della memoria fisica

10

IV Generazione: il PC

Diretto discendente del minicomputer:Architettura a busParole e istruzioni a 16 bit

Nasce nel 1980 all’ IBM (che dà così avvio alla propriadecadenza)Esplosione del mercato dei “cloni”Crollo dei costi ed enorme espansione dell’utenzaDai grandi Centri di Elaborazione ad un contesto diInformatica DistribuitaL’espansione del PC è trainata da tre fattori:

Aumento della capacità della CPUDiscesa dei costi della memoriaDiscesa dei costi dei dischi

11

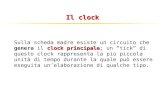

Evoluzione dell’industria dei calcolatoriLa legge di Moore

Il numero di transistor su di un chip raddoppia ogni 18 mesi:

Aumento di circa 60% all’annoConseguenze:

Aumento della capacità dei chip di memoriaAumento della capacità delle CPU

12

Evoluzione dell’industria dei calcolatori

La legge di Moore per le CPU

13

Evoluzione dell’industria dei calcolatori

La legge di Moore per le CPU

Più transistor in una CPU significano:Eseguire direttamente istruzioni più complesseMaggiore memoria sul chip (cache)Maggiore parallelismo interno

N.B. Altro fattore tecnologico decisivo è la frequenza di funzionamento → “velocità di commutazione del singolo transistor”

14

Evoluzione dell’industria dei calcolatoriLa legge di Nathan

Il software è come un gas che si espande per riempire il contenitore che lo contiene

Al calare dei costi ed all’aumentare della memoriadisponibile, le dimensioni del software sono semprecresciute in proporzioneIl Circolo Virtuoso

Spinta tecnologica (Moore law)Costi più bassi e prodotti miglioriNuove applicazioni e mercatiNuove compagnie e maggiore competizioneSpinta tecnologica ......

15

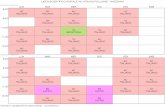

Evoluzione dell’industria dei calcolatori

Tipologie di calcolatori

16

Evoluzione dell’industria dei calcolatori

Tipologie di calcolatori

Personal ComputerLo conosciamo bene

ServerSu rete locale o Web serverMemorie fino a qualche GbyteCentinaia di Gbyte di discoGestione di rete efficiente

COW (Cluster of workstations)Sistema multiprocessore ad accoppiamento lascoHardware di tipo standard: costi contenutiStrutture di connessione velociElevata capacità di elaborazione complessiva

17

Evoluzione dell’industria dei calcolatori

Tipologie di calcolatoriMainframe

Diretti discendenti della serie IBM 360Gestione efficiente dell’I/OPeriferie a dischi di molti TbyteCentinaia di terminali connessiCosti di parecchi milioni

Perché sopravvivono ?Gestiscono applicazioni legacyCosti di migrazione delle applicazioni molto superiori a quelli dell’Hardware

18

Esempi di famiglie di calcolatori

La famiglia INTEL

19

Esempi di famiglie di calcolatori

INTEL Pentium IIIDisponibilità: febbraio 1999450Mhz – 1Ghz di frequenza di clockPipeline a 10 stadiCirca 9 milioni di transistor in un chip4 GB di memoria indirizzabileBus di sistema a 100 e 133 MHzNuove istruzioni SIMD, Single Instruction Multiple Data, (SSME2 - Streaming SIMD Extensions) per applicazioni multimediali (estensione del set MMX)Potenziamento delle memorie cacheIntroduzione di un numero di serie al processore(abilitazione via software)

20

Esempi di famiglie di calcolatori

INTEL Pentium IV

Disponibilità: dicembre 20001.3–2.20 Ghz di frequenza di clockPipeline a 20 stadiCirca 30 milioni di transistor in un chip64 GB di memoria indirizzabileBus di sistema a 400 Mhz144 nuove istruzioni SIMD per applicazioni multimedialiTecnologia di integrazione a 0.18-micronPotenziamento delle memorie cache

21

Esempi di famiglie di calcolatori

La famiglia INTEL: IL Pentium IV

22

Esempi di famiglie di calcolatoriLa famiglia INTEL: Il Pentium II

Architettura a 32 bit compatibile con i predecessoriAritmetica Floating Point IEEE 754Cache di 1° livello 16 KB dati + 16 KB istruzioniCache di 2° livello 512 KB nel package (a metà della frequenza della CPU)SEC (Single Edge Cartridge) a 242 pinDissipa oltre 50 Watt!!!

23

Esempi di famiglie di calcolatoriLa famiglia SPARC

Scalable Processor ARChitectureProposta da Sun Microsystems nel ’87Dedicata a workstation UnixNon prodotta direttamente da SunCaratteristiche principali

Insieme ridotto di istruzioni (55)Esecuzione non interpretataArchitettura a 32 bitUnità FP addizionale (14 istr.)

UltraSPARC I (1995)Registri e indirizzi a 64 bitVIS (Visual Instruction Set)Dedicata a sistemi high-end : dozzine di CPU, memorie di Tbyte

Ultra SPARC II e III

24

Esempi di famiglie di calcolatori

La famiglia SPARC: l’ULTRA SPARCIIArchitettura RISC a 64 bit, pensata per configurazione multiprocessor a 4 CPU con memoria condivisaCompletamente compatibile con il codice della sparc a 32 bitPackage con 787 piediniBus sincrono Sbus per l’I/OUPA (Ultra Port Architetture) per la comunicazione con la memoriaCache 1° livello interna 16KB + 16KBCache 2° livello esterna (divisa in tag e data), estendibile da 512Kb a 16MBUDB2 (Ultra Sparc Data Buffer II) per disaccoppiareCPU e memoria

25

Esempi di famiglie di calcolatori

La famiglia SPARC: l’ULTRA SPARCII

26

Esempi di famiglie di calcolatoriLa famiglia SPARC: l’ULTRA

SPARCIII

27

Esempi di famiglie di calcolatoriJava e Java Virtual Machine

Java: linguaggio di programmazione orientato aglioggetti introdotto da SUN

In alternativa al C++Risolve i problemi di sicurezzaGestione della multimedialità

JVM (Java Virtual Machine):Macchina virtuale che esegue un codice speciale (Java byte code)Il codice JVM può essere eseguito da interpreti software su diverse piattaforme

Obiettivo:distribuire, eventualmente su rete, software indipendente dalla piattaforma

28

Esempi di famiglie di calcolatori

Portabilità delle applicazioni Java

Codice JAVA

RETE

JAVA Compiler

JAVAMachine

(HW)

InterpreteJVM(SW)

Codice piattaforma HW

CompilatoreJust In Time

(SW)

Codice JVM

29

Esempi di famiglie di calcolatori

Java soluzioni HW e SWSoluzione SW (parziale):

Compilatori JIT (Just In Time)Compilazione al volo subito prima dell’esecuzioneRitardo di compilazione

Soluzione HW:Java Machine: implementazione Hardware della Java Virtual MachinePicoJava I e II:

Architettura definita da SunDiverse implementazioni disponibili

30

Esempi di famiglie di calcolatori

La famiglia pico Java: Sun Micro Java 701

Esegue direttamente codice JVMDestinata a sistemi embeddeb (da 100$)Package BGA (Ball Grid Array) a 316 pinL’economicità prevale sulle prestazioniMemoria + Flash PROM (programma)16 linee programmabili di I/O destinate a bottoni, interruttori, lampade etc. (16 pin)3 timer programmabili del chip10 pin per la diagnostica del chipChip opzionale di gestione I/O Bus PCI a 33/66 Mhz: compatibilità con schede per PC

31

Esempi di famiglie di calcolatori

La famiglia pico Java: Sun Micro Java 701