PROGETTO E REALIZZAZIONE DI UN CIRCUITO PER IL ......Figura 4.15 Schema a blocchi del circuito...

Transcript of PROGETTO E REALIZZAZIONE DI UN CIRCUITO PER IL ......Figura 4.15 Schema a blocchi del circuito...

UNIVERSITÀ DEGLI STUDI DI PERUGIA

FACOLTÀ DI INGEGNERIA

CORSO DI ELETTRONICA E DELLE TELECOMUNICAZIONI

PROGETTO E REALIZZAZIONE DI UN CIRCUITO PER IL

CONTROLLO DI UN SENSORE PER APPLICAZIONI DI

RADIOPROTEZIONE NELLA RADIOLOGIA INTERVENTISTICA

TESI DI LAUREA MAGISTRALE

LAUREANDA: RELATORE:

Michela Siena Dott. Ing. Pisana Placidi

CORRELATORI:

Ing. Elia Conti

Ing. Daniel Megalotti

ANNO ACCADEMICO 2011/2012

Indice

Introduzione 1

Capitolo 1 La Radiologia Interventistica e la radioprotezione

3

1.1 Radiologia Interventistica ...................................................................................3

1.2 Radioprotezione e grandezze dosimetriche.............................................6

1.3 Interazione particelle-materia................................................................10

1.3.1 Interazione dei fotoni con la materia............................................................... 11

1.3.2 Importanza relativa dei vari tipi di interazioni................................................ 17

1.3.3 Materiali equivalenti dal punto di vista dell’attenuazione dei fotoni.............. 18

Capitolo 2 Dosimetri commerciali 20

2.1 Dosimetri passivi...................................................................................23

2.1.1 Dosimetri a film sottile (film badge)............................................................... 18

2.1.2 Dosimetri a termoluminescenza (TLD) .......................................................... 26

2.2 Dosimetri attivi ......................................................................................28

2.2.1 Dosimetri a semiconduttore e dosimetri DIS .................................................. 28

2.2.2 Esempi di APD commerciali .......................................................................... 29

2.3 Il progetto RAPID .................................................................................35

Capitolo 3 Architettura 37

3.1 I blocchi costitutivi ................................................................................37

3.2 Il sensore ........................................................................................................... 40

3.3 CC430 e CC1111.......................................................................................47

Indice

II

Capitolo 4 Circuito di elaborazione 51

4.1 Algoritmo di clustering..........................................................................51

4.2 Implementazione del circuito di elaborazione ......................................63

4.3 Descrizione del circuito di elaborazione ...............................................67

4.4 Descrizione del circuito di emulazione del sensore MT9V011 ............71

4.4.1 Circuito di emulazione: versione 1 ................................................................. 72

4.4.2 Circuito di emulazione: versione 2 ................................................................. 81

Capitolo 5 Verifica del circuito di elaborazione 87

5.1 EMU_SENSOR_SEL = 1 ....................................................................87

5.2 EMU_SENSOR_SEL = 0 ....................................................................93

5.3 Occupazione delle risorse logiche su CPLD........................................96

5.4 Modello temporale dei CPLD MAX 7000 di Altera per il calcolo dei

ritardi ..........................................................................................................97

5.5 Verifica sperimentale su FPGA..........................................................100

Conclusioni 105

Appendice A 107

Bibliografia 112

Elenco delle figure

Figura 1.1 Nell’ordine, angiografia cerebrale (a) e angiografia degli arti inferiori (b) con

DSA 4

Figura 1.2 Angiogafo digitale con DSA 5

Figura 1.3 Sezione d’urto dei singoli meccanismi di interazione 12

Figura 1.4 Sezione d’urto in funzione dell’energia dei fotoni nel carbonio (a) e nel piombo

(b) 13

Figura 1.5 Lunghezza di assorbimento dei fotoni in materiali a vario Z [10] 14

Figura 1.6 Illustrazione dell’effetto fotoelettrico 14

Figura 1.7 Coefficiente di attenuazione massico per effetto fotoelettrico 15

Figura 1.8 Illustrazione del processo Compton 16

Figura 1.9 Illustrazione della generazione di una coppia 16

Figura 1.10 Coefficiente di attenuazione massico per acqua e piombo 17

Figura 1.11 Coefficiente di attenuazione massico per il silicio [10] 18

Figura 2.1 Posizionamento delle diffrenti tipologie di dosimetri [15] 21

Figura 2.2 Esempio di dosimetro total body e relativo posizionamento [16] 21

Figura 2.3 Esempio di dosimetro ad anello e relativo posizionamento [16] 21

Figura 2.4 Riproduzione grafica di un dosimetro a film 23

Figura 2.5 Schema di funzionamento di un densitometro [17] 24

Figura 2.6 Un esempio di grafico H-D [17] 25

Figura 2.7 Meccanismo fisico della termoluminescenza [17] 26

Figura 2.8 Esempio di curva di luminescenza [17] 27

Figura 2.9 Principio di funzionamento di un dosimetro a semiconduttore [18] 28

Figura 2.10 Camera di ionizzazione e cella di memoria MOSFET [18] 29

Figura 2.11 Unfors EDD-30 [20] 30

Figura 2.12 Il sistema DoseAware [23] 31

Figura 2.13 Il dosimetro Dosilab EDM- III 32

Figura 2.14 Il dosimetro TermoScientific EPD-MK2+ [26] 32

Figura 2.15 Il sistema dosimetrico RaySafe i2 [27] 33

Figura 2.16 Schema del sistema dosimetrico in base al progetto RAPID 36

Figura 3.1 I blocchi costitutivi del sistema 37

Figura 3.2 Diagramma a blocchi del sensore 40

Indice delle figure

II

Figura 3.3 Configurazione di default del sensore 41

Figura 3.4 Disposizione dei pin nel chip 42

Figura 3.5 Struttura della matrice di pixel attivi 43

Figura 3.6 Il modello di colori RGB 43

Figura 3.7 Illustrazione spaziale della lettura dell’immagine 44

Figura 3.8 Diagramma temporale dei dati forniti dal pixel 44

Figura 3.9 Andamento temporale relativo dei segnali master clock e pixel clock 45

Figura 3.10 Andamento temporale relativo dei segnali FRAME_VALID e LINE_VALID

45

Figura 3.11 Diagramma a blocchi funzionale della famiglia CC430F61xx [29] 48

Figura 3.11 Diagramma a blocchi funzionale della famiglia CC430F61xx [29] 48

Figura 3.12 Vista dall’alto del package della famiglia CC1111Fx [30] 49

Figura 3.13 Diagramma a blocchi delle famiglie CCF1110Fx/CCF1111Fx [30] 50

Figura 4.1 Visualizzazione dei fotoni che colpiscono la matrice di pixel del sensore [37] 52

Figura 4.2 Visualizzazione dei pixel in un cluster [37] : il pixel contrassegnato in giallo

non è topologicamente connesso al centro (S, in rosso). Degli 8 pixel topologicamente

connessi solo i due in arancio hanno un segnale superiore alla seconda soglia T2 e pertanto

fanno parte del cluster 53

Figura 4.3 (a) Distribuzione statistica del numero di fotoni in un frame e (b) correlazione

tra numero di fotoni e la relativa incertezza [37] 54

Figura 4.4 (a) Distribuzione statistica del segnale totale ricostruito e (b) correlazione tra il

segnale totale ricostruito e la relativa incertezza [37] 54

Figura 4.5 Distribuzione sperimentale del rumore dei singoli pixel del sensore 56

Figura 4.6 Distribuzione integrale del rumore dei singoli pixel del sensore 56

Figura 4.7 Distribuzione sperimentale dei piedistalli dei singoli pixel del sensore 57

Figura 4.8 Distribuzione integrale dei piedistalli dei singoli pixel del sensore 57

Figura 4.9 (a) Numero di pixel normalizzati sopra soglia in funzione del valore di soglia;

(b) numero di pixel sopra soglia in conteggi ADC in funzione del valore di soglia 58

Figura 4.10 (a) Errore relativo del numero di pixel normalizzati sopra soglia in funzione

del valore di soglia; (b) errore relativo del numero di pixel sopra soglia in conteggi ADC in

funzione del valore di soglia 59

Figura 4.11 (a) Integrale di carica in un frame in funzione del valore di soglia;

(b) somma dei segnali dei pixel sopra soglia in conteggi ADC in funzione del valore di

soglia 60

Indice delle figure

III

Figura 4.12 (a) Errore relativo dell’integrale di carica in un frame in funzione del valore di

soglia;

(b) errore relativo della somma dei segnali dei pixel sopra soglia in conteggi ADC in

funzione del valore di soglia 61

Figura 4.13 (a) Correlazione tra il numero di pixel sopra soglia e il tasso di dose misurato

dal dosimetro commerciale Unfors EDD-30; (b) correlazione tra la somma dei segnali dei

pixel sopra soglia e il tasso di dose misurato dal dosimetro commerciale Unfors EDD-30 62

Figura 4.14 (a) Correlazione tra il numero di pixel sopra soglia e il tasso di dose misurato

dai TLD;

(b) correlazione tra la somma dei segnali dei pixel sopra soglia e il tasso di dose misurato

dai TLD 63

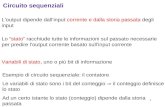

Figura 4.15 Schema a blocchi del circuito complessivo realizzato su CPLD 64

Figura 4.16 Realizzazione circuitale del blocco di confronto e incremento 67

Figura 4.17 Circuito di confronto e incremento: simulazione behavioral 68

Figura 4.18 Effetti della transizione di LINE_VALID sul circuito di confronto e

incremento 68

Figura 4.19 Dato corrente maggiore della soglia: il contatore è abilitato al conteggio 69

Figura 4.20 Dato corrente minore della soglia: il contatore non incrementa

NUMPIX_MICRO 69

Figura 4.21 Risultato della simulazione timing del blocco di confronto e incremento 70

Figura 4.22 Simulazione timing: ritardi nel circuito di confronto e incremento 70

Figura 4.23 Porzione di sensore emulato 71

Figura 4.24 Macchina a stati del circuito di emulazione del sensore MT9V011 73

Figura 4.25 Il sincronizzatore MealySinc 74

Figura 4.26 MealySinc: simulazione behavioral 75

Figura 4.27 Versione del sincronizzatore con 2 FF 76

Figura 4.28 Versione sincronizzatore con 2 FF: simulazione behavioral 76

Figura 4.29 Versione del sincronizzatore con 3 FF 77

Figura 4.30 Versione del sincronizzatore con 3 FF: simulazione timing 77

Figura 4.31 Realizzazione circuitale del blocco di emulazione del sensore MT9V011 nella

sua versione 1 78

Figura 4.32 Prima versione del circuito di emulazione del sensore MT9V011: simulazione

behavioral 78

Figura 4.33 Transizione da 0 a 1 di START_SEQ: la scansione è abilitata. Prima versione

Indice delle figure

IV

del circuito di emulazione 79

Figura 4.34 Comportamento di LINE_VALID_EMU quando FRAME_VALID_EMU è

alto. Prima versione del circuito di emulazione 80

Figura 4.35 Scansione della matrice terminata: LINE_VALID_EMU e

FRAME_VALID_EMU tornano bassi. Prima versione del circuito di emulazione 80

Figura 4.36 STOP_SEQ interviene e la scansione si arresta. Prima versione del circuito di

emulazione 80

Figura 4.37 Realizzazione circuitale del blocco di emulazione del sensore MT9V011 nella

sua seconda versione 81

Figura 4.38 Macchina a stati del circuito di emulazione del sensore MT9V011 nella sua

seconda versione 83

Figura 4.39 Seconda versione del circuito di emulazione: simulazione behavioral 84

Figura 4.40 Comportamento di FRAME_VALID_EMU, LINE_VALID_EMU e

DOUT_EMU, quando START_SEQ interviene. Seconda versione del circuito di

emulazione 84

Figura 4.41 Transizione da 0 a 1 di END_COUNT_ROW: scansione terminata. Seconda

versione del circuito di emulazione 85

Figura 4.42 Intervento di STOP_SEQ nel corso di un frame e successivo nuovo intervento

di START_SEQ. Seconda versione del circuito di emulazione 85

Figura 4.43 Seconda versione del circuito di emulazione: simulazione timing 86

Figura 4.44 Ritardo tra il fronte di salita del clock e la transizione di LINE_VALID_EMU.

Seconda versione del circuito di emulazione 86

Figura 5.1 Realizzazione circuitale del circuito complessivo realizzato su CPLD che

prevede la prima versione del circuito di emulazione 88

Figura 5.2 Circuito di elaborazione complessivo, prima versione del circuito di

emulazione, EMU_SENSOR_SELECT = 1: simulazione behavioral 89

Figura 5.3 Ritardo rispetto al fronte di salita del clock con cui sale

FRAME_VALID_MICRO 90

Figura 5.4 Ritardo tra la commutazione di OUT_AND_MONITOR, e la transizione di

DOUT al dato maggiore della soglia 90

Figura 5.5 Realizzazione circuitale del circuito complessivo realizzato su CPLD che

prevede la seconda versione del circuito di emulazione 91

Figura 5.6 Circuito di elaborazione complessivo, seconda versione del circuito di

emulazione, EMU_SENSOR_SELECT = 1: simulazione behavioral 92

Indice delle figure

V

Figura 5.7 Ritardo tra LINE_VALID_MON e fronte di salita del clock 93

Figura 5.8 Ritardo tra la transizione da 0 a 1 di OUT_AND_MON e OUT_COMP_MON,

e quella di DOUT_MON al dato maggiore della soglia 93

Figura 5.9 Circuito complessivo su CPLD, prima versione del circuito di emulazione

EMU_SENSOR_SEL = 0: simulazione behavioral 94

Figura 5.10 Analisi dei ritardi tra LINE_VALID_S e LINE_VALID_MON, e tra

DOUT_S e DOUT_MON 95

Figura 5.11 Ritardo di OUT_AND_MON e OUT_COMP_MON rispetto al fronte di salita

del clock 95

Figura 5.12 Ritardo tra il fronte di discesa di LINE_VALID_S e OUT_AND_MON 95

Figura 5.13 Circuito complessivo su CPLD, seconda versione del circuito di emulazione

EMU_SENSOR_SEL = 0: simulazione behavioral 96

Figura 5.14 Il modello temporale per il calcolo dei tardi nei CPLD Altera [42] 98

Figura 5.15 Modello circuitale per il calcolo di tCO [42] 99

Figura 5.16 Starter Kit Board dell’FPGA Spartan 3 di Xilinx 100

Figura 5.17 Schema a blocchi del circuito di emulazione del microcontrollore CC430 101

Figura A.1 Architettura di un PLD [39] 107

Figura A.2 Architettura di un CPLD [39] 108

Figura A.3 Architettura della famiglia MAX 7000 dell’Altera [40] 109

Figura A.4 Architettura di un LAB della famiglia MAX 7000 dell’Altera [40] 110

Figura A.5 Architettura di una macrocella in un LAB della serie MAX 7000 [40] 111

Elenco delle tabelle

Tabella 1.1 Parametri di lavoro dell’angiografo nelle procedure di RI [4] 6

Tabella 1.2 Valori di wr al variare del tipo di radiazione e del range di energia 7

Tabella 1.3 Valori di wt al variare del tipo di tessuto o organo colpito 8

Tabella 1.4 Tipiche dosi relative a singole procedure di arteriografia e drenaggio biliare 9

Tabella 1.5 Limiti di esposizione fissati dalla legge 9

Tabella 1.6 Importanza relativa dei tre processi in acqua 18

Tabella 2.1 Livelli di allarme impostati dalla casa costruttrice [20] 30

Tabella 2.2 Schema riassuntivo delle specifiche dei sensori Unfors EDD-30, Philips

DoseAware, Dosilab EDM-III , ThermoScientific EPD-Mk2+ e RaySafe i2 34

Tabella 2.3 Schema riassuntivo sui vantaggi e svantaggi di dosimetri attivi e passivi 35

Tabella 5.1 Risorse occupate sul CPLD nei due differenti casi di impiego della prima o

della seconda versione del circuito di emulazione 96

Tabella 5.2 Dettaglio delle macrocelle occupate dalle singole istanze che compongono il

cicuito complessivo nei due casi di utlizzo della prima e della seconda versione del circuito

di emulazione 97

Introduzione

Lo sviluppo di nuove e sofisticate tencologie ha reso l’impiego delle radiazioni

ionizzanti in medicina un’applicazione in continua evoluzione. La Radiologia

Interventistica rappresenta in tal senso uno degli ambiti di maggiore interesse, in cui si

fondono progresso tecnologico delle metodiche diagnostiche e soprattutto prestazioni

terapeutiche mini-invasive, volte alla graduale sostituzione dei trattamenti chirurgici

convenzionali.

In questo contesto si inserisce il tema della Radioprotezione degli operatori sanitari,

chiamati ad operare a stretto contatto con il paziente e dunque soggetti ad un’elevata

esposizione ai raggi X. Il monitoraggio della dose cui sono sottoposti i lavoratori è

condotto mediante l’utilizzo di dosimetri individuali, vale a dire opportuni dispositivi che

consentono la determinazione dell’esposizione del singolo individuo alle radiazioni

ionizzanti. I dosimetri certificati ed attualmente tipicamente impiegati sono dosimetri

passivi, quali dosimetri a film e dosimetri a termoluminescenza (TLD), che, pur basandosi

su tecnologie consolidate, non consentono la determinazione della dose in tempo reale. Le

fasi di misura e lettura dello strumento avvengono separatamente, e i tempi di risposta sono

dell’ordine dei giorni. La necessità di disporre di uno strumento più efficace ed efficiente

adatto allo scopo ha portato allo sviluppo di dosimetri attivi, basati su tecnologie a

semiconduttore ed in grado di fornire misure in tempo reale.

Il progetto RAPID (Real Time Active Pixel Dosimetry) nasce da una collaborazione tra

l’Istituto Nazionale di Fisica Nucleare (INFN) di Perugia, l’Università degli Studi di

Perugia, il Servizio di Fisica Sanitaria dell’ASL3 dell’Umbria presso l’Ospedale di Foligno

e il Servizio di Fisica Sanitaria dell’ASL1 dell’Umbria presso l’Ospedale di Città di

Castello. Il progetto è finalizzato alla realizzazione di un dosimetro individuale real time

con tecnologia wireless per il monitoraggio dell’effettiva dose cui sono soggetti gli

Introduzione

2

operatori nelle procedure di Radiologia Interventistica, attraverso l’impiego di un sensore a

matrice di pixel attivi (Active Pixel Sensor, APS). L’eliminazione dei tempi di attesa

consentirà la creazione di un archivio remoto delle dosi assorbite da ciascun operatore,

semplificando la pianificazione delle procedure e favorendo una gestione più efficace del

lavoro.

Il presente lavoro di tesi si inserisce nella progettazione e realizzazione del circuito

preposto al controllo del sensore di immagine per la rivelazione delle radiazioni. La

trattazione si articola nelle sezioni di seguito riassunte.

Il Capitolo 1 introduce la Radiologia Interventistica e fornisce i principi teorici e le

nozioni fisiche necessarie per la comprensione del funzionamento di un dispositivo per la

rivelazione di radiazioni in tale ambito applicativo.

Il Capitolo 2 presenta una panoramica generale sui principali dosimetri attualmente

commercializzati, distinguendo fra dosimetri attivi e passivi, e sottolineando i relativi

vantaggi e svantaggi. Ciò fornisce di fatto le motivazioni alla base della nascita del

progetto RAPID.

Il Capitolo 3 illustra l’architettura pensata per la realizzazione del sistema dosimetrico.

Viene descritto il ruolo di ciascun blocco costitutivo, con particolare riferimento al sensore

di radiazione.

Il Capitolo 4 descrive i dettagli relativi all’implementazione su CPLD della logica di

controllo e elaborazione per il sensore preposto alla rivelazione della radiazione. Vengono

in particolare descritti gli elementi funzionali e le specifiche del circuito dedicato

all’elaborazione dei dati provenienti dalla matrice di pixel attivi e di un circuito in grado di

emulare le funzionalità del sensore per scopi di test.

Il Capitolo 5 approfondisce la verifica del circuito di controllo complessivo

implementato su CPLD. Il corretto funzionamento del circuito implementato, in attesa

della realizzazione della scheda che ospita il CPLD, è stato verificato mappando la logica

progettata su di un dispositivo programmabile di tipo FPGA.

Le Conclusioni riassumono l’iter progettuale seguito e focalizzano l’attenzione sui

possibili sviluppi futuri.

Capitolo 1

La Radiologia Interventistica e la radioprotezione

Il Capitolo 1 introduce le problematiche connesse alla radioprotezione con particolare

riferimento allo scenario della Radiologia Interventistica (RI) e fornisce le basi fisiche per

la comprensione del principio di funzionamento di un dispositivo per la rivelazione di

radiazioni.

1.1 Radiologia Interventistica

La Radiologia è la branca della medicina che si occupa di fornire immagini (vere,

ricostruite o virtuali) dell’interno del corpo umano, con lo scopo di ottenere informazioni

utili alla diagnosi [1], sfruttando in primo luogo tecniche di imaging con raggi X, ma anche

ultrasuoni e risonanza magnetica. La Radiologia Interventistica (RI) rappresenta, a sua

volta, una moderna branca della Radiologia, ad altissimo contenuto tecnologico, che si

occupa della gestione mini-invasiva di problematiche cliniche: utilizzando immagini

prodotte con tecniche quali radioscopia, ecografia, tomografia, talvolta anche associate tra

loro, gli strumenti vengono guidati ai distretti corporei d’interesse senza la necessità di un

accesso chirurgico ed invasivo, vale a dire agendo per via percutanea. Ciò consente

notevoli vantaggi sia in termini di una minimizzazione dei rischi per il paziente sottoposto

alla procedura, permettendo spesso di operare in anestesia locale, sia per quanto riguarda

aspetti più prettamente logistici e di organizzazione, riducendo in tal senso i tempi di

ricovero, che diventano estremamente brevi e riconducibili spesso a prestazioni

ambulatoriali.

L’ angiografia è l’esame radiologico in grado di evidenziare i vasi sanguigni dei

La Radiologia Interventistica e la radioprotezione Capitolo 1

4

diversi distretti corporei al fine di studiarne morfologia ed eventuali alterazioni. Questa

metodica è resa possibile grazie all’utilizzo di particolari cateteri estremamente sottili che

consentono di raggiungere per via endovascolare il distretto da esaminare, anche con il

supporto di un mezzo di contrasto iodato che viene somministrato per visualizzare e

studiare in modo selettivo i vasi con le loro diramazioni [2]. Gli esami angiografici

vengono perciò comunemente eseguiti tramite l’utilizzo di raggi X e del suddetto mezzo di

contrasto, anche detto radio-opaco, in quanto reso necessario dal fatto che il sangue ha lo

stesso coefficiente di attenuazione per le radiazioni in questione dei tessuti circostanti. Si

possono essenzialmente individuare le varianti che seguono nelle tecniche di angiografia

classica:

- fluoroscopia digitale, caratterizzata da acquisizione di studi dinamici in bassa e

media risoluzione, bassa dose, con fascio pulsato o continuo;

- Digital Acquisition, caratterizzata da acquisizioni ad alta risoluzione e alta dose,

- Digital Subtraction Acquisition (DSA), in cui si acquisiscono immagini in

sottrazione digitale: alle immagini evidenziate dal mezzo di contrasto ne viene

sottratta una ottenuta prima dell'introduzione dell'agente di contrasto stesso, per

rimuovere la contaminazione di strutture statiche, che appariranno con la stessa

intensità prima e dopo l'introduzione del mezzo di contrasto. Vengono così esaltati i

condotti vascolari contrastati sottraendo i tessuti molli e scheletrici circostanti

precedentemente acquisiti.

Le immagini riportate in Figura 1.1 mostrano i risultati di angiografie eseguite su

differenti parti del corpo, in particolare angiografia cerebrale e agli arti inferiori, con DSA.

(a)

(b)

Figura 1.1 Nell’ordine, angiografia cerebrale (a) e angiografia degli arti inferiori (b) con DSA

La Radiologia Interventistica e la radioprotezione Capitolo 1

5

La procedura d’intervento sul paziente è normalmente svolta dal radiologo

interventista, o angiografista, in genere affiancato da altre figure professionali quali quella

del cardiologo, dell’infermiere e del tecnico sanitario di radiologia medica (TSRM).

L’apparecchiatura radiologica è in primo luogo rappresentata da un angiografo digitale,

costituito da un tubo radiogeno posto sotto al lettino su cui viene fatto accomodare il

paziente, che consente la realizzazione di proiezioni multiple dei diversi distretti vascolari

opacizzati, in tutta la loro estensione e in tempi molto brevi. Altre attrezzature necessarie

sono iniettori di contrasto, stent vascolari, cateteri a palloncino, ecc. In Figura 1.2 è

riportata la fotografia di un classico angiografo digitale che effettua la DSA.

Figura 1.2 Angiogafo digitale con DSA

Per ottimizzare l’immagine prodotta è possibile agire, variandoli in modo opportuno, su

alcuni parametri che influiscono sulle prestazioni fornite dall’angiografo, fra i quali

differenza di potenziale (in kV) applicata al tubo radiogeno, corrente (in mA) sull’anodo,

frequenza e durata degli impulsi nel caso di fascio impulsato. Valori tipici dei parametri

suddetti relativamente a procedure angiografiche svolte presso la ASL3 Umbria, Ospedale

San Giovanni Battista di Foligno sono sintetizzati nella Tabella 1.1.

Il principale svantaggio nelle procedure di Radiologia Interventistica è legato ad una

potenziale eccessiva esposizione ai raggi X da parte non solo del paziente, ma anche e

soprattutto dell’operatore, chiamato a lavorare a distanze molto ridotte dal paziente, con

La Radiologia Interventistica e la radioprotezione Capitolo 1

6

prolungati tempi di esposizione e spesso in assenza di adeguate schermature (guanti anti X,

schermi mobili, ecc.) [3]

Tabella 1.1

Parametri di lavoro dell’angiografo nelle procedure di RI [4]

Radiography

(Mean Values/procedure)

Radioscopy

(Mean Values/procedures) Procedures

No exposure/

procedure kV mA/mAs Time (s)

kV mA Time (min)

Pace maker 80 30 2-5

PercutaneousTransluminal

Angioplasty

14 76 400 4 80 30 10-45

Endoscopic Retrograde

Cholangio-

Pancreotography

8 74 160 0.5 80 30 10-30

Percutaneous

Transluminal Coronary

Angioplasty

15-30 fps-10

exposition

320 6 80 30 15-60

1.2 Radioprotezione e grandezze dosimetriche

La Radioprotezione è la disciplina che ha il compito fondamentale di “assicurare la

protezione degli individui esposti, della loro progenie e del genere umano nel suo insieme,

dagli eventuali danni che potrebbero derivare dallo svolgimento delle attività con rischio

da radiazioni ionizzanti”[5]. Le fonti principali di esposizione sono, in ordine di

importanza per quanto concerne il contributo, il fondo naturale (2.4 mSv/anno) e le

applicazioni mediche di diagnostica e terapia.

Quando un materiale è attraversato da una radiazione elettromagnetica si produce

ionizzazione ed eccitazione degli atomi bersaglio; qualora il mezzo colpito sia un tessuto

biologico, l’interazione fra atomi e molecole può produrre un’alterazione della struttura

elettronica, causandone danneggiamenti nei termini di un’alterazione della loro

funzionalità. Esistono attualmente diversi organismi internazionali che si occupano della

quantificazione e della caratterizzazione dei danni biologici prodotti in base al tipo di

radiazione ionizzante e del tessuto colpito, quali l’International Commission on

Radiological Units and Measurements (ICRU), l’International Commition on Radiological

Protection (ICRP) e la U.S. National Commission on Radiation Protection (NCRP) [6]. I

La Radiologia Interventistica e la radioprotezione Capitolo 1

7

parametri di riferimento definiti sono:

1. Dose assorbita (D): rappresenta il rapporto tra il valor medio dell’energia dε che

colpisce la materia in un volume infinitesimo di massa dm e la massa stessa. L’unità di

misura definita dal Sistema Internazionale è il gray (Gy), dove 1 Gy corrisponde a 1

Joule di radiazione assorbita da 1 kg di massa:

dm

dD

ε= (1.1)

2. Dose equivalente (H): tiene conto della diversa pericolosità dei vari tipi di radiazione.

Uno stesso tessuto, a parità di dose assorbita, risponde infatti in modo differente a

seconda della radiazione incidente. La dose equivalente si ricava allora pesando la dose

assorbita tramite un fattore adimensionale wr:

DwH r= (1.2)

La Tabella 1.2 mostra un quadro riassuntivo dei valori assunti da wr al variare del tipo

di particella incidente e dell’energia trasportata.

Tabella 1.2

Valori di wr al variare del tipo di radiazione e del range di energia

Radiation and energy range Radiation weighting factor ωR

Photons, all energies 1

Electrons and muons, all energies 1

Neutrons En < 10 keV 5

10 keV < En < 100 keV 10

100 keV < En < 2 MeV 20

2 MeV < En < 20 MeV 10

En > 20 MeV 5

Protons, except recoil photons, E > 2 MeV 5

α particles, nuclear fragments, heavy nuclei 20

L’unità di misura definita dal SI è il sievert (Sv): 1 Sv, a differenza di 1 Gy, produce gli

La Radiologia Interventistica e la radioprotezione Capitolo 1

8

stessi effetti biologici indipendentemente dal tipo di radiazione considerata. I fotoni

vengono trattati come la radiazione di riferimento e, analogamente agli elettroni, hanno

wr unitario; per fasci di neutroni il valore oscilla fra 3 e 11 a seconda dell’energia del

fascio, mentre per i raggi alfa sale a 20 e così via.

3. Dose efficace (E): misurata anch’essa in sievert, pondera la dose equivalente sul tipo di

tessuto investito grazie al fattore adimensionale wt, che tiene conto della diversa

radiosensibilità dei tessuti irraggiati:

∑=t

tt HwE (1.3)

La Tabella 1.3 riporta alcuni valori di wt in corrispondenza dell’organo o tessuto

colpito.

Tabella 1.3

Valori di wt al variare del tipo di tessuto o organo colpito

Organ or tissue Tissue weighting factor ωT

Gonads 0.20

Red bone marrow 0.12

Colon 0.12

Lung 0.12

Stomach 0.12

Bladder 0.05

Chest 0.05

Liver 0.05

Oesophagus 0.05

Thyroid gland 0.05

Skin 0.01

Bone Surface 0.01

Other organs or tissue 0.05

Con riferimento alle procedure di RI di arteriografia e drenaggio biliare svolte presso

l’Ospedale di Foligno, le dosi caratteristiche espresse in mSv relativamente a diverse zone

di esposizione, sono di seguito riassunte:

La Radiologia Interventistica e la radioprotezione Capitolo 1

9

Tabella 1.4

Tipiche dosi relative a singole procedure di arteriografia e drenaggio biliare

Angiografia arti inferiori Hp(10)(mSv) Drenaggio biliare Hp(10)(mSv)

POLSO DX 0.07 0.18

POLSO SIN 0.30 1.33

CRISTALLINO 0.11 0.07

SOTTO CAMICE 0.00 0.02

ARCO ALTEZZA

LETTINO

0.19 0.14

SOTTO PAZIENTE 8.94 289.97

La legge stabilisce i limiti di esposizione nei Decreti Legislativi

− 230/95 “Attuazione delle direttive 89/618/Euratom, 90/641/Euratom, 92/3/Euratom e

96/29/Euratom in materia di radiazioni ionizzanti”

− 187/00 “Attuazione della direttiva 97/43/EURATOM in materia di protezione

sanitaria delle persone contro i pericoli delle radiazioni ionizzanti connesse ad

esposizioni mediche

e successive modifiche ed integrazioni, che rappresentano i riferimenti normativi per

l’attività di radioprotezione.

Tabella 1.5

Limiti di esposizione fissati dalla legge

Lavoratori non esposti Lavoratori esposti

Cat. B Cat. A

ESPOSIZIONE ESTERNA mS/anno

Globale 1 6 20

Cristallino 15 50 150

Pelle 50 150 500

Estremità 50 150 500

I dati mostrano l’importanza crescente del monitoraggio dell’esposizione alle radiazioni

per il rispetto dei limiti massimi oltre i quali si potrebbe incorrere in danni alla salute. Ciò è

testimoniato anche dalle numerose pubblicazioni in tal senso [7], [8].

La Radiologia Interventistica e la radioprotezione Capitolo 1

10

1.3 Interazione particelle-materia

La rivelazione della radiazione è resa possibile dalla sua interazione con la materia,

perciò ogni sistema di rivelazione si basa sullo stesso meccanismo, per il quale il risultato

dell’interazione delle particelle con il mezzo è convertito in un segnale elettrico, che può

quindi essere letto, memorizzato ed elaborato.

Quando una particella energetica attraversa un mezzo, il campo elettrico associato alla

carica in movimento e quello generato dalla struttura elettronica del mezzo, determinano

un trasferimento di energia: in particolare la carica perde parte della sua energia a favore

del mezzo, e viene quindi convertita in portatori (coppie elettrone-lacuna, ioni, fotoni), i

quali sono a loro volta raccolti per la rivelazione della radiazione incidente. I principali

meccanismi di interazione variano con l’energia, le caratteristiche del target, la massa e la

carica della particella incidente e sono collisioni anaelastiche con la struttura atomica del

materiale, scattering elastico dai nuclei, reazioni nucleari, emissione della radiazione di

Cherenkov e radiazione di frenamento (o Bremsstrahlung); i primi due meccanismi di

interazione sono i più rilevanti, specialmente per particelle pesanti come protoni o ioni,

mentre gli altri risultano più importanti per particelle leggere, come elettroni o positroni ad

elevate energie [9].

Le collisioni avvengono prevalentemente con gli elettroni e raramente con i nuclei; in

tutti i casi, a causa del suddetto trasferimento di energia, esse portano gli atomi del mezzo

colpito ad uno stato eccitato e, se l’energia è sufficientemente elevata, determinano la

formazione di ioni (ionizzazione primaria). A sua volta uno ione altamente energetico può

innescare la generazione di nuovi ioni (ionizzazione secondaria). È bene sottolineare che

parlando di collisioni non si deve necessariamente pensare alle masse di due corpi che

entrano in contatto, ma in senso più generale all’interazione elettromagnetica fra particelle

cariche, che può avvenire perciò anche quando particella ed elettrone non entrano in

contatto; si parla in questo caso di collisioni a distanza.

Il processo di collisione è caratterizzato dalla sezione d’urto. Considerando un fascio

di particelle, con una distribuzione uniforme e F particelle per unità di tempo, che incide su

un dato target, chiamando Ns in numero medio di particelle diffuse nell’angolo solido dΩ

nell’unità di tempo, si può definire la sezione d’urto differenziale:

( )Ω

=ΩΩ d

dN

FE

d

d s1,

σ (1.4)

La Radiologia Interventistica e la radioprotezione Capitolo 1

11

La sezione d’urto totale può quindi essere ricavata come l’integrale su tutto l’angolo

solido:

∫ ΩΩ

=Ω dd

dE

σσ ),( (1.5)

Questa quantità ha le dimensioni di un’area ed è definita come la sezione normale alla

direzione del fascio al di fuori della quale la particella non viene deviata; tale definizione è

in realtà solo un’astrazione. Più precisamente σ può essere considerata come una misura

della probabilità d’interazione: maggiore è σ, maggiore è la probabilità di avere

un’interazione. Sulla base di questa ultima definizione σ può essere riferita non solo alle

collisioni ma anche ad altri tipi di interazioni.

1.3.1 Interazione dei fotoni con la materia

In base alla loro energia e alla natura del materiale, i fotoni subiscono nella materia

una grande varietà di processi, tra i quali quelli di maggiore rilevanza sono:

- effetto fotoelettrico

- effetto Compton

- creazione di coppie

rispettivamente per le basse, medie e alte energie.

Analizzando questi tipi di interazione si spiegano le principali caratteristiche dei

raggi X, in primo luogo la loro capacità di penetrare la materia molto maggiore rispetto alle

particelle cariche; ciò è dovuto al fatto che le sezioni d’urto che caratterizzano questi

processi sono molto più piccole rispetto a quelle associate ai processi relativi alle particelle

cariche. L’importanza relativa dei meccanismi di interazione è mostrata in Figura 1.3.

Ciascun processo può essere rappresentato con la sua sezione d'urto, che varia con

l’energia dei fotoni e con il numero atomico del materiale assorbente. La sezione d'urto

totale si ottiene sommando le sezioni d’urto relative ai singoli processi (in ordine,

rispettivamente, all’effetto fotoelettrico, all’effetto Compton, e alla creazione di coppie).

πστσ ++= ctot (1.6)

Quando, inoltre, un fotone interagisce con il mezzo colpito, esso viene assorbito o

comunque completamente rimosso dal fascio incidente; in altre parole un fascio di fotoni

La Radiologia Interventistica e la radioprotezione Capitolo 1

12

che attraversa un target è soltanto attenuato in intensità e non ridotto in termini di energia.

Figura 1.3 Sezione d’urto dei singoli meccanismi di interazione

L’attenuazione dell’intensità (I) di un fascio di fotoni che interagisce con la materia,

viene descritta da una legge di tipo esponenziale e dipendente dallo spessore (x) del mezzo

attraversato:

( ) ( )lxeIxI

µ−= 0 (1.7)

dove I0 è l’intensità del fascio incidente e µl è il coefficiente di assorbimento del materiale,

a sua volta definito come:

totAl n σµ = (1.8)

in cui σtot rappresenta la somma di tutte le σ delle interazioni sopra citate e nA è il numero

di atomi per unità di massa. La Figura 1.4 mostra l’andamento di σtot in funzione

dell’energia dei fotoni, nei casi di carbonio e piombo.

La lunghezza di assorbimento lµρλ /= , con ρ densità del mezzo, per alcuni materiali

a differente numero atomico, è riportata in Figura 1.5 al variare dell’energia dei fotoni

incidenti. La lunghezza di assorbimento lµρλ /= , con ρ densità del mezzo, per alcuni

La Radiologia Interventistica e la radioprotezione Capitolo 1

13

materiali a differente numero atomico, è riportata in Figura 1.5 al variare dell’energia dei

fotoni incidenti.

(a)

(b)

Figura 1.4 Sezione d’urto in funzione dell’energia dei fotoni nel carbonio (a) e nel piombo (b)

In un sensore di silicio (ρSi = 2.42 g/cm3), per fotoni nel range 1 – 100 keV, si ha

λ = (0.001 – 4) g/cm2, da cui un coefficiente di attenuazione µl = (2.42·103 – 0.6) cm-1.

Calcolando lo spessore di silicio ζ necessario ad attenuare il fascio incidente di un fattore e,

La Radiologia Interventistica e la radioprotezione Capitolo 1

14

tale che I(x) = I0/e ~ 30% I0 , si ottiene ζ = (4 – 1.5·104) µm. Per un sensore con spessore

inferiore ai 100 µm la radiazione non viene completamente assorbita nel mezzo; ci si

aspetta dunque di misurare solo parzialmente l'energia dei fotoni incidenti.

Figura 1.5 Lunghezza di assorbimento dei fotoni in materiali a vario Z [10]

Di seguito vengono descritti in sintesi i tre processi sopra citati.

L’effetto fotoelettrico consiste nell’urto tra un fotone e un atomo, con conseguente

assorbimento del fotone ed emissione di un elettrone dall’atomo, generalmente

appartenente ad una delle orbite più interne (Figura 1.6).

Figura 1.6 Illustrazione dell’effetto fotoelettrico

La Radiologia Interventistica e la radioprotezione Capitolo 1

15

Risulta, infatti, che un quanto ha maggiore probabilità di produrre effetti fotoelettrici

sugli elettroni degli strati atomici più legati. Perché siano rispettate le leggi di

conservazione dell’energia e dell’impulso, il fotone non può cedere tutta la sua energia ad

un elettrone libero: condizione necessaria affinché avvenga la cessione è che l’elettrone sia

legato ad un nucleo.

L’energia cinetica dell’elettrone emesso, detto fotoelettrone, è pari alla differenza tra

l’energia del fotone e l’energia di legame dell’orbita di appartenenza.

La sezione d’urto diminuisce molto rapidamente con l’energia dei fotoni incidenti; per

energie dei quanti inferiori a 1 MeV, la sezione d’urto è inversamente proporzionale a

(hν)3, dove hν è l’energia trasportata da un quanto, mentre per energie superiori la

diminuzione è più lenta. In corrispondenza delle energie di soglia del processo, inoltre,

presenta improvvise discontinuità per i differenti orbitali (M, L, K), come evidenziato dalla

traiettoria spezzata di µm (Figura 1.7).

Figura 1.7 Coefficiente di attenuazione massico per effetto fotoelettrico

Nell’ effetto Compton (Figura 1.8) il fotone interagisce con un elettrone atomico

considerato come un elettrone libero. Quando ci si riferisce ad un elettrone libero si intende

un elettrone la cui energia di legame è molto minore dell’energia del fotone che lo

colpisce. Pertanto mentre l’effetto fotoelettrico diventa molto probabile quando l’energia

La Radiologia Interventistica e la radioprotezione Capitolo 1

16

del fotone incidente è confrontabile con quella di legame, quando l’energia del fotone

cresce oltre il valore dell’energia di legame, l’effetto fotoelettrico decresce rapidamente e il

processo Compton diventa sempre più importante.

A seguito dell’urto, l’elettrone riceve parte dell’energia del fotone e viene emesso ad

un angolo θ, mentre il fotone, con energia ridotta, subisce una deflessione di un angolo φ.

Figura 1.8 Illustrazione del processo Compton

Se λ0 è la lunghezza d’onda del fotone incidente e λ quella del fotone scatterato,

studiando il processo Compton come urto tra due particelle e imponendo la conservazione

di energia e quantità di moto, si ricava:

)cos1(0 ϕλλλλ −=−=∆ c (1.9)

in cui λc è la lunghezza d’onda Compton.

La creazione di coppie (Figura 1.9) si verifica quando il fotone interagisce fortemente

solo con il campo elettromagnetico di un nucleo atomico, rilasciando tutta la sua energia

nel processo di creazione di una coppia, costituita da un elettrone e da un positrone.

Figura 1.9 Illustrazione della generazione di una coppia

La Radiologia Interventistica e la radioprotezione Capitolo 1

17

Il processo può avvenire solo se l’energia trasportata dai fotoni è sufficientemente elevata;

in particolare, essendo la massa a riposo dell’elettrone di 0.51 MeV, l’energia minima del

fotone per generare questo processo deve essere di 1.02 MeV.

1.3.2 Importanza relativa dei vari tipi di interazioni

Il coefficiente di attenuazione (calcolato dividendo la sezione d’urto per la densità del

mezzo massico ρ) viene utilizzato per valutare l’occorrenza dei vari tipi di interazione ed è

ampiamente utilizzato in radioprotezione perché consente di mettere a confronto materiali

con densità molto differenti. La Figura 1.10 e la Figura 1.11 mostrano rispettivamente

l’andamento per acqua e piombo, rappresentativi per materiali a basso Z, e silicio.

Per testare gli effetti prodotti dai raggi X sulla materia viene generalmente utilizzato

un fantoccio in materiale acqua equivalente; l’importanza dei vari tipi di interazione nel

fantoccio si evince dalla Tabella 1.6, in cui sono riassunte le percentuali di interazione in

base all’energia dei fotoni incidenti.

Figura 1.10 Coefficiente di attenuazione massico per acqua e piombo

La Radiologia Interventistica e la radioprotezione Capitolo 1

18

Figura 1.11 Coefficiente di attenuazione massico per il silicio [10]

Tabella 1.6

Importanza relativa dei tre processi in acqua

Relative Number of Interactions (%) Photon Energy (MeV)

σ Τ π

0.01 95 5 0

0.026 50 50 0

0.060 7 93 0

0.150 0 100 0

4.00 0 94 6

10.00 0 77 23

24.00 0 50 50

100.00 0 16 81

1.3.3 Materiali equivalenti dal punto di vista dell’attenuazione dei fotoni

Due materiali si dicono equivalenti per una determinata energia dei fotoni incidenti, se

in essi avvengono lo stesso numero e lo stesso tipo di interazioni, in volumi che

contengono masse uguali dei materiali confrontati. Il coefficiente di attenuazione massico

di un composto è ottenuto come somma dei contributi dei singoli elementi che lo

costituiscono, ciascuno moltiplicato per la relativa frazione di massa p:

∑=

=

N

i

ii

composto i

p1 ρ

µρµ

(1.10)

La Radiologia Interventistica e la radioprotezione Capitolo 1

19

dove N è il numero di elementi del composto. Utilizzando una composizione in tipo e

percentuale di atomi molto prossima a quella del materiale da emulare, è possibile

raggiungere una situazione molto vicina a quella ideale di composti perfettamente

equivalenti.

Capitolo 2

Dosimetri commerciali

Nella radioprotezione degli operatori il monitoraggio individuale riveste un ruolo

importante in quanto consente di programmare in modo sicuro ed efficiente le esposizioni,

al fine di mantenere la dose ricevuta quanto più bassa possibile e comunque al di sotto dei

limiti stabiliti dalle normative vigenti [11]-[13]. La valutazione della dose cui sono

sottoposti i lavoratori è condotta mediante l’utilizzo di dosimetri individuali, vale a dire

opportuni dispositivi che consentono la determinazione dell’esposizione del singolo

individuo alle radiazioni ionizzanti. L’importanza dell’accuratezza nelle misure di dose

assorbita per scopi di radioprotezione è anzitutto legata alla necessità di non sottovalutare

gli effetti e le conseguenze per la salute umana che possono verificarsi. Inoltre un adeguato

livello di accuratezza nella dosimetria è necessario anche per evitare indebiti costi

economici per interventi preventivi o di rimedio non realmente necessari; vale a dire la

possibilità di avere a disposizione misure affidabili di dose consente di attuare

esclusivamente gli interventi strettamente necessari per la protezione degli operatori

esposti, in un’ottica di efficacia ed efficienza [14].

In base alle modalità di utilizzo dello stesso, il dosimetro può essere essenzialmente di

tipo total body (a corpo intero), da indossare a livello del torace e sopra l’eventuale camice

protettivo piombato, ad anello alle dita, al cristallino, o presentarsi come bracciale al

polso (Figura 2.1, Figura 2.2, Figura 2.3). Ogni dispositivo viene tarato su un fantoccio

equivalente tenendo conto della posizione in cui sarà posto e pertanto è indispensabile che,

a seconda della taratura, il dosimetro venga posto esclusivamente sulla parte del corpo di

interesse, altrimenti la misura fornita non potrebbe essere correlabile alla dose assorbita.

Dosimetri commerciali Capitolo 2

21

Figura 2.1 Posizionamento delle diffrenti tipologie di dosimetri [15]

Figura 2.2 Esempio di dosimetro total body e relativo posizionamento [16]

Figura 2.3 Esempio di dosimetro ad anello e relativo posizionamento [16]

Talvolta, nel caso di operatori particolarmente esposti, viene fornito un secondo dosimetro

Dosimetri commerciali Capitolo 2

22

total body da indossare sotto al camice piombato, [15]; ciò al fine di garantire che la

misura complessiva di dose sia affidabile e corrispondente all’effettiva esposizione anche

nel caso di massicce quantità di radiazioni ionizzanti. Le principali caratteristiche di un

dosimetro cui fare riferimento per caratterizzarne le prestazioni riguardano: sensibilità e

risoluzione, range e soglia di rivelazione, risposta lineare con la dose, omogeneità e

riproducibilità.

Le istruzioni per l’utilizzo dei dosimetri personali da parte del personale medico sono

dettate dall’articolo 68 del decreto legislativo 230/95, che sancisce le seguenti direttive

comportamentali:

− il dosimetro è personale e non può quindi essere ceduto o prestato ad altre persone;

− il dosimetro deve essere portato per tutto il tempo di permanenza nei locali interessati

dall’esposizione alle radiazioni ionizzanti e non può, salvo diversa indicazione, essere

trasportato all’esterno della Struttura d’appartenenza;

− il dosimetro total body deve essere sempre portato all’altezza del petto sul risvolto del

colletto o sul taschino del camice avendo cura che non sia schermato da alcun oggetto;

− quando viene indossato un indumento protettivo (grembiule e/o camice in gomma

piombifera), il dosimetro total body deve essere portato sotto tale indumento;

− il dosimetro a bracciale deve essere indossato al polso prima di effettuare ogni

manipolazione che comporti esposizioni a radiazione ionizzante;

− il dosimetro a bracciale deve essere sempre portato sotto eventuali guanti protettivi;

− al termine del lavoro, il dosimetro deve essere riposto in un luogo ove non sussista

alcuna possibilità d’esposizione alle radiazioni ionizzanti;

− il dosimetro non deve essere esposto di proposito a sorgenti di radiazioni ionizzanti;

− è obbligo del lavoratore l’accurata conservazione del dosimetro: in particolare, il

dosimetro non deve mai né venire a contatto di liquidi, né essere posto vicino a fonti di

calore, né essere aperto o manomesso in alcun modo;

− è obbligo del lavoratore consegnare, secondo la periodicità stabilita, il dosimetro alla

persona incaricata di effettuarne regolarmente il cambio;

− è fatto obbligo di segnalare tempestivamente l'eventuale deterioramento o smarrimento

del dosimetro al Servizio di Fisica Sanitaria, che provvederà alla sua sostituzione;

nell’attesa, l’operatore non può svolgere l’attività che lo espone a rischio da radiazioni

ionizzanti.

In questo capitolo verranno illustrate le diverse tipologie di dosimetri attualmente

Dosimetri commerciali Capitolo 2

23

disponibili, descrivendone i principi teorici di funzionamento ed evidenziando i relativi

vantaggi e svantaggi applicativi.

2.1 Dosimetri passivi

I dispositivi certificati ed attualmente tipicamente sfruttati per la misura individuale

della dose sono dosimetri passivi, quali dosimetri a film e dosimetri a termoluminescenza

(TLD).

2.1.1 Dosimetri a film sottile (film badge)

Sono essenzialmente costituiti da un contenitore in cui è inserita una pellicola

fotografica. Una rappresentazione grafica è fornita in Figura 2.4.

Figura 2.4 Riproduzione grafica di un dosimetro a film

La pellicola è formata da un supporto, normalmente acetato di cellulosa, su cui è

depositata l'emulsione, vale a dire un sottile strato di gelatina (da un millimetro a qualche

centinaia di micron) contenente piccoli granuli di bromuro di argento (AgBr). Sotto

l'azione della radiazione un granulo di AgBr viene ionizzato, e durante i processi di

sviluppo e fissaggio il bromo viene asportato, lasciando solo l'argento. Di conseguenza sul

fondo di gelatina trasparente si passa dalla cosiddetta immagine latente (sviluppo),

costituita dall'argento metallico, all'annerimento della pellicola (fissaggio) proprio nei

punti dove è fissato l'argento. Il processo di sviluppo costituisce una fase estremamente

delicata in quanto un errore di 2°C nella temperatura di sviluppo porta ad un errore del

10% sulla lettura, mentre l'errore di 1 minuto sulla durata conduce a un errore del 20%; è

Dosimetri commerciali Capitolo 2

24

perciò necessario agire con attenzione per la determinazione di temperatura e durata

ottimali per il processo.

La misura dell'annerimento della pellicola viene effettuata mediante il densitometro

(Figura 2.5). Un densitometro è un dispositivo messo a punto per misurare la densità ottica,

cioè il potere di assorbimento di luce, di un’immagine fotografica o stampata.

Figura 2.5 Schema di funzionamento di un densitometro [17]

Il fascio di luce prodotto da una sorgente di intensità I0 incide sul dosimetro con

intensità I, dopo aver attraversato un diaframma e la pellicola stessa. Una cellula

fotoelettrica libera a questo punto un numero di elettroni proporzionali all'intensità della

luce incidente, generando una corrente misurabile con un microamperometro in un circuito

esterno. Questo strumento richiede una taratura preventiva per il controllo dello zero del

circuito della cella: in assenza di film interposto, la lettura della corrente deve essere nulla,

mentre si deve avere corrente quando viene esaminata una pellicola esposta.

In base alla definizione di densità ottica (d0), un'emulsione ha densità ottica 1 se

trasmette un decimo della luce incidente:

=

I

Id 0

100 log (2.1)

Poiché la densità ottica in un punto dipende dall'energia ceduta nel punto dalle radiazioni,

essa è in diretta relazione con la dose, purché si abbia l'avvertenza di sottrarre prima il

fondo della pellicola. In particolare è possibile stabilire una ralazione lineare fra d0 e la

Dosimetri commerciali Capitolo 2

25

fluenza di particelle Ф, attraverso cui risulta proporzionale alla dose assorbita. Pertanto,

indicando con S la sezione di un granulo, con n il numero di grani anneriti per cm2 e con N

il numero totale di grani per cm2 di superficie, si può scrivere

( ) eeSNd S

100 log1 Φ−−= (2.2)

che per piccole fluenze, ovvero SФ<<1, diventa

eNSd 102

0 logΦ= (2.3)

in accordo con quanto anticipato sopra.

Le emulsioni sono utilizzate negli intervalli di linearità fra la densità ottica e la fluenza.

Questi intervalli sono ricavabili dai grafici H-D, così chiamati dal nome degli autori Hurter

e Driffield, che mostrano l’andamento di d0 in funzione di Ф. Un esempio di grafico H-D è

riportato in Figura 2.6,in cui è evidenziato il tratto di caratteristica lineare.

Figura 2.6 Un esempio di grafico H-D [17]

Prima del suo impiego una pellicola deve essere tarata, per avere la curva di densità ottica

netta in funzione della grandezza dosimetrica da misurare (esposizione, dose, ecc.).

Si parla di fading per indicare la perdita d’informazione nel tempo; nei dosimetri a film

questa si attesta intorno al 20÷30% mensile, per cui è consigliabile sostituirli al personale

ogni 1÷2 mesi, mentre la lettura può essere ripetuta in ogni momento. Per questo motivo

sono ancora oggi spesso preferiti ai TLD. I dosimetri a film sottile sono impiegati per

fotoni e particelle β [17].

Dosimetri commerciali Capitolo 2

26

2.1.2 Dosimetri a termoluminescenza (TLD)

Il fenomeno fisico sul quale si basa il funzionamento dei TLD è la termoluminescenza,

che si manifesta in alcune sostanze isolanti (ad esempio CaF2, LiF o BeO), dette fosfori,

sotto forma di una debole luce emessa per riscaldamento a seguito di una esposizione a

radiazione. Il meccanismo del fenomeno si spiega con la presenza di livelli energetici nel

gap proibito del materiale, originati dalla presenza di attivatori, come impurità o difetti

reticolari, nella struttura cristallina. L'energia ceduta dalla radiazione incidente produce il

passaggio di alcuni elettroni dalla banda di valenza V alla banda di conduzione C (Figura

2.7), con la conseguente formazione di lacune nella banda di valenza. Alcuni elettroni e

lacune si ricombinano immediatamente, mentre altri sono catturati in questi livelli

energetici metastabili e vi possono rimanere intrappolati a lungo, a meno che non

intervengano fenomeni in grado di fornire loro l’energia necessaria per sfuggire alle

trappole. In questo caso, alcuni elettroni passano nella banda di conduzione e ricadono,

esaurito il rispettivo tempo di vita medio, nella banda di valenza, dove possono

ricombinarsi con le lacune. È in questo processo, detto di termoluminescenza, che si

verifica l'emissione di luce visibile (Figura 2.7).

Figura 2.7 Meccanismo fisico della termoluminescenza [17]

Man mano che viene trasferito calore al cristallo, aumenta lo svuotamento delle

trappole, finché a una determinata temperatura tutte le trappole di un determinato livello

energetico risultano vuote. Il grafico dell'intensità della luce emessa in funzione della

temperatura, o del tempo di riscaldamento, presenta una successione di picchi,

corrispondenti alla completa liberazione delle trappole di un dato livello, preceduti da lente

risalite, legate all’inizio dello svuotamento di ogni nuovo livello. Ciascun picco successivo

Dosimetri commerciali Capitolo 2

27

è piu intenso del precedente, in quanto i livelli sono man mano più energetici,

conseguentemente ogni nuova discesa è più ripida della precedente. Tale curva, graficata in

Figura 2.8, è caratteristica di ogni sostanza ed è detta curva di luminescenza (glow curve).

L’area di ogni picco è proporzionale alla dose assorbita.

Figura 2.8 Esempio di curva di luminescenza [17]

I TLD sono perciò realizzati sfruttando cristalli che esibiscono il fenomeno della

termoluminescenza; questi dispositivi “accumulano” la radiazione assorbita per un fissato

periodo temporale e periodiamente vengono sottoposti alla lettura tramite un processo di

riscaldamento a circa 400°C. La frequenza con cui avvengono i salti energetici è legata alla

frequenza della radiazione incidente; si può, quindi, risalire alla misura della dose di

radiazione ionizzante cui è stato esposto l’operatore nell’arco temporale considerato. Prima

di essere usato, il TLD deve essere azzerato, attraverso una preventiva fase di annealing,

allo scopo di svuotare le trappole e di renderle stabili, secondo procedimenti diversi per

ogni sostanza. Esempi di TLD sono quelli riportati in Figura 2.2 e Figura 2.3.

I TLD sono sensibili nel range energetico compreso tra 10 keV e 3 MeV. Le misure non

avvengono in tempo reale e i tempi di risposta sono lunghi, circa qualche giorno, visto che

le fasi di misura e di lettura del dispositivo sono separate e spesso affidate a servizi sanitari

differenti. La misura fornita, inoltre, è relativa alla dose integrale, non permettendo quindi

di ottimizzare istante per istante l'esposizione nelle procedure, e, poiché la periodicità di

sostituzione è mensile, si perde l'informazione sull'esposizione nei singoli interventi.

Dosimetri commerciali Capitolo 2

28

2.2 Dosimetri attivi

Accanto ai dosimetri passivi sono disponibili in commercio dosimetri attivi (Active

Personal Dosimeters, APD), che sfruttano tecnologie a semiconduttore e si basano su

sistemi di rivelazione che forniscono una risposta diretta e istantanea della dose [18]. Il

passo avanti rispetto ai dosimetri passivi è proprio quello di fornire delle valutazioni in

tempo reale dell’esposizione alle radiazioni, talvolta anche grazie alla dotazione di segnali

acustici che allertano l’operatore nel caso di raggiungimento dei limiti previsti,

consentendo di intervenire tempestivamente ed efficacemente nella riorganizzazione delle

attività lavorative.

2.2.1 Dosimetri a semiconduttore e dosimetri DIS

Nei dosimetri a semiconduttore (diodi al silicio) la radiazione ionizzante interagisce

nella regione di svuotamento determinando la produzione di coppie elettrone-lacuna; le

particelle cariche generate vengono quindi separate e raccolte per effetto della differenza di

potenziale applicata Figura 2.9. Ciò produce nel diodo un impulso che viene a sua volta

processato dall’elettronica di elaborazione prevista.

Figura 2.9 Principio di funzionamento di un dosimetro a semiconduttore [18]

Generalmente utilizzati per raggi X e gamma, possono talvolta essere sfruttati per la

rivelazione di neutroni grazie all’utilizzo di materiali che convertono il flusso neutronico in

Dosimetri commerciali Capitolo 2

29

particelle cariche [18].

Il dosimetro Direct Ion Storage (DIS) nasce dall’accoppiamento tra una camera a

ionizzazione e una cella di memoria non volatile che utilizza la tecnologia MOSFET

(Metal Oxide Semiconductor Field Effect Transistor), consentendo di rivelare raggi X,

raggi gamma, raggi beta e neutroni. La radiazione incidente induce la ionizzazione del

dispositivo, provocando un’alterazione della carica sul floating gate; la variazione della

carica è quindi direttamente correlabile con la dose assorbita e ciò consente di effettuare la

misura. Le prestazioni del dispositivo possono essere ottimizzate tramite la scelta più

opportuna del materiale che costituisce le pareti e il gas.

Figura 2.10 Camera di ionizzazione e cella di memoria MOSFET [18]

L’utilizzo del floating gate del MOSFET come uno degli elettrodi della camera a

ionizzazione permette la miniaturizzazione del dispositivo, evita la necessità di

un’alimentazione durante la fase di accumulazione della dose e consente che la lettura

avvenga senza distruzione dell’informazione dosimetrica [19]. La lettura della carica

immagazzinata, inoltre, viene svolta senza “disturbare” la carica stessa, misurando la

conducibilità del transistore.

2.2.2 Esempi di APD commerciali

Il presente paragrafo illustra alcuni esempi di dosimetri attivi attualmente

commercializzati, quali Unfors EDD-30, Philips DoseAware, Dosilab EDM-III,

ThermoScientific EPD-MK2+ e RaySafe i2, sottolineando le peculiarità di ciascuno.

− Unfors EDD-30

L’Unfors EDD-30 (Figura 2.11) è un semplice dosimetro formato da un piccolo rivelatore

a stato solido posto su un cavo collegato a un display. Il sensore può misurare la dose e il

Dosimetri commerciali Capitolo 2

30

rateo di dose per una specifica parte del corpo, per esempio gli occhi, mani, piedi, o per il

corpo intero. Viene misurato, inoltre, anche il tempo totale di esposizione. Una volta

posizionati sensore e display si accende lo strumento e la dose viene automaticamente

misurata in accumulazione.

Figura 2.11 Unfors EDD-30 [20]

Raggiunto il livello impostato di dose o di rateo di dose si attiva un allarme sonoro che

avverte in tempo reale l’operatore del superamento dei limiti. La casa costruttrice imposta

livelli di allarme nominati body, eye e hand per produrre un segnale acustico di modo che

l’operatore venga stimolato a correggere il proprio comportamento e i propri metodi

durante l’esecuzione di una data procedura.

Tabella 2.1

Livelli di allarme impostati dalla casa costruttrice [20]

Set Up Livello di allarme 1

Rateo di Dose

Livello di allarme 2

Rateo di Dose

Livello di allarme 3

Rateo di Dose

Body 0.1 mSv/h 0.5 mS/h 2.5 mSv/h

Eye 0.3 mSv/h 1.5 mSv/h 7.5 mSv/h

Hand 1.0 mSv/h 5.0 mSv/h 25 mSv/h

FrEE 0.3 mSv/h 1.5 mSv/h 7.5 mSv/h

Il dosimetro opera su una banda di 10 Hz, alimentato con due batterie alcaline e si spegne

automaticamente dopo due ore di inattività o in assenza di radiazioni rilevate; il sensore ha

inoltre una risposta di rivelazione sferica, permettendo la misura della dose

indipendentemente dall’angolo incidente della radiazione [22].

Dosimetri commerciali Capitolo 2

31

− Philips DoseAware

DoseAware consente di ottenere informazioni in tempo reale sulla dose assorbita,

fornendo un rapido accesso alla storia di esposizione di ciascun operatore. Il sistema si

compone di uno schermo touch screen (base station) che visulizza le informazioni relative

a ciascun lavoratore memorizzato (è prevista la possibilità di creare una rete con

molteplici base stations i cui dati sono elaborati da un apposito software), e di un piccolo

dosimetro personale (Personal Dose Meter) che rileva la radiazione e trasmette le

informazioni alla base station, consentendone la visualizzazione real time. Sono poi

forniti oggetti accessori utilizzati per riporre i dispositivi quando non in uso. La dotazione

è mostrata in Figura 2.12.

Figura 2.12 Il sistema DoseAware [23]

La stazione base viene posizionata nella stanza in cui vengono effettuate le procedure, in

modo che sia visibile a tutto il personale impegnato; gli operatori, ciascuno dei quali

indossa il dosimetro personale, possono controllare in tempo reale la rispettiva situazione,

grazie a tre livelli di attenzione crescente, vale a dire verde, giallo e rosso.

Il range di dose relativamente al sensore è compreso fra 1µSv e 10Sv, con una risoluzione

di 1µSv e un’incertezza con cui vengono fornite le misure che si attesta al 5%, [23].

− Dosilab EDM-III

Il dosimetro Dosilab EDM-III esibisce un un energy range di misura compreso fra 20 keV

e 6 MeV, di cui l’intervallo da 20 keV e 1.5 MeV per la rivelazione di fotoni (raggi X e

Gamma), e quello da 1.5 MeV a 6 MeV per radiazioni beta. Il display di cui è fornito il

dispositivo (Figura 2.13) permette di visualizzare i valori di corrente alternativamente per

misure di deep dose, con una profondità di 10 mm (Hp10), shallow dose, con una

profondità di 0.07 mm (Hp0.07), deep dose rate (Hp10/h) e shallow dose rate (Hp0.07/h).

Dosimetri commerciali Capitolo 2

32

Lo stesso display informa relativamente a situazioni di allerta, come il raggiungimento dei

limiti di esposizione fissati per gli operatori o un basso livello di batteria. È possibile

immagazzinare fino a 50 esposizioni con almeno un minuto di intervallo fra due

esposizioni consecutive; qualora avvengano due esposizioni nell’arco di uno stesso

minuto, il dosimetro le considera come fossero una soltanto, sommando i risultati di

misura di ciascuna [24].

Figura 2.13 Il dosimetro Dosilab EDM- III

− ThermoScientific EPD-Mk2+

Nato come evoluzione del progetto originale Mk2, si tratta di un dispositivo utilizzabile

sia come dosimetro stand alone, che come elemento di un più complesso sistema

dosimetrico, grazie agli strumenti hardware e software messi a disposizione dalla casa

produttrice. Il dosimetro EPD-Mk2+ si presenta come mostrato in Figura 2.14.

Figura 2.14 Il dosimetro TermoScientific EPD-MK2+ [26]

Risulta sensibile ai raggi X, gamma e alle particelle beta, offrendo prestazioni avanzate nel

range tra 15 keV e 10 MeV. È prevista la possibilità di configurare un allarme acustico che

avverta il raggiungimento dei limiti di esposizioni, mentre display e funzioni sono

controllabili per mezzo di un singolo pulsante posizionato sul pannello frontale dell’unità,

opportunamente “incassato” per evitare operazioni indesiderate. È inoltre possibile

Dosimetri commerciali Capitolo 2

33

eseguire dei controlli di integrità prima dell’utilizzo, quali test sulla batteria e sul detector,

o lettura della tensione fornita dalla batteria stessa [26].

− RaySafe i2

Il dispositivo RaySafe i2 fornisce informazioni accurate, real time e di facile lettura sulla

dose assorbita dagli operatori impegnati nelle procedure di RI. Il sistema dosimetrico nel

suo complesso (Figura 2.15) si compone in primo luogo di un dosimetro attivo (i2

Dosimeter), per la lettura e memorizzazione della dose secondo per secondo; i dati raccolti

sono quindi inviati con tecnologa wireless ad un display touch screen (i2 real time

display), che visualizza le informazioni provenienti da tutti i dosimetri collegati in tempo

reale; barre che possono essere di colore verde, giallo e rosso sono utilizzate per fornire

un’informazione qualitativa immediata del livello di pericolosità cui è giunto ciascun

opratore. Selezionando inoltre uno qualsiasi degli operatori memorizzati e presenti in lista

si accede alla storia personale di ciascuno. Accanto alla strumentazione hardware sono

infine forniti i software RaySafe i2 dose viewer e RaySafe i2 dose manager, per analisi

avanzate di dati, operazioni di archivio e gestione di display multipli [27].

Figura 2.15 Il sistema dosimetrico RaySafe i2 [27]

La Tabella 2.2 schematizza le pricipali caratteristiche dei dosimetri attivi descritti nel

paragrafo, consentendo un rapido confronto delle relative specifiche.

Nonostante i notevoli vantaggi sottolineati relativamente all’utilizzo dei sistemi

dosimetrici attivi, questi non sono ancora in grado di fornire le stesse prestazioni dei

dosimetri passivi con il tipo di raggi X utilizzati durante le procedure; la loro risposta è

infatti più scarsa rispetto ai TLD e l’energy range in cui lavorano ha un limite inferiore

maggiore (14-48 keV contro i 10 keV dei TLD).

Dos

imet

ri c

omm

erci

ali

C

apit

olo

2

34

Tab

ella

2.2

Sch

ema

rias

sunt

ivo

dell

e sp

ecif

iche

dei

sen

sori

Unf

ors

ED

D-3

0, P

hili

ps D

oseA

war

e, D

osil

ab E

DM

-III

, T

herm

oSci

enti

fic

EP

D-M

k2+

e R

ayS

afe

i2

U

nfo

rs E

DD

-30

[2

1]-

[22

]

Ph

ilip

s D

ose

Aw

are

[2

3]

D

osi

lab

ED

M-I

II [

25

] T

he

rmo

Sci

en

tifi

c E

PD

-Mk

2+

[2

6]

Ra

yS

afe

i2

[2

7]

Tip

olo

gia

di

sen

sore

se

mic

on

du

tto

re

sem

ico

nd

utt

ore

se

mic

on

du

tto

re

sem

ico

nd

utt

ore

se

mic

on

du

tto

re

Ap

pli

cazi

on

e

pri

nci

pa

le

do

sim

etr

ia o

pe

rato

ri

do

sim

etr

ia o

pe

rato

ri

do

sim

etr

ia o

pe

rato

ri

do

sim

etr

ia o

pe

rato

ri

do

sim

etr

ia o

pe

rato

ri

Co

nn

ett

ivit

à

wir

ed

(se

nso

re c

oll

eg

ato

ad

un

'un

ità

di

visu

ali

zza

zio

ne

po

rta

tile

)

wir

ele

ss

–

inte

rfa

ccia

IR

fin

o a

1 m

wir

ele

ss r

ad

io c

om

mu

nic

ati

on

con

i d

osi

me

tri

– p

ort

e

eth

ern

et

10

/10

0 M

bit

/s

con

ne

ssio

ne

de

l d

ose

ma

na

ge

r

All

arm

e

si

–

–

si

si

Dim

en

sio

ni

sen

sore

6

x 1

1 x

22

mm

–

–

8

5 x

63

x 1

9 m

m

30

0 x

25

0 x

60

mm

Dim

en

sio

ni

alt

ri

dis

po

siti

vi

un

ità

di

visu

ali

zza

zio

ne

: 8

2 x

98

x 2

1 m

m l

un

gh

ezz

a c

avo

: 1

.5 m

–

–

–

–

En

erg

y r

an

ge

0

.01

4 –

0.1

20

Me

V (

±1

0%

) 0

.04

8 –

0.1

00

Me

V (

±3

0%

) 0

.02

– 6

Me

V

0.0

15

– 1

0 M

eV

N

-40

– N

-10

0 (

33

– 8

4 k

eV

)

N-1

00

– N

-12

0 (

84

– 1

01

ke

V)

Do

se r

an

ge

1

0 n

Sv

– 9

99

9 S

v –

1

μS

v –

1 S

v 0

μS

v –

16

Sv

1 μ

Sv

– 1

0 S

v

Do

se r

ate

ra

ng

e

0.0

3 m

Sv/

h –

2 S

v/h

4

0 µ

Sv/

h –

30

0 m

Sv/

h

0.5

μS

v/h

– 1

Sv/

h

0 μ

Sv/

h –

4 S

v/h

4

0 μ

Sv/

h –

15

0 m

Sv/

h (

±1

0%

)

15

0 m

Sv/

h –

30

0 m

Sv/

h (

±2

0%

)

Te

mp

o e

spo

sizi

on

e

10

ms

– 9

99

9 s

–

–

–

–

Ris

po

sta

sf

eri

ca (

v. d

ett

ag

li i

n [

22

])

–

–

an

iso

tro

pa

(v.

de

tta

gli

in

[2

6])

–

Se

nsi

bil

ità

–

–

–

–

–

Ca

lib

razi

on

e

N-8

0 (

80

Kvp

, 2

mm

Cu

an

d

4m

m A

l)

–

–

–

N-4

0,

N-1

00

, N

-12

0

Du

rata

ba

tte

rie

1

30

ore

(2

pil

e A

A)

–

–

1.5

V a

lca

lin

e:

45

– 5

0 c

on

tin

uo

,

~ 1

0 m

esi

in

OF

F m

od

e

3.6

V l

ith

ium

: 5

me

si c

on

tin

uo

, ~

10

me

si O

FF

mo

de

3 –

5 a

nn

i (d

ipe

nd

en

tem

en

te

da

ll’u

tili

zzo

qu

oti

dia

no

)

Dosimetri commerciali Capitolo 2

35

La Tabella 2.3 riassume i principali vantaggi e svantaggi nell’impiego di sistemi

dosimetrici attivi e passivi.

Tabella 2.3

Schema riassuntivo sui vantaggi e svantaggi di dosimetri attivi e passivi

Vantaggi Svantaggi

Dosimetri

passivi

Facilmente gestibili in termini

di posizionamento

Determinazione non real time

della dose

Tempi di risposta lunghi (giorni)

Misura e lettura separati

Forniscono una misura di dose

integrale

Dosimetri

attivi

Determinazione real time della

dose

Possibilità di definizione di

opportuni livelli di intervento

Più efficace pianificazione

delle procedure di RI

Prestazioni inferiori con i raggi

X utilizzati nelle procedure

Energy range inferiore

Risposta più scarsa

2.3 Il progetto RAPID

Il progetto RAPID (Real Time Active Pixel Dosimetry) nasce da una collaborazione tra

l’Istituto Nazionale di Fisica Nucleare (INFN) di Perugia, l’Università degli Studi di

Perugia, il Servizio di Fisica Sanitaria dell’ASL3 dell’Umbria presso l’Ospedale di Foligno

e il Servizio di Fisica Sanitaria dell’ASL1 dell’Umbria presso l’Ospedale di Città di

Castello. Obiettivo del progetto è lo sviluppo di un nuovo approccio per effettuare il

monitoraggio degli operatori attraverso l’uso di rivelatori a matrice di pixel attivi (Active

Pixel Sensors, APS), che consenta essenzialmente di:

− effettuare un monitoraggio in tempo reale della dose assorbita dagli operatori;

− creare un archivio remoto delle dosi assorbite da ciascun operatore per ottimizzare la

pianificazione delle procedure e minimizzare le code, contribuendo ad una gestione più

efficace del lavoro.

La possibilità di comunicare il dato dosimetrico in tempo reale, infatti, favorisce una

Dosimetri commerciali Capitolo 2

36

maggior consapevolezza dell’esposizione a radiazioni ionizzanti e, conoscendo

l'esposizione, si potrà agire, istante per istante, su tutte le variabili che determinano la dose

finale, come modalità di acquisizione (pulsata, continua, alta o bassa risoluzione), utilizzo

degli ingrandimenti, posizione del rivelatore d’immagine, angolazione del fascio

radiogeno, distanza dal paziente. L’attività di sorveglianza radioprotezionistica risulta in tal

modo nettamente agevolata, poiché la conoscenza del dato dosimetrico permette di

intervenire immediatamente nel caso di superamento dei limiti di esposizione

dell'operatore. L’idea è inoltre che, fornendo dati già in formato digitale, la gestione degli

stessi risulta notevolmente semplificata, con l’ulteriore possibilità di creare database per