Memoria Estatica

description

Transcript of Memoria Estatica

MEMORIA ESTATICA

NDICE

1. INTRODUCCIN.

1. MODO DE OPERACIN DE UNA SRAM.

1. TECNOLOGA DE FABRICACIN.

1. TEMPORIZACIN DE LA RAM ESTTICA.

1. APLICACIONES DE LA RAM ESTTICA.

1. CONCLUSIN.

1. BIBLIOGRAFA.

INTRODUCCIN.

En este trabajo investigaremos acerca de las memorias RAM estticas (SRAM), la cual es un tipo de memoria basada en semiconductores que, a diferencia de la memoria DRAM, es capaz de mantener los datos (mientras est alimentada) sin necesidad de circuito de refresco (no se descargan). Sin embargo, s son memorias voltiles, es decir que pierden la informacin si se les interrumpe la alimentacin elctrica.

Entre los tipos de SRAM se encuentran:

SRAM no voltiles, que presentan un funcionamiento estndar SRAM, con la salvedad de que guardan los datos cuando se interrumpe la alimentacin elctrica, salvaguardando informacin crtica. Se utilizan en situaciones donde la conservacin de los datos es crucial y el uso de bateras no es posible.

Se encuentran tambin las SRAM asncronas que estn disponibles en tamaos desde 4Kb hasta 32Mb. Con un tiempo rpido de acceso, son adecuadas para el uso en equipos de comunicaciones, como switches, routers, telfonos IP, tarjetas DSLAM, y en electrnica de automocin.

Tambin se encuentran por tipo de transistor que se subdividen en Transistor Bipolar de Unin o BJT (de tipo TTL o ECL), muy rpidos, pero con un consumo muy alto. Y los MOSFET (de tipo CMOS), de consumo reducido y muy utilizado actualmente.

Por ltimo estn los que son por funcin *asncronas que son independientes de la frecuencia de reloj. Y sncronas donde todas las operaciones son controladas por el reloj del sistema.

MODO DE OPERACIN DE UNA SRAM.

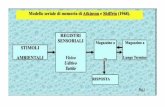

Una memoria SRAM tiene tres estados distintos de operacin: standby, en el cual el circuito est en reposo, reading o lectura, durante el cual los datos son ledos desde la memoria, y writting o escritura, durante el cual se actualizan los datos almacenados en la memoria.

1. Reposo: Si bus de control (WL) no est activado, los transistores de acceso M5 y M6 desconectan la celda de los buses de datos. Los dos biestables formados por M1 M4 mantendrn los datos almacenados mientras dure la alimentacin elctrica.

1. Lectura: Asumimos que el contenido de la memoria es 1, y est almacenado en Q. El ciclo de lectura comienza cargando los buses de datos con el 1 lgico, y luego activa WL y los transistores de control. A continuacin, los valores almacenados en Q y Q se transfieren a los buses de datos, dejando BL en su valor previo, y ajustando BL a travs de M1 y M5 al 0 lgico. En el caso que el dato contenido en la memoria fuera 0, se produce el efecto contrario: BL ser ajustado a 1 y BL a 0.

1. Escritura: El ciclo de escritura se inicia aplicando el valor a escribir en el bus de datos. Si queremos escribir un 0, ajustaremos BL to 1 y BL a 0, mientras que para un 1, basta con invertir los valores de los buses. Una vez hecho esto, se activa el bus WL, y el dato queda almacenado.

TECNOLOGA DE FABRICACIN.

Hablar de evolucin en las SRAM es hablar de las distintas estrategias seguidas para aumentar su velocidad y tamao siendo todava competitivas en precio con las RAM dinmicas. Cada vez se piden ms prestaciones de las memorias RAM estticas en todos sus dominios de aplicacin: como memoria cach, en el diseo de subsistemas grficos y en equipos de comunicacin de alta velocidad, donde todava hay diferencias entre la velocidad a la que el procesador necesita acceder a los datos y la velocidad intrnseca a la tecnologa y arquitectura de los circuitos SRAM que sirven a ese procesador.

Celdas RAM Estticas (SRAM) en Tecnologa Bipolar.

Ya hemos disco que las celdas RAM son biestables simplificados al mximo para aumentar la densidad de integracin con las facilidades adicionales para permitir la organizacin expuesta en el apartado anterior, es decir el direccionamiento, la lectura y la escritura. La funcin que realizaba el pulso de reloj en biestable R-S sincronizado a nivel la realiza aqu la lnea de seleccin de bit que facilita la entrada y/o salida de datos slo en la celda direccionada. Estas celdas se pueden realizar en tecnologas bipolares, MOS, CMOS y BiCMOS. Cuando la velocidad es el parmetro dominante se elige bipolar o BiCMOS y cuando interesa aumentar la capacidad se elige CMOS.

La figura 11.9 muestra el esquema de una celda bipolar realizada mediante dos transistores multiemisor. Sobre la estructura mnima de dos inversores realimentados (biestables), se superponen dos nuevos emisores para conectar las lneas de bit y se utiliza el circuito de polarizacin para seleccionar la celda en la que se quiere leer o escribir. Para ello, los emisores E1 y E2 se apoyan sobre el pulso de seleccin de celda, lo que hace que su valor cambie de 0.3V a 3V.

Elegimos el convenio de decir que la celda almacena un 1 cuan el transistor Q1 est conduciendo (Q2 al corte) y un 0 cuando Q2 est conduciendo (Q1 al corte). Por consiguiente, el emisor adicional de Q1 (E1) est conectado a la lnea de escritura de un 1 y el emisor adicional de Q2 (E2), a la lnea de escritura de un cero. Estas lneas van a otras muchas celdas pero slo operan sobre la celda que est seleccionada. Finalmente, e resultado de la lectura aparece sobre un amplificador diferencial que conecta la lneas de lectura de 1 y lectura de 0. En su mnima expresin, este sensor del estado se limita a dos resistencias, R3, conectadas entre las lneas e lectura y una tensin fija de 1.5 voltios. La figura 11.10 muestra el cronograma de la lnea de palabra y de las lneas de bit con los valores correspondientes en los intervalos de lectura y escritura de 1 y 0.

Las celdas SRAM en tecnologa bipolar tienen su campo natural de aplicacin en el diseo de las memorias cach de computadores de altas prestaciones en los que la velocidad es el parmetro esencial (tiempos de ciclo inferiores a 5ns).

Celdas RAM Estticas (SRAM) en Tecnologa MOS.

La idea bsica del diseo de celdas MOS estticas es la misma que en el caso bipolar. Partimos de un biestable MOS con dos inversores acoplados (Q1-Q3 y Q2-Q4) y le aadimos otros dos (Q5 y Q6) para las operaciones de seleccin, lectura y escritura. La figura 11.12 muestra el circuito correspondiente para esta celda de 6 transistores NMOS de realce.

Supongamos al igual que en el caso bipolar que la celda almacena un 1 cuando Q1 est en conduccin y Q2 en corte y viceversa en el caso de almacenar un 0. Cuando la celda no est direccionada est aislada del resto de la memoria porque los transistores Q5 y Q6 son puertas de transferencia abiertas (muy alta impedancia) debido a la polarizacin que reciben a travs de la lnea WL procedente del decodificador de direcciones. Para leer el contenido de la celda se activan sus puertas de transmisin poniendo VDD = 12 V en WL, con lo que Q5 y Q6 conducen y transmiten el potencial del punto A (punto de 0) a la lnea de datos correspondientes (BL negado).

Anlogamente, el potencial del punto B (punto de 1), se transmite a BL y el amplificador diferencial de lectura extrae el dato. Obsrvese que la celda es totalmente simtrica y que slo el convenio inicial (1 significa Q2 en conduccin) y el etiquetado de las lneas de datos (BL es la lnea de 1), permiten la distincin. Cuando la celda contena un 1, al final de la operacin de lectura aparecen 12 V en BL y 0 Ven BL negado. Cuando tena un 0, aparece 0V en BL y 12V en BL negado.

Para escribir en la celda se comienza direccionndola mediante un pulso positivo en WL, como en el caso anterior. Esto abre de nuevo las puertas de transmisin Q5 y Q6 y permite conmutar el biestable. Para escribir un 1 se mantiene BL en 12V y se baja la tensin de BL negado a 0V .Esto hace conducir a Q1 a travs de Q6 (si es que estaba cortado), quedando el drenador de Q1 (punto A de la figura 11.12) a 0V, el 1 lgico queda almacenado en la celda dado que los transistores Q5 y Q6 pasan de nuevo al estado de corte presentando alta impedancia y dejando a la celda aislada.

TEMPORIZACIN DE LA RAM ESTTICA.

Los CI's de la RAM son los que ms frecuentemente se utilizan como la memoria interna de una computadora. La CPU (unidad central de procesamiento) efecta en forma continua operaciones de lectura y escritura en su memoria a muy alta velocidad determinada por las limitaciones de la CPU. Los circuitos de memoria que se conectan con la CPU tienen que ser lo suficientemente rpidos para responder a los comandos de lectura y escritura de la CPU, por lo que un diseador de computadoras tiene que interesarse en las diversas caractersticas de temporizacin de las RAMs.

Observe que no todas las RAMs tienen las mismas caractersticas de temporizacin pero muchas de ellas son similares de manera que utilizaremos un conjunto de caractersticas comunes con fines ilustrativos. La nomenclatura de los diferentes parmetros de temporizacin variar de un fabricante a otro, pero el significado de cada parmetro es, por lo general, fcil de determinar a partir de los diagramas de temporizacin de la memoria en las hojas de especificaciones de la RAM. La figura 11.28 muestra los diagramas de temporizacin de un ciclo completo de lectura y de uno de escritura de un circuito RAM comn.APLICACIONES DE LA RAM ESTTICA.

Las caractersticas de la memoria SRAM es que son ms cara, pero ms rpida y con un menor consumo (especialmente en reposo) que la memoria DRAM. Por tanto es utilizada, cuando es necesario disponer de un mejor tiempo de acceso, o un consumo reducido, o ambos. Debido a su compleja estructura interna, es menos densa que DRAM, y por lo tanto no es utilizada cuando es necesaria una alta capacidad de datos, como por ejemplo en la memoria principal de los ordenadores personales.

Otras caractersticas de la SRAM son la Frecuencia de reloj y el consumo elctrico, por lo cual estas caractersticas varan dependiendo de la frecuencia con la cual se accede a la misma; puede llegar a tener un consumo similar a DRAM cuando es usada en alta frecuencia, y algunos circuitos integrados pueden consumir varios vatios durante su funcionamiento. Por otra parte, las SRAM utilizadas con una frecuencia baja, tienen un consumo muy bajo, del orden de micro-vatios. Los usos de las SRAM pueden ser:1. como producto de propsito general: 0. con interfaces asncronas como chips 32Kx8 de 28 pines (nombrados XXC256), y productos similares que ofrecen transferencias de hasta 16Mbit por chip. 0. con interfaces sncronas, principalmente como caches y otras aplicaciones que requieran transferencias rpidas, de hasta 18Mbit por chip. 0.

1. integrados en chip: 1. como memoria RAM o de cache en micro-controladores. 1. como cache primaria en microcontroladores. 1. para almacenar los registros de microprocesadores. 1. en circuitos integrados. 1. en FPGAs y CPLDs.Usos integrados en productosLas SRAM se utilizan en sistemas cientficos e industriales, electrnica del automvil, y similares. Tambin se pueden encontrar en prcticamente todos los productos de uso cotidiano que implementen una interfaz electrnica de usuario.Tambin podemos encontrar memorias SRAM en los ordenadores personales, estaciones de trabajo, routers y la totalidad de perifricos de los mismos.

Uso de aficionadosLos aficionados a la electrnica prefieren las memorias SRAM debido a su sencilla interfaz, ya que es mucho ms fcil trabajar con SRAM que con DRAM, al no existir ciclos de refresco, y poder acceder directamente a los buses de direccin y de datos en lugar de tener que utilizar multiplexores. Adems, las SRAM solo necesitan tres buses de control: Chip Enable (CE), Write Enable (WE), y Output Enable (OE). En el caso de las SRAM sncronas, tendremos adems la seal de reloj (CLK).

EJEMPLO PRCTICOCircuito actual SRAMUn ejemplo de un CI SRAM actual es la cmos MCM6264C, que es una memoria RAM de 8K x 8 con ciclos de lectura y escritura de 12 ns y un consumo de potencia de slo 100mW en el estado de espera. En la figura 11.29 se muestra el smbolo lgico correspondiente para este CL. Observe que es circuito tiene 13 entradas para direccionamiento dado que 12^13- 8192 - 8K, y ocho lnea de E/S para datos. Las cuatro entradas de control determinan el modo de operacin del circuito de acuerdo con la tabla que tambin aparece en la figura.La entrada WE es igual a la entrada R / W que hemos utilizados hasta este momento. Un nivel bajo en la entrada WE har que se escriban los datos dentro de la RAM siempre y cuando el circuito haya sido seleccionado ; ambas entradas de seleccin de microcircuito est activas. Observe la forma en que se utiliza el smbolo & para denotar que ambas entradas tienen que estar activas. Un nivel ALTO aplicado en WE produce la operacin de lectura siempre que el dispositivo se encuentre seleccionado y los buffers de salida estn habilitados por OE = BAJO. Cuando el dispositivo deja de estar seleccionando, para al estado de bajo consumo de potencia en el que ninguna de las dems entradas tiene efecto sobre l.

CONCLUSIN.

En este trabajo les comentamos sobre la memoria SRAM, cuya Siglas son Static Random Access Memory, es un tipo de memoria que es ms rpida y fiable que la ms comn DRAM (Dynamic RAM). El trmino esttica viene derivado del hecho que necesita ser refrescada menos veces que la RAM dinmica. Los chips de RAM esttica tienen tiempos de acceso del orden de 10 a 30 nanosegundos, mientras que las RAM dinmicas estn por encima de 30, y las memorias bipolares y ECL se encuentran por debajo de 10 nanosegundos.

Un bit de RAM esttica se construye con un --- como circuito flip-flop que permite que la corriente fluya de un lado a otro basndose en cul de los dos transistores es activado. Las RAM estticas no precisan de circuitera de refresco como sucede con las RAMs dinmicas, pero precisan ms espacio y usan mas energa. La SRAM, debido a su alta velocidad, es usada como memoria cach.

Les comentamos tambin sobre los tipos de SRAM que existen de los cuales son SRAM no voltiles, las SRAM asncronas, los que son por tipo de transistor que se subdividen en Transistor Bipolar de Unin o BJT y los MOSFET y por ltimo los SRAM por funcin asncrona y sncrona.

Luego les comentamos sobre el modo de operacin de la memoria esttica, en la cual consista en 3 procesos que eran reposo, lectura y escritura.BIBLIOGRAFA.

1. Libro de sistemas Digitales Principios y AplicacionesRobert Tocci octava edicin

1. http://es.wikipedia.org/wiki/SRAM

1. http://www.taringa.net/posts/info/1968746/Tipos-de-memoria-ram-de-una-PC___.html