L’ARCHITETTURA DEI CALCOLATORI - CNRstaff.icar.cnr.it/ffolino/teaching/2009/Fondamenti... ·...

Transcript of L’ARCHITETTURA DEI CALCOLATORI - CNRstaff.icar.cnr.it/ffolino/teaching/2009/Fondamenti... ·...

-

L’ARCHITETTURA DEI CALCOLATORI

Il processoreLa memoria centraleLa memoria di massaLe periferiche di I/O

-

11/10/2007

2

Caratteristiche dell’architettura

Flessibilitàadatta a svolgere diverse tipologie di compiti

Modularitàogni componente ha una funzione specifica

Scalabilitàogni componente può essere sostituito con uno equivalente

Standardizzazionecomponenti facilmente sostituibili in caso di malfunzionamento

Riduzione dei costigrazie alla produzione su larga scala

Semplicitàdi installazione ed esercizio del sistema

-

11/10/2007

3

1.Elaborazione

Interconnessione

2.Memorizzazione

3.Comunicazione(interfaccia)

Unità Centrale di Elaborazione

MemoriaElettronica

MemoriaMagnetica

Il calcolatore:modello architetturale

Periferiche

Collegamenti(BUS/Cavi)

-

11/10/2007

4

Hardware: architettura

L’architettura dell’hardware di un calcolatore reale è molto complessaLa macchina di Von Neumann è un modello semplificato dei calcolatori moderni

Von Neumann progettò, verso il 1945, il primo calcolatore con programmi memorizzabili anziché codificati mediante cavi e interruttori

-

11/10/2007

5

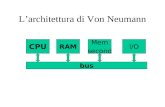

Macchina di Von NeumannE’ composta da 4 tipologie di componenti funzionali:

unità centrale di elaborazione (CPU)esegue istruzioni per l’elaborazione dei datisvolge anche funzioni di controllo

memoria centralememorizza e fornisce l’accesso a dati e programmi

interfacce di ingresso e uscitacomponenti di collegamento con le periferiche del calcolatore

bussvolge la funzionalità di trasferimento di dati e di informazioni di controllo tra le varie componenti funzionali

-

11/10/2007

6

Macchina di Von Neumann

-

11/10/20077

Dispositivi di Input

Tastiera Mouse

Joystick

trackball Touch pad

Penna ottica Scanner

Webcam

Fotocam. Dig.

Microfono

Schermi touch screen

Tavoletta grafica

-

11/10/20078

Dispositivi di Output

Monitor

Cuffie

Plotter

Stampante

Casse acustiche Videoproiettore

-

11/10/2007

9

Caratteristiche del collegamento a BUS

Semplicitàun’unica linea di connessione costi ridotti di produzione

Estendibilitàaggiunta di nuovi dispositivi molto semplice

Standardizzabilitàregole per la comunicazione da parte di dispositivi diversi

Lentezzautilizzo in mutua esclusione del bus

Limitatà capacitàal crescere del numero di dispositivi collegati

Sovraccarico del processore (CPU)perchè funge da master sul controllo del bus

-

11/10/2007 10

Bus di sistemaInterconnette CPU, memorie ed interfacce verso dispositiviperiferici (I/O, memoria di massa, ...)Collega due unità funzionali alla volta

una trasmette e l’altra riceveIl trasferimento dei dati avviene sotto il controllo della CPU

-

11/10/2007

11

Bus di sistemaIl bus trasporta dati, indirizzi e comandi Componenti del bus (sottogruppi di linee):

Bus dati (data bus) Bus indirizzi (address bus) Bus comandi (command bus)

Bus dati (data bus) Serve per trasferire dati

tra la memoria centrale ed il registro dati (MDR) della CPUtra periferiche e CPU (o memoria centrale)

Bidirezionale

-

11/10/2007

12

Bus di sistema

Bus indirizzi (address bus)

Serve per trasmettere il contenuto del registro indirizzi (MAR) alla memoria (o ad una periferica)

si seleziona una cella per successive operazioni di lettura o scrittura

UnidirezionaleBus comandi (command bus)

Serve per inviare comandi verso la memoria (e.g.: lettura o scrittura) o verso una periferica (es. stampa verso la stampante / interfaccia)

Unidirezionale

-

11/10/2007

13

Interfacce di I/O e bus

-

UNITÀ CENTRALE DI ELABORAZIONECPU

-

11/10/2007

15

Organizzazione tipica di un calcolatore “bus oriented”

CPU Memoriacentrale

Bus

Unità dicontrollo

Unitàaritmetico

logica (ALU)Registri

CPU

Terminale

Unitàdisco

Stampante

Dispositivi di I/O

-

11/10/2007

16

Tre tipologie di istruzioni

Istruzioni aritmetico-logiche (Elaborazione dati)Somma, Sottrazione, Divisione, …And, Or, Xor, …Maggiore, Minore, Uguale, Minore o uguale, …

Controllo del flusso delle istruzioniSequenzaSelezione semplice, a due vie, a n vie, …Ciclo a condizione iniziale, ciclo a condizione finale, …

Trasferimento di informazioneTrasferimento dati e istruzioni tra CPU e memoriaTrasferimento dati e istruzioni tra CPU e dispositivi di ingresso/uscita (attraverso le relative interfacce)

-

11/10/2007

17

Elementi di una CPU

Unità di controlloSvolge funzioni di controllo, decide quali istruzioni eseguire.

Unità aritmetico–logicaesegue le operazioni aritmetico-logiche (+,-,etc. , confronto).

Registrimemoria ad alta velocità usata per risultati temporanei e informazioni di controllo;il valore massimo memorizzabile in un registro è determinato dalle dimensioni del registro;esistono registri di uso generico e registri specifici:

Program Counter (PC) – qual è l’istruzione successiva;Instruction Register (IR) – istruzione in corso d’esecuzione;…

-

11/10/2007

18

A B

Registri

A+B

Come lavora la ALURegistri di ingresso dell’ALU

Bus di ingresso all’ALU

Registro di

uscita dell’AL

U

ALU

A+B

A

B

-

11/10/2007

20

Registri (1/2)

Un microprocessore contiene un numero limitato di celle di memoria (registri) con scopi specifici

registro contatore delle istruzioni (PC, program counter)indirizzo della prossima istruzione da eseguire

registro delle istruzioni (IR, instruction register)istruzione che deve essere eseguita (codificata)

parola di stato del processore (PSW)contiene informazioni, opportunamente codificate, circa l’esito dell’ultima istruzione che è stata eseguita

-

11/10/2007

21

Registri (2/2)

registro indirizzi della memoria (MAR)indirizzo della cella di memoria che deve essere acceduta o memorizzata

registro dati della memoria (MDR)dato che è stato acceduto o che deve essere memorizzato

registri generaliper memorizzare gli operandi ed il risultato di una operazione

-

11/10/2007

22

Esecuzione delle istruzioni

Ciclo Fetch–Decode–Execute(leggi–decodifica–esegui)

1. Prendi l’istruzione corrente dalla memoria e mettila nel registro istruzioni (IR).

2. Incrementa il program counter (PC) in modo che contenga l’indirizzo dell’istruzione successiva.

3. Determina il tipo dell’istruzione corrente (decodifica).4. Se l’istruzione usa una parola in memoria, determina dove si trova.5. Carica la parola, se necessario, in un registro della CPU.6. Esegui l’istruzione.7. Torna al punto 1 e inizia a eseguire l’istruzione successiva.

-

11/10/2007

23

Ciclo Fetch–Decode–Execute

Fetch

Decode

Execute

-

11/10/2007

24

CPU

In grado di eseguire solo istruzioni codificate in linguaggio macchina

Ciclo Fetch – Decode - Execute1. Prendi l’istruzione corrente dalla memoria e

mettila nel registro istruzioni (IR) (fetch)

2. Incrementa il Program Counter (PC) in modo che contenga l’indirizzo dell’istruzione successiva

3. Determina il tipo di istruzione da eseguire (decode)

4. Se l’istruzione necessita di un dato in memoria determina dove si trova e caricalo in un registro della CPU

5. Esegui l’istruzione (execute)

6. Torna al punto 1 e opera sull’istruzione successiva

-

11/10/2007

Introduzione all'Informatica

25

Evoluzione delle CPU

CPU Anno Frequenza(MHz)

Dimensione registri / bus

dati

Numero ditransistor

8086 1978 4.77 — 12 8 / 16 29 000

80286 1982 8 — 16 16 / 16 134 000

80386 1986 16 — 33 32 / 32 275 000

80386 SX 1988 16 — 33 32 / 16 275 000

80486 1989 33 — 50 32 / 32 1 200 000

Pentium 1993 60 — 200 32 / 64 3 100 000

Pentium II 1997 233 — 400 32 / 64 7 500 000

Pentium III 1999 450 — 1133 32 / 64 24 000 000

Pentium 4 2000 1600 — 2000 32 / 64 42 000 000

-

11/10/2007

26

Legge di Moore

Osservazione fatta da Gordon Moore nel 1965:

il numero dei transistor per cm2

raddoppia ogni X mesi

In origine X era 12. Correzioni successive hanno portato a fissare X=18. Questo vuol dire che c’è un incremento di circa il 60% all’anno.

-

11/10/2007

27

# Transistor [CPU Intel]

-

11/10/2007

28

Legge di Moore e progresso

Il progresso della tecnologia provoca un aumento del numero di transistorper cm2 e quindi per chip.

Un maggior numero di transistor per chip permette di produrre prodotti migliori (sia in termini di prestazioni che di funzionalità) a prezzi ridotti.

I prezzi bassi stimolano la nascita di nuove applicazioni (e.g. non si fanno video game per computer da milioni di $).

Nuove applicazioni aprono nuovi mercati e fanno nascere nuove aziende.

L’esistenza di tante aziende fa crescere la competitività che, a sua volta, stimola il progresso della tecnologia e lo sviluppo di nuove tecnologie.

-

LA MEMORIA