ECIMATORE DIGITALE A EGA ERTZ PER A/D...

Transcript of ECIMATORE DIGITALE A EGA ERTZ PER A/D...

-

POLITECNICO DI MILANO

Dipartimento di Elettronica e Informazione

DECIMATORE DIGITALE A 200 MEGAHERTZPER A/D SIGMA-DELTA :

DALLARCHITETTURA AL LAYOUT

Relatore: Prof. Andrea LACAITACorrelatore : Ing. Carlo SAMORI

Tesi di laurea di:Alfio ZANCHIMatricola 603716

Ingegneria ElettronicaOrientamento Segnali e Sistemi Elettronici

ANNO ACCADEMICO 1994/95

-

Indice

Introduzione ..................................................................................... I

Capitolo 1 - La catena di conversione A/D Sigma-Deltaed il ruolo del decimatore ........................................ 1

1.1 Limportanza della conversione A/D e D/A 11.2 Un metodo ideale per i sistemi misti: la conversione Sigma-Delta 21.3 Campionamento e conversione ADC di tipo convenzionale 41.4 Sovracampionamento: lo scambio risoluzione-velocit 61.5 Dal convertitore tracking al Sigma-Delta del 1 ordine 81.6 Comportamento nei tempi del modulatore Sigma-Delta:

una simulazione preliminare 121.7 Comportamento in frequenza del modulatore Sigma-Delta:

analisi del rapporto Segnale/Rumore 161.8 Pattern noise per modulatori del 1 ordine 181.9 Il modulatore Sigma-Delta del 2 ordine 231.10 Evidenza spettrale delle propriet di shaping sul rumore 261.11 Cenni alla realizzazione circuitale 281.12 Decimazione del segnale digitale sovracampionato 291.13 Scelta dellordine e del fattore di decimazione 321.14 Numero di bit in uscita dal decimatore FIR 361.15 Simulazioni dellintera catena A/D Sigma-Delta 40

Capitolo 2 - La scelta dellarchitettura a blocchi del filtro ........... 44

2.1 Implementazione canonica di un filtro FIR 442.2 Realizzazione in Forma DIRETTA 462.3 Realizzazione in Forma RICORSIVA 502.4 Sezione IIR del decimatore: le aritmetiche modulari 532.5 Il problema dei cicli limite 572.6 Sezione FIR del decimatore: stato iniziale e latenza 602.7 Simulazione e scelta finale 612.8 Strutture di decimazione alternative 632.9 Confronto tra filtraggio eseguito direttamente e mediante FFT 66

Capitolo 3 - Dallarchitettura alla logica: tecniche adottate perlaritmetica digitale ................................................ 69

3.1 Uso dei sommatori nel circuito 693.2 Parte IIR : Limite di Winograd per la velocit dei sommatori 703.3 Parte IIR : Ripple carry e full-adder 70

-

3.4 Parte IIR : Carry look-ahead (CLA) 763.5 Parte IIR : Carry select, o somma condizionale 823.6 Parte IIR : Carry select + Carry look-ahead 843.7 Parte IIR : Carry save (applicazione del pipe-line alla somma binaria) 863.8 Parte IIR : Altre tecniche alternative di somma 893.9 Parte IIR : Progetto a livello logico delle tecniche individuate 943.10 Parte FIR : Sottrattore dinamico a Manchester carry chain 1023.11 Parte FIR : Sottrattori veloci e risparmio di latenza 1063.12 Uso dei registri/ritardi nel circuito 1073.13 Parte IIR : Corsa critica e latch a NPTC 1083.14 Parte IIR : Tecnica C2MOS e memorizzazione dinamica 1113.15 Parte IIR : Tecnica NORA 1143.16 Parte IIR : Tecnica TSPC 1153.17 Parte IIR : Scelte di temporizzazione finali 1173.18 Parte FIR : Registri 1183.19 Parte Intermedia : Divisore di frequenza 4:1 118

Capitolo 4 - Dalla logica circuitale allo schematico a transistori:problemi e soluzioni ............................................. 120

4.1 Uno sguardo alla tecnologia a disposizione: BiCMOS 1204.2 Dimensionamento dellinvertitore digitale minimo 1264.3 Ritardo del buffer minimo digitale 1304.4 Parte IIR : Implementazione a transistori delle singole porte logiche 1314.5 Parte IIR : Ottimizzazione dei singoli blocchi carry-select da 2 bit 1414.6 Parte IIR : Progetto CMOS della rete di look-ahead del sommatore 1464.7 Parte IIR : Progetto BiCMOS a Wired-OR della rete CLA 1504.8 Parte IIR : Ottimizzazione dei registri a latch 1594.9 Parte IIR : Tentativo useful clock skew 1714.10 Parte IIR : Introduzione del carry save/pipe-line 1814.11 Parte IIR : Modifiche finali a sommatori e registri 1844.12 Parte IIR : Simulazioni conclusive 1914.13 Parte FIR : Sottrattori a Manchester carry chain semplice 1964.14 Parte FIR : Manchester carry chain rigenerata 2004.15 Parte FIR : Simulazioni conclusive della soluzione Manchester 2054.16 Parte FIR : Sottrattori veloci e calo di latenza 2094.17 Parte Intermedia : Tecniche di distribuzione del sincronismo 2124.18 Parte Intermedia : Divisore di frequenza

e sincronismo di sottocampionamento 2154.19 Consumo di energia : alimentazioni e clock 2214.20 Stime delloccupazione di area 2264.21 Il problema della temperatura 2274.22 Ultima modifica circuitale : tecnica dvide et mpera 229

-

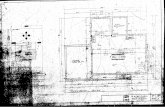

Capitolo 5 - Floorplanning e layout in tecnologia BiCMOS .......... 232

5.1 Obiettivi principali del floorplanning 2325.2 Parte IIR : Geometria con percorso dei dati rettilineo 2335.3 Parte IIR : Geometrie con percorso dei dati ripiegtao 2355.4 Parte IIR : Geometria mista e problemi di clock skew 2375.5 Parte FIR : Prosecuzione della geometria IIR precedente 2395.6 Parte IIR : Il floorplan delle singole porte logiche nei blocchi modulari 2415.7 Parte FIR : Floorplanning funzionale alla precarica 2445.8 Elementi fondamentali e parametri principali utili per il layout 2455.9 Design rules del processo BiCMOS 2495.10 Layout della sezione IIR: i blocchi unitari carry select 2515.11 Dimensionamento delle linee di alimentazione 2595.12 Distribuzione del clock 2625.13 Layout della sezione intermedia del filtro 2665.14 Layout della sezione FIR: sottrattori con celle a pitch minimo 2685.15 Layout della sezione FIR: i registri a pitch minimo 2705.16 Risultato finale e corrispondenza con le previsioni 2745.17 Fasi post-layout: estrazione del circuito , LVS e calcolo

di alcuni parametri caratteristici dei circuiti digitali 276

Capitolo 6 - Vettori di test e diverse verifiche di funzionamento .. 281

6.1 Uso di Matlab per il controllo delle sequenze binarie 2816.2 Simulazioni complete di casi critici 2846.3 Sintesi del macromodello di un modulatore Sigma-Delta del 2 ordine 2876.4 Schemi completi della catena di conversione A/D Sigma-Delta 2956.5 Simulazioni miste behavioural-circuitali della catena A/D 2986.6 Analisi di worst-case del filtro decimatore 3006.7 Condizioni di funzionamento consigliate 3056.8 Conclusioni e sviluppi futuri 306

Appendice 1 - Il simulatore TOSCA .............................................. 1

Appendice 2 - Listati Matlab per la simulazione dei decimatori .. 4

Appendice 3 - Sintesi della logica di riporto condizionalemediante mappe di Karnaugh ............................. 19

Bibliografia ...................................................................................... 24

Ringraziamenti ................................................................................ 29

-

Introduzione

I

Introduzione

Lo scopo del presente lavoro di tesi quello di progettare un filtro decimatore

da porre a valle di un modulatore del tipo Sigma-Delta. E noto infatti come la

conversione Analogico/Digitale eseguita mediante la tecnica di sovracampionamento

a Sigma-Delta sia efficiente nel rimuovere il rumore di quantizzazione dalla banda

base del segnale, ma richieda unintera catena DSP (Digital Signal Processing) per

scendere in frequenza sino al limite di Nyquist, e contestualmente aumentare il

numero di bit della rappresentazione digitale dei dati. In effetti, in letteratura si parla

propriamente di modulazione Sigma-Delta per la parte analogica, ma di conversione

A/D Sigma-Delta per il sistema completo.

Lambito applicativo a cui questo progetto si rivolge quello dellelaborazione

di segnali a frequenza video; tale locuzione usata, in questo contesto, per soli fini

indicativi e si riferisce in generale a segnali aventi uno spettro estendentesi fino a 4

MegaHertz. Ci ha implicato la realizzazione di un modulatore funzionante a 200

MegaHertz e con uscita a 2 bit, per ottenere una risoluzione finale superiore a 10 bit

per i segnali in banda; il primo stadio della cascata di decimazione dovr dunque

prelevare la sequenza binaria a 2 per 200 Megabit/secondo, ed estrarne una sequenza

di dati da 8 bit a 50 MegaHertz. Il risultato viene acquisito attraverso un

sottocampionamento, previo filtraggio passa-basso per evitare aliasing del rumore

nelle bande di interesse. Il tipo di elaborazione seguita a comb filter, o filtro a

pettine, che garantisce grande semplicit di implementazione ed efficace reiezione del

rumore di quantizzazione ad alta frequenza.

Il lavoro svolto si esplicato dapprima nellindividuazione dellarchitettura a

blocchi pi adeguata allo scopo; in un secondo tempo nella traduzione

dellarchitettura scelta in una configurazione circuitale a livello di porte logiche, con

particolare enfasi dedicata allottimizzazione, rispetto alla velocit, dellaritmetica

binaria utilizzata; in terza istanza, nel passaggio da tale logica alla sua realizzazione

mediante transistori; ed in ultimo luogo, nella trasposizione della rete di componenti

progettata nel layout fisico dei dispositivi, con attenzione particolare dedicata agli

aspetti di bassa occupazione di area e basso consumo di potenza.

-

Introduzione

II

La tecnologia elettronica a nostra disposizione per portare avanti il progetto di

tipo BiCMOS (Bipolar + CMOS), quindi il circuito digitale finale sar realizzato con

la prospettiva di terminare sul medesimo chip che allocher il modulatore Sigma-

Delta, gi preesistente come frutto di una tesi di dottorato. Le alimentazioni sono gi

fissate a 3.3 V, quindi si tratta di unapplicazione low-power; in effetti, il decimatore e

lintera catena di conversione devono consumare poco anche per non perturbare le

caratteristiche del circuito principale a cui renderanno servizio di front-end A/D. Va

chiarito subito, in questottica, come il progetto finale faccia uso di soli componenti

MOSFET evitando lutilizzo dei pi dissipativi ed ingombranti BJT.

Il segnale di sincronismo del sistema supposto giungere dallesterno, con

fronti simmetrici di salita e discesa di durata 0.3 nanosecondi e ciclo di lavoro pari al

50%; idem dicasi per le due linee binarie provenienti dal modulatore, gi pensate

sincronizzate con il clock. La fase di temporizzazione divisa per quattro, cio il fattore

di decimazione, va viceversa generata allinterno del circuito. Le otto uscite binarie

(byte) sono rese disponibili allesterno attraverso un registro finale non bufferizzato; il

progetto non si deve occupare inoltre dei problemi inerenti le sezioni di ingresso ed

uscita dei segnali (pad di connessione con limpaccamento, numero di connessioni per

le alimentazioni, etc.), essendo solo una parte di un chip completo.

La versione disponibile della tecnologia BiCMOS contempla la presenza di tre

livelli di metallo e di due tipologie di polisilicio; non consente la sovrapposizione dei

contatti (stacked contact); la minima lunghezza di canale di 0.7 m, mentre la

larghezza minima praticabile vale 2.2 m. Le tensioni di soglia valgono +0.816 V per

i transistori NMOS e 0.919 V per i PMOS; purtroppo non si ha a disposizione una

tecnologia con soglie scalate rispetto alla alimentazione in uso, che avrebbe fornito

invece componenti con soglie attorno a 0.5 V; la velocit del circuito risente

sicuramente di questa particolarit. Il transistore bipolare minimo realizzabile ha

inoltre unarea di emettitore di 3.5x3.5 m2.

I programmi di sviluppo dei circuiti integrati che sono stati utilizzati sono:

OPUSTM (della Cadence Design Systems, Inc.) per il disegno dei circuiti, sia a livello

dello schematico che del layout; ST-SPICE (della SGS-Thomson Microelectronics)

per la simulazione, ammessa per al solo livello circuitale e non anche a livello

-

Introduzione

III

behavioral; e Xelga (della Anacad Corp.) per lanalisi dei segnali prodotti dalle

simulazioni. Si segnala in questa sede la mancanza di un mezzo di simulazione a

livello astratto per le funzioni digitali, nonch di un analizzatore automatico dei

ritardi del circuito, che che avrebbero probabilmente consentito di migliorare il flusso

di progettazione. I mezzi di calcolo a nostra disposizione erano delle workstation Sun

SPARC10 e SPARC20.

La presente dissertazione scritta suddivisa in 6 capitoli, i cui contenuti sono

per sommi capi i seguenti:

1. Il primo capitolo tratta gli aspetti generali inerenti il problema della

conversione Analogico/Digitale, fornendo le principali definizioni utili per

comprendere il prosieguo dellanalisi del problema. Dalle strutture pi classiche di

A/D si passa gradualmente alle tecniche sovracampionate, sino al Sigma-Delta del

2 ordine; per questultimo si riconosce la necessit di una decimazione, e si

investigano le propriet spettrali che il fltro decimatore deve possedere, in

riferimento alla risoluzione desiderata alluscita della catena di conversione.

2. Nel secondo capitolo si analizzano diverse tipologie di schemi a blocchi in

grado di fornire le caratteristiche identificate del decimatore. Partendo da strutture di

filtraggio utilizzate in altri contesti, si giunge a proporre due soluzioni alternative

che vengono quindi confrontate con laiuto di simulazioni al calcolatore; particolare

enfasi dedicata allo studio delle aritmetiche binarie occorrenti per assicurare il

corretto funzionamento degli schemi individuati.

3. Il terzo capitolo contiene la descrizione delle fasi di passaggio

dallarchitettura funzionale del filtro ad una realizzazione dei singoli blocchi

mediante porte logiche, ad alto livello. Sono ivi esaminate alcune configurazioni di

porte atte allimplementazione di unaritmetica di somma veloce dei dati, a partire

dagli schemi pi semplici sino a soluzioni pi elaborate; inoltre viene trattata la

questione della sincronizzazione del sistema, e quindi della efficiente realizzazione

dei registri in esso contenuti.

4. Nel quarto capitolo, le tecniche ad alto livello scelte vengono finalmente

trasformate in circuiti a transistori e sottoposte a test di simulazione. La maggiore

importanza viene data alla sezione del filtro funzionante a 200 MHz: si presentano

schematici facenti uso della tecnologia BiCMOS, sia facendo ricorso ai soli

MOSFET che usando i transistor bipolari, ed applicando tecniche circuitali (un

-

Introduzione

IV

esempio: lo useful clock skew) di ottimizzazione rispetto alla velocit di

operazione. Seguono le descrizioni della rete di divisione e distribuzione del clock, e

della sezione di sottrazione dei dati funzionante a 50 MHz. Infine, si presentano i

risultati dellanalisi worst-case dellintero schema.

5. Il capitolo quinto dedicato allimplementazione fisica del circuito

progettato. Vengono discusse le problematiche afferenti al floor-planning

(disposizione ottima dei blocchi logicamente omogenei dei transistori) ed al layout

(progetto delle configurazioni geometriche di transistori e connessioni), e si

illustrano le soluzioni trovate con lausilio di immagini tratte dal circuito finale

disegnato.

6. Nel capitolo sesto si trova infine una breve descrizione dei metodi utilizzati

per verificare la correttezza del funzionamento del circuito, sia durante lo

svolgimento del progetto che in sede di test conclusivo.

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 1 -

Capitolo

La catena di conversione

A/D Sigma-Delta

ed il ruolo del decimatore

In questo capitolo si descrivono i principi fondamentali ed i comportamenti principali che

caratterizzano il funzionamento dei sistemi di conversione A/D di tipo Sigma-Delta.

Partendo dai metodi classici di conversione si definiscono i parametri atti a quantificarne

le propriet, per poi passare alle tecniche alternative sovracampionate, e giungere

allanalisi dei modulatori Sigma-Delta sino al 2 ordine. Compresa la necessit di porre

degli stadi di decimazione a valle del modulatore, si analizzano infine le prestazioni di

questi ultimi sia da un punto di vista teorico che fornendo simulazioni pi intuitive.

1.1 - L importanza della conversione A/D e D/A

Linteresse devoluto alle tecniche di conversione Analogico/Digitale e

Digitale/Analogico oggigiorno in continua ascesa; sono testimonianza di ci le numerose

realizzazioni di integrazione di sistemi misti, che contemplano cio la concomitante presenza

di elettronica binaria - digitale - e continua - analogica - sul medesimo die di silicio.

A supporto di questa affermazione si possono annoverare svariati esempi, in prima

istanza divisibili in due vaste categorie :

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 2 -

- i sistemi digitali presenti in blocchi a funzione essenzialmente analogica; tipico il caso

delle schede Smart-Power per attuatori, laddove si utilizzano dispositivi di potenza

pilotati da reti logiche anche complesse, con capacit di calcolo e di memoria per la

bufferizzazione di dati;

- i sistemi analogici presenti in blocchi a vocazione eminentemente digitale; e questo

forse il caso che pi frequentemente si incontra : basti pensare ai sottosistemi di driving

delle linee di dato e/o selezione in una memoria Flash-EPROM, oppure agli outlet dei

modem, e ancora pi in generale ad ogni sistema di interfaccia di una rete di

telecomunicazioni.

In effetti, la presenza onnipervasiva dei processori, con la loro facilit di controllo da

parte dellutente umano e la flessibilit di gestione delle loro risorse, grazie alla

programmabilit che ne rappresenta la caratteristica peculiare, gi una risposta molto

appetibile a svariati problemi che la moderna elettronica deve affrontare. Risolti quei

problemi, tende inoltre a farne sorgere di nuovi, in una continua spinta verso laumento delle

velocit, la riduzione delle aree, la moltiplicazione delle funzioni e la minimizzazione delle

potenze dissipate dal singolo chip.

Questo proficuo processo di fusione delle due branche dellelettronica pone, di

conseguenza, richieste sempre pi stringenti ai progettisti dellinterfaccia tra i due blocchi: il

convertitore, sia esso A/D oppure D/A. In questa tesi di laurea sar affrontato soltanto il tema

della trasformazione A/D (Analogico Digitale) dei segnali in arrivo; purtuttavia bene

aver presente che la filosofia Sigma-Delta trova applicazione anche nelloperazione inversa, di

passaggio D/A.

1.2 - Un metodo ideale per i sistemi misti : la conversione Sigma-Delta

La maggioranza degli schemi di conversione A/D fa riferimento a circuiti che, tra le

possibili scelte di realizzazione, privilegiano quelle che si appoggiano pi a tecniche

analogiche che non a tecniche digitali.

I convertitori a rampa (semplice, doppia, multirampa, ...) si basano sulla precisione e

sulla riproducibilit di una rampa di tensione; il dispositivo di conteggio dei cicli di clock che

intercorrono tra i segnali di sincronismo forniti dai comparatori riveste importanza marginale,

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 3 -

rispetto alla rete di integrazione della corrente continua che dar la rampa. I convertitori ad

approssimazioni successive (sia che lavorino in una fase sola, oppure con raffinamento

progressivo della stima binaria presentata in uscita) hanno bisogno di precisi comparatori e di

un buon DAC; la cosiddetta pesiera, logica di controllo che scala progressivamente i bit,

non certo una rete concettualmente critica, data anche la relativa lentezza del dispositivo.

Infine, gli ADC di tipo Flash hanno s una logica di priority encoding che deve essere veloce,

ma sono ancora pi difficili da integrare sia la rete resistiva di partizione della tensione di

fondo-scala che la batteria di comparatori, il cui numero esplode esponenzialmente con il

numero di bit.

Tutto questo tende a sposarsi poco felicemente con le attuali risorse messe a

disposizione dalle tecnologie utilizzate per implementare i sistemi misti. Naturalmente infatti,

data la complessit dei compiti che tali circuiti saranno chiamati a svolgere, la spinta

tecnologica massima verso standard di tipo VLSI (Very Large Scale Integration); solo cos

unintera logica di controllo microprogrammata pu adattarsi a stare sul singolo chip di

silicio. Ma le applicazioni VLSI ottimizzano i parametri legati alla densit dei transistori, a

netto discapito della precisione dei dispositivi medesimi. Solo a titolo di esempio, sappiamo

dalla consolidata teoria del progetto degli amplificatori operazionali quanto sia utile

aumentare le dimensioni dei componenti di ingresso per ridurre lincidenza della dispersione

delle dimensioni fisiche ottenute realmente, che pesano direttamente sui valori degli errori in

continua; in un ambito di processo pensato per produrre milioni di transistori di dimensioni

submicrometriche, questo bisogno di precisione quanto meno mal soddisfatto, e snatura

lintenzione originaria che ha portato a sviluppare il processo medesimo.

Molto meglio sarebbe poter barattare precisione con velocit di elaborazione,

possibilmente di un segnale gi digitalizzato; il che esattamente quel che accade nel caso dei

convertitori A/D del tipo Sigma-Delta. Esso il supporto ideale per i circuiti misti: data una

qualsiasi operazione da compiere su un segnale, esso pu essere presentato in ingresso ed ivi

convertito da un ADC Sigma-Delta, occupando poco spazio e necessitando di una precisione

circuitale poco spinta. In un secondo tempo lelaborazione dellinformazione pu quindi

procedere interamente in maniera intelligente, digitale, a bordo del chip; alla fine i risultati

si presenteranno al pin di uscita, riconvertiti in analogico di nuovo con la medesima tecnica

Sigma-Delta. Il DAC utilizzato sar ancora una volta velocissimo, e poco influenzato dalla

probabile scarsa precisione dei suoi componenti analogici.

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 4 -

1.3 - Campionamento e conversione ADC di tipo convenzionale

Gli schemi dei tre tipi di ADC accennati in precedenza lavorano, con gran precisione

circuitale, alla minor frequenza possibile; essa fissata dal teorema del campionamento di C.

Shannon, ed la cosiddetta frequenza di Nyquist:

fN f= 2 0

laddove f0 rappresenta la massima frequenza formante il segnale in questione, supposto

essere limitato in banda. Detta fs = 1/Ts la frequenza di campionamento utilizzata, si avr

quindi fs = fN .

E noto dalla teoria dei segnali che un campionamento eseguito su una forma donda,

nei tempi, corrisponde ad una ripetizione dello spettro di frequenza dellonda nel dominio

coniugato; le repliche spettrali aggiunte si posizionano a frequenze multiple di fs :

0 fN fs 2fs 3fs

0 fs = fN = 2f0

f0

f0

Figura 1.1 - Effetto della diversa frequenza di campionamento sugli spettri di segnale

Dalla figura si comprende come il limite dato dal teorema di Shannon implichi in

pratica che londa di tensione venga campionata in modo sufficientemente fitto, tale da poterla

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 5 -

ricostruire univocamente a partire dalla successione di campioni presi, senza scambiarla con

altri segnali (inconveniente che viene definito equivocazione in frequenza, o aliasing).

I dati analogici ottenuti dal campionatore (Sample & Hold) vengono passati agli ADC

che provvedono a rappresentarli con un appropriato numero di bit, adatto a conservare

linformazione di ampiezza prelevata con una precisione sufficiente; vale a dire, non cos

spinta da riprodurre anche le oscillazioni di rumore ad essa sovrapposte. Tale operazione va

necessariamente compiuta con accuratezza, perch losservazione eseguita sullingresso

priva di ridondanza; il flusso binario ottenuto il minimo necessario a descrivere

correttamente i dati in arrivo.

Loperazione di passaggio dalla rappresentazione a valori continui di un segnale x al suo

equivalente digitale a valori discreti comporta necessariamente lintroduzione di un errore di

quantizzazione dato da

e x xquantizzato=

x (continuo)

x (discreto)quantizzato

0

1

2

3

4

5101

100

011

010

001

000 x (continuo)

e

0

+/2

/2

Figura 1.2 - Caratteristica ed errore di quantizzazione

Il numero di livelli orizzontali disponibili in un ADC pari a 2N , dove N il numero di

bit in uscita.

Dalla caratteristica di conversione statica A/D si capisce che la minima variazione del

segnale in ingresso apprezzata dal convertitore vale , che anche chiamato LSB (Less

Significant Bit) perch corrisponde, nelluscita binaria, ad una variazione della cifra meno

significativa. Dellerrore di quantizzazione immediato calcolare la potenza: la sua

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 6 -

distribuzione allinterno del passo minimo uniforme, se il segnale x sufficientemente

variabile nella dinamica a disposizione; avendo inoltre e media nulla si scrive:

e e p e de e de2 22

22

2

2 21

12= = =

( )

/

/

/

/

Distribuendo la potenza ottenuta sullintervallo di frequenza occupato dal rumore (cio

sullintero range fs , se il rumore si suppone bianco come da prassi) se ne ricava infine la

densit spettrale di potenza E2(f) :

E fe

fs

22

( ) =

1.4 - Sovracampionamento : lo scambio risoluzione-velocit

Il concetto base per la comprensione del funzionamento di una catena di conversione del

tipo Sigma-Delta quello del sovracampionamento. A differenza degli ADC discussi

precedentemente il convertitore Sigma-Delta opera ad una frequenza molto superiore ad fN ,

campionando londa di tensione molto pi spesso ed estraendone una sequenza di valori binari

che assai meno risolta in ampiezza, ma molto pi fitta temporalmente.

Il sovracampionamento, in linea di principio, un concetto che si pu applicare anche

alle modalit di conversione convenzionali, cio al caso consueto di campionamento seguito

da semplice discretizzazione del livello letto, spesso denominato PCM (Pulse Code

Modulation) in letteratura. Basta infatti elevare la fs molto al disopra del limite di Nyquist, ad

esempio di un fattore OSR (OverSampling Ratio, o rapporto di sovracampionamento); si

otterr un calo proporzionale della densit spettrale di rumore. Per quantificarlo occorre per

introdurre il Rapporto Segnale/Rumore e la sua misura in decibel, nonch in bit equivalenti.

Dato un ADC con tensione di fondo-scala VFS e N bit di uscita, si definisce SNR

(Signal/Noise Ratio) il rapporto :

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 7 -

SNRPot segnale

Pot rumore

V

VFS

FSN

N= = =..

/

( / ) /

2

2

12

2 122

valutato solitamente iniettando nellADC un rumore bianco che occupa la massima

dinamica possibile, cio il valore di fondo-scala del convertitore; di qui la seconda

espressione fornita. La sua misura in decibel, unit logaritmica, :

SNR SNRdB = 20 10log

Parlare di calo di 6dB di SNR significa dunque riferirsi ad un dimezzamento

effettivo del rapporto. In termini di numero di bit, lespressione diventa :

N SNRSNR

SNR dB= =

=log

log

log/ .2

10

10

20

20 26 02

e dunque un calo di 6dB traduce una perdita di un bit nella risoluzione.

Veniamo ora alleffetto del sovracampionamento : il rumore di quantizzazione q2

e2

, quantit fissa una volta deciso il numero dei bit da utilizzare, viene distribuito su un

intervallo di frequenza di larghezza superiore al consueto fN (0 OSR fN ); la densit

spettrale di potenza di rumore E2(f) cala allora in maniera inversamente proporzionale ad fs , e

la risoluzione S/N guadagna perci 3 dB per ogni raddoppio della frequenza di

campionamento. La banda su cui la E2(f) viene integrata resta invero costante, 0 f0 , ma si

hanno pi dati di segnale a disposizione essendo calato Ts ; da qui deriva il vantaggio netto.

La formula che fornisce il valore del rumore che rimane nella banda del segnale lega la

potenza del disturbo medesimo al tasso di sovracampionamento OSR:

n E f dfe

ff e OSR

s

f02 2

2

02

0 20= = = ( ) / ,

essendo e2

= 2/12 la potenza del rumore di quantizzazione.

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 8 -

Il guadagno ottenuto non molto notevole nel caso considerato, se si pensa ai problemi

squisitamente circuitali che siffatto aumento della fs comporta. Osserveremo per in seguito

che il PCM un caso particolare, degenere, di conversione Sigma-Delta, la quale invece

ottiene vantaggi molto superiori dal sovracampionamento se applicata in modo adeguato.

1.5 - Dal convertitore tracking al Sigma-Delta del 1 ordine

Il circuito che si pu considerare il progenitore del Sigma-Delta il cosiddetto

convertitore tracking, di cui presentiamo lo schema:

U P -D O W NC O U N TE R

IN

O U T

C L O C K

DAC

Figura 1.3 - Schema a blocchi del convertitore tracking

In esso, il segnale in input viene continuamente confrontato con laccumulazione

delluscita; se essa inferiore al dato ora presente al morsetto +, allora luscita va mantenuta

alta, per riportare la sua accumulazione (morsetto -) pi vicina ad IN; questo finch il valore

in reazione raggiunger quello letto dallesterno, facendo ricommutare il comparatore che

abbasser lOUT; ci far decrementare il contatore sul ramo di reazione, ancora tentando di

adeguarsi al dato IN, e cos via. La retroazione negativa tende dunque a far inseguire

lingresso dalloutput del contatore, che ne rappresenta cos una versione digitalizzata. In tale

processo di inseguimento si ravvisano subito due comportamenti caratteristici che sono causa

derrore:

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 9 -

- la differenza di pendenza che pu sussistere tra le due onde, continua e a

gradinata, nel caso in cui linput var troppo velocemente; lincremento del

contatore/accumulatore fisso nel tempo, e ci pu portare ad avere un ragguardevole

errore a monte del comparatore. Questo fenomeno prende il nome di slope overload;

- linstabilit che caratterizza la conversione di un segnale costante IN; ogni

valutazione del comparatore trover infatti un valore troppo alto o troppo basso del

segnale su -, generando una incessante commutazione di OUT. Questo introduce un

granularity noise sul nostro valore convertito, ed inoltre non d informazione

sullesatta dislocazione della continua allinterno del passo di quantizzazione; una

media dellonda quadra in uscita restituirebbe comunque il valore a met tra i due

livelli, avendosi qui duty cycle pari al 50%.

SOVRACCARICODI PENDENZA

GRANULARITA'

OUT

IN

Figura 1.4 - Uscita caratteristica della conversione A/D tracking con errori

Luscita del convertitore tracking una replica quantizzata del segnale in ingresso. Si

osservi per che linformazione in esso contenuta conservata anche nel segnale che comanda

il contatore, che ha laspetto di un flusso binario 011001010110...; basta integrarlo per

recuperare IN. Questo comodo nel momento in cui si debba per esempio trasmettere il

segnale su una linea: non serve un bus da N piste, ma una pista solamente; il ricevitore

allaltro capo della linea a questo punto sar costituito da un blocco di integrazione che

completer il trasferimento dei dati, restituendo IN nel suo aspetto originario.

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 10 -

Questosservazione consente di avvicinarsi ulteriormente al principio di funzionamento

del Sigma-Delta, qualora si esamini il comportamento dellanello tracking come risposta in

frequenza. Lo schema dell ADC tracking pu essere rappresentato agevolmente adoperando

la Trasformata Zeta; lavorando infatti ad istanti di tempo ben definiti, temporizzati dal clock

che governa lUp/Down counter in retroazione, il sistema rappresentabile con un equivalente

a segnali campionati. Essendo il contatore un integratore delluscita, esso avr un polo in

z = 1; inoltre introdurr un ritardo nellanello, per cui schematizzando:

z-1

z1- -1z-1

z1- -1

OUTIN X(z) Y(z)

E(z)

Figura 1.5 - Schemi a blocchi del convertitore A/D di tipo Delta

dove luscita stata prelevata nel nuovo punto proposto, a monte del contatore. Denominando

ora con X(z) linput, Y(z) loutput e con E(z) lerrore di quantizzazione introdotto dalla

presenza della soglia del comparatore, si pu scrivere :

( )Y z X z E zz

z

X z z E z z( ) ( ) ( ) ( ) ( ) ( ) ( )= + +

= +

1

11

1 11

1

1 1

Essendo peraltro 1 - z-1 la trasformata del pi semplice differenziatore discreto, si nota

come segnale e rumore vengano egualmente formati in frequenza da questo circuito. La

caratteristica di trasferimento una derivazione alle differenze finite; in quanto tale, questo

schema di modulazione delluscita digitale prende il nome di modulatore Delta. In ricezione,

la de-enfasi subita dal segnale utile va recuperata come detto mediante integrazione, che per

enfatizzer anche il rumore in banda; non si tratta certo di una tecnica efficiente per il

passaggio A/D, insomma.

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 11 -

Il passo successivo quello di integrare X(z) prima che esso acceda allanello; cos

facendo si otterr stavolta un dato in uscita del tipo:

Y z X zz

zE z z X z z E z z( ) ( ) ( ) ( ) ( ) ( ) ( )=

+

= +

1

11 1 1

11 1

che ha preservato a meno di un ritardo il segnale in ingresso, formando viceversa il rumore di

quantizzazione (introdotto dalla presenza della soglia) verso la zona ad alte pulsazioni, ossia

fN Stavolta, la stringa binaria trasmessa OUT non necessita di alcuna enfasi, e cos stata

veramente ripulita dalla densit spettrale di rumore espulsa dalla banda base. Inoltre, chiaro

che il blocco di integrazione preliminare di X(z) pu essere importato nellanello senza

cambiare lespressione precedente; E(z) non lo vede, nel computo delle trasmittenze H(z) tra

il comparatore ed Y(z). Avendosi gi un integratore in reazione, esso pu anzi essere spostato

sul ramo di andata, continuando a mantenere tutti i trasferimenti come prima.

z - 1

z1- - 1z - 1

z1- - 1X(z) Y(z)

E(z)

W(z)

Figura 1.6 - Schema a blocchi del modulatore Sigma-Delta del 1 ordine

Si allora ottenuto lo schema di principio per il modulatore Sigma-Delta (spesso

abbreviato con lacronimo simbolico ; indica lintegrazione iniziale e la

differenziazione subta dal segnale); nella letteratura inerente, con ordine del modulatore si

definisce il numero di anelli di integrazione nidificati che esso contiene. In particolare, questo

un Sigma-Delta del 1 ordine e ad 1 bit, in quanto presenta un solo anello di reazione e

utilizza un semplice comparatore, cio esce con una sequenza monobit 0-1-1-1-0-1-1-0-0-0-1-

0-...

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 12 -

1.6 - Comportamento nei tempi del modulatore Sigma-Delta : una

simulazione preliminare

La teoria che regola il funzionamento di questi modulatori tuttaltro che banale; la

maggior parte dei modelli utilizzati sono basati di conseguenza su approssimazioni lineari (in

particolare quella che riguarda il quantizzatore), le quali vanno ad un certo punto del lavoro

verificate mediante simulazione del sistema. E quindi opportuno non ritardare il ricorso al

calcolatore, che gi in questa prima fase pu fornire un valido appoggio dando una sensazione

di prima mano sulla qualit dei segnali in gioco in questo oggetto.

La simulazione pu essere tentata a vari livelli. Esistono quantomeno:

un livello astratto, che consente di specificare i blocchi con parametri di tipo

behavioural, ai morsetti esterni, senza modellizzarne n i particolari, n le eventuali non-

idealit;

ed un livello pi circuitale, che permette unanalisi puntuale di sfumature quali

leffetto dello slew-rate o del prodotto guadagno-banda sulle prestazioni globali dello

strumento.

In questa sede duopo utilizzare la prima descrizione, per conservare una visione

dallalto sullargomento; il mezzo informatico da usare allora Simulink, un toolbox di

Matlab della The MathWorks Inc., che lavora essenzialmente per blocchi. Essi possono

essere predefiniti (ve ne sono parecchie decine) oppure realizzati dallutente, mediante delle

chiamate a routine scritte appositamente nel linguaggio di Matlab. Si tratta allora di comporre

lo schema prima descritto con le funzioni a disposizione :

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 13 -

Figura 1.7 - Schema a blocchi Simulink del modulatore Sigma-Delta del 1 ordine

Signal Gen. 1 un generatore di forme donda, capace di produrre sinusoidi, onde

quadre, denti di sega e rumore bianco, a diverse frequenze e con differenti ampiezze; sempre

per centrate attorno a 0 Volt , quindi si rende necessario aggiungere un offset che ci riporti

nella dinamica di ingresso che avremo poi realmente a disposizione (0 - 3.3 V). Lo Zero

Order Hold non servirebbe nemmeno, dato che lanello lavora molto pi velocemente del

segnale esterno, ma in linea di principio obbligatorio per passare dal dominio continuo a

quello discreto. Guadagno posto ad 1, ma pu essere variato per apprezzare i vari

comportamenti del modulatore al variare del guadagno danello. Vi poi un gruppo di

oscilloscopi, come Uscita sovracampionata, per consentire una visione in tempo reale

dellandamento della simulazione. Il Quantizzatore predefinito, ed ha una caratteristica di

trasferimento data da una gradinata ad infiniti livelli; il passo centrale inoltre simmetrico

attorno allo 0, ragion per cui occorre limitare a priori luscita del gruppo di accumulazione

(sommatore Integratore e registro Accumulatore) per limitare il range utile delle gradinata,

e spostare lintera risposta di 0.5 V per giungere al comportamento desiderato. Tali operazioni

sono rispettivamente svolte da Saturazione 0/3 V e da Offset quantizzatore. La taratura

della caratteristica di conversione dellADC interno una parte cruciale della stesura del

circuito, poich dal posizionamento delle soglie dipende la caratteristica di overload del

Sigma-Delta, ossia la massima dinamica di input che non manda fuori linearit il loop. Ci si

cos preventivamente assicurati della bont dellADC inserito, provandolo con una

simulazione a parte:

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 14 -

Figura 1.8 - Circuito Simulink di prova del quantizzatore

Il risultato della prova quello atteso; la scalinata risultante conserva in effetti la

pendenza unitaria, che fa s che il guadagno dellanello intero sia determinato dal solo blocco

di moltiplicazione inserito a tal fine; e presenta inoltre quattro livelli di quantizzazione,

simmetrici attorno ad 1.5 V.

Figura 1.9 - Caratteristica a gradinata del quantizzatore ottenuta

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 15 -

LADC interno che si simula da due bit, come il modulatore a monte del circuito

decimatore oggetto della tesi. Lirregolarit nelle pareti verticali del gradino dovuta

allinterpolazione grafica che il programma esegue tra punti consecutivamente plottati; il

segnale di prova utilizzato per lo sweep della dinamica unonda triangolare.

Lesempio che proponiamo nel dominio dei tempi riguarda la conversione di unonda

sinusoidale a 500 kHz; si riporta qui limmagine fornita dai monitor disposti lungo lanello :

Input :

sinusoide a 500 kHz-

2.4 V picco-picco

Integrazionedellerrore :

-ingresso w(t)allADC Flash

interno

Uscitasovracampionata

a 200 MHz :

-sequenzada 2 bit

Figura 1.10 - Segnali prelevati lungo lanello del modulatore Sigma-Delta

del 1 ordine durante la simulazione

Essa lascia apprezzare come il segnale di input sia conservato nel valor medio

delluscita, mentre il rumore ad alta frequenza; comportamento che si dovr ritrovare poi

anche nella successiva analisi nel dominio coniugato.

In questo esempio introduttivo sono stati utilizzati due bit, in uscita, per rifarsi al nostro

caso reale; del resto, anche i valori di tensione utilizzati e le frequenze operative sono quelle

con cui ci si dovr confrontare in seguito. Per poter avere una certa intelligibilit delluscita,

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 16 -

luso di 4 livelli di quantizzazione sembra qui indispensabile; in effetti, il tasso di

sovracampionamento (OSR) non tale da provocare un calo decisivo del rumore in banda, e

gi dapprincipio si deve partire garantendosi una certa risoluzione in ampiezza, senza fare

affidamento esclusivamente sulleffetto del calo di bit-rate. Ci accade perch linput in

questione un segnale video, quindi a larga banda di per se stesso; un sovracampionamento

di un fattore 24 porta da 8 MHz, frequenza di Nyquist per una ipotetica luminanza, a quasi

200 MHz! Nel caso molto pi frequente di utilizzo per conversioni a frequenze audio, OSR

maggiori di 128 sono comuni, con la conseguenza che anche limpiego di modulatori da 1 bit

sufficiente a conservare una risoluzione elevata.

1.7 - Comportamento in frequenza del modulatore Sigma-Delta : analisi del

rapporto Segnale/Rumore

Le propriet spettrali delluscita del modulatore ricavate al paragrafo 5 sono le seguenti:

- segnale : X(z) z-1 , solo ritardato ma conservato in toto;

- rumore : E(z) (1-z-1) , formato con un profilo a sen(t).

Proprio il profilo passa-alto che il rumore in uscita assume la peculiarit fondamentale

dei convertitori Sigma-Delta. La ricezione dei flussi binari di uscita sar infatti eseguita da un

filtraggio passa-basso, cio da una media, per recuperare lingresso rigettando il rumore; di

nuovo quellintegrazione che gi il convertitore tracking eseguiva nellanello medesimo.

Il pi semplice mezzo per togliere il disturbo sarebbe quindi un filtraggio con profilo

idealmente a scatola nelle frequenze, che comunque difficilmente approssimabile con

circuiti semplici; ci si accontenta di solito di profili a seno cardinale ( sen(f)/f ). Il limite

teorico comunque fissato dal filtro ideale con frequenza di taglio ad f0 , limite di banda per il

segnale da convertire; lintegrazione del rumore dovr dunque essere eseguita sino a tale

limite, come da prassi consolidata. Si noti inoltre come il valore trovato del rapporto

Segnale/Rumore dipenda direttamente dalla sua definizione, che fa riferimento ad un segnale

che sfrutta tutta la dinamica disponibile dellADC. Nel caso Sigma-Delta allora i valori di

SNR trovati si riferiscono alle massime ampiezze di segnale fisicamente convertibili dal

modulatore; per ampiezze inferiori il denominatore (R) del rapporto resta invariato, mentre

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 17 -

il numeratore (S) di SNR che cala proporzionalmente allampiezza. Definito come range

dinamico il rapporto in decibel tra massimo e minimo segnale convertibile, si avr semplice

legame lineare tra esso e SNR :

Range Dinamico(dB)

SNR

VFS

MDS

(dB)

Figura 1.11 - Andamento del Rapporto Segnale/Rumore in funzione della dinamica di

ingresso per la modulazione Sigma-Delta (grafico bilogaritmico)

Il minimo segnale convertibile fissato dallessere SNR = 1 (in analogia al minimum

detectable signal, MDS, dei rivelatori).

Nel paragrafo 4 si gi parlato del caso PCM; configurazione che possiamo considerare

alternativamente come un anello Sigma-Delta di ordine zero, un modulatore cio senza

reazione che si riduce al solo ADC flash interno. La formula che calcolava il rumore era:

n E f dfe

ff e OSR

s

f02 2

2

02

0 20= = = ( ) /

Passando allanello del primo ordine si ha allora una modifica nella formula per

introdurre lo shaping del rumore; ricordando che z ej fTs= 2 il calcolo stavolta :

n E f sen fT dfe

ff T df e f Ts

f

ss

fs0

2 2 20

22 2 2

02

2

034

24

320 0= = ( ) ( ) ( ) ( )

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 18 -

da cui si evince come un raddoppio delle frequenza porti ad un miglioramento di SNR

pari ad un fattore 23/2; sono 9dB, ossia circa 1.5 bit di risoluzione guadagnati grazie

allaumentata bit-rate.

Per capire ci, basta passare dalla lettura della dinamica di funzionamento dellanello in

trasformata Zeta a quella, ora pi intuitiva dopo la simulazione, nel dominio del tempo. Il

fatto che alluscita dellintegratore, indicata con W(z), esista una trasformata Zeta pari a :

( )W z X z zz

z E zz

zz X z E z z( ) ( ) ( ) ( ) ( ) ( ) ( )=

=

1

11

1

11 1

11

11

Tradotto nei tempi significa che il registro accumulatore tenta di PREDIRE il rumore

introdotto dal quantizzatore flash interno; lintegratore sa che lerrore sommato prima di

raggiungere luscita ei, e quindi prova ad abbatterlo dando in input allADC il valore

xi-1 - ei-1. Va da s che se lerrore ei introdotto fosse perfettamente bianco, per definizione

sarebbe impredicibile e dunque vanificherebbe lazione di previsione; ma esso non bianco,

specialmente laddove la bassa variabilit del segnale di ingresso non consente allintegratore

di avere unoutput abbastanza variabile. La staticit delluscita del registro accumulatore

porta ad avere errore non decorrelato dal segnale, ma piuttosto sticky, appiccicoso, ossia

lento; ragion per cui nellerrore possibile riscontrare una dinamica non casuale, magari

addirittura una periodicit, che si deve tentare di riconoscere. Fatto ci, il passo successivo

depurare la sequenza errore dalla dinamica identificata, cio eseguire uno SBIANCAMENTO

del rumore che consenta di lasciarne attiva la sola parte impredicibile, che sperabilmente non

dislocata in banda base (questo discorso meglio formalizzabile in termini di

decomposizione di Wold; ma per gli attuali fini introduttivi ci non si rende indispensabile).

1.8 - Pattern noise per modulatori del 1 ordine

Come facile arguire, la predizione effettuata da questo anello piuttosto inefficace; ci

si potr attendere allora che la risposta a segnali dingresso lenti dellADC Sigma-Delta

introduca componenti di rumore non bianche, ma magari periodiche a bassa frequenza, e

dunque estremamente fastidiose in applicazioni audio: il cosiddetto problema del pattern

noise.

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 19 -

Una simulazione delluscita del filtro al variare di un ingresso costante chiarisce

immediatamente il concetto. Si osservi il comportamento del sistema quando lingresso d.c.

e pari ad 1.8V (si riportano un centinaio di campioni, o taps, delluscita) :

Figura 1.12 - Pattern noise con Vin = 1.8 V costante

In effetti, come evidenziato dalla trasformata Zeta, il segnale presente illeso nella

sequenza elaborata; si trova a bassissima frequenza, cio insito nella media del segnale

ottenuto; il calcolo :

Valor MedioUscita

k==1

100

100

restituisce 1.8000, come atteso. Il rumore sovrapposto al valor medio per molto regolare; l

E(z) delle formule non sar certamento un termine bianco, ma piuttosto si evidenzier la

presenza di alcuni TONI di rumore distribuiti in frequenza. Alcuni di tali toni possono

purtroppo terminare entro il range ove presente il segnale, sporcandolo irrimediabilmente.

Per fortuna, questa fastidiosa eventualit nel caso di costante 1.8V in input non si

verifica. Si noti che il valore 1.8 pu essere espresso come 9/5 = 1 + 4/5, e che quindi la

periodicit di variazione richiesta alluscita era 5; l1 in surplus viene sistemato dalla

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 20 -

posizione del gradino di quantizzazione entro il quale si oscilla. Un colpo ogni 5, per una

sinusoide campionata, una locuzione che ha una traduzione diretta sul cerchio unitario del

piano delle Zeta. Pu essere interpretato come il risultato di una decimazione di una costante

unitaria, quindi come il passaggio da un polo in z = 1 a cinque poli, disposti a pentagono con

un vertice sempre in z = 1 (per propriet matematiche della trasformata Zeta meglio descritte

nel prossimo paragrafo): il tono visibile risulta dunque da una composizione di sottotoni. Il

grafico della trasformata del solo pattern noise in uscita, avendo gi estratto la continua, il

seguente: esso si ricava prendendo 16384 campioni (214) del tipo sopra illustrato. Non

interessando lampiezza delle delta di Dirac, non si riscala il risultato della FFT.

-4 -3 -2 -1 0 1 2 3 4

Figura 1.13 - Spettro delluscita del modulatore con toni di pattern noise

(non mostrata la componente continua)

Se si passa da un valore di tensione da convertire esprimibile con una frazione con basso

denominatore ad un altro pi complesso da tradurre in un rapporto, si avr un periodo pi

esteso delle variazioni, e quindi un pericoloso avvicinamento dei toni alla banda base (qui

riconoscibile come /OSR, in termini di pulsazione). Questo caso si presenta giustappunto

con una frazione del tipo 1/301, non riducibile; la conversione corretta richieder un colpo

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 21 -

ogni 301 transizioni del clock, sulluscita; quindi, londa ripetitiva introdotta sar circa 300

volte sotto la frequenza di campionamento fs , e presumibilmente nella banda di segnale. La

sua potenza non per paragonabile a quella del tono visto precedentemente, quindi i valori

in ordinata della FFT saranno molto inferiori.

Figura 1.14 - Pattern noise con Vin = 1/301 = 3.32 mV costante

Il registro dellintegratore ha una condizione iniziale che stata accuratamente

specificata a zero. E la distanza tra le variazioni che deve essere pari a 301; la prima di esse

pu avvenire ad un istante variabile, prima che lanello raggiunga la situazione di regime. E

importante notare come spesso lo stato iniziale introduca in anello una continua che non si

smorza; infatti Gloop unitario, e in ogni caso pu sopportare variazioni di 30% senza

inficiare la funzionalit dello strumento. Una componente continua iniettata allo startup

nellintegratore pu essere deleteria, e lo si vedr con la prossima FFT che rispecchia un caso

equipollente. Pu per converso essere desiderabile come aiuto al cosiddetto dithering :

volendo decorrelare il rumore dal segnale, una tecnica adottata proprio quella di far circolare

nellanello una continua, o un onda quadra, randomizzante; tale segnale genera un veloce

tremolo in tensione (dither, appunto) che scroller luscita abbastanza sovente, in modo da

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 22 -

non permettere permanenze troppo lunghe delloutput nel range dello stesso gradino di

quantizzazione.

Tornando al pattern noise provato poco sopra, se ne presenta la trasformata: sar simile

ad un pettine di Dirac, ancora; ma essendo le ripetizioni molto distanziate nei tempi, avranno

un corrispettivo fitto nelle frequenze, cio genereranno molti toni sinusoidali (per quanto

piccoli):

-4 -3 -2 -1 0 1 2 3 4

Figura 1.15 - Spettro delluscita del Sigma-Delta con numerosi toni di bassa entit

La spiacevole presenza di questo effetto di pattern noise, nonch leccessiva semplicit

della predizione dellerrore ei , indirizzano verso uno schema pi complesso che preveda un

potenziamento della valutazione dellerrore futuro: un Sigma-Delta del 2 ordine.

1.9 - Il modulatore Sigma-Delta del 2 ordine

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 23 -

Laggiunta di un anello di reazione ulteriore, con il relativo integratore, aumenta la

quantit di memoria presente nel sistema consentendo cos una stima di ei basata sui due

valori precedenti (si veda Candy in [1]).

X(z) Y(z)

E(z)

W(z)

z -1

-1

z -1

z1- -1z -1

-1

z -1

z1 - -1

Figura 1.16 - Schema a blocchi del modulatore Sigma-Delta del 2 ordine

Il nostro convertitore pensato per lavorare su un segnale video; come tutte le

rappresentazioni di immagini quindi esso avr alta correlazione tra i campioni vicini, e di

conseguenza se il rumore non ben decorrelato dal segnale risulter essere correlato a se

stesso; allora il miglioramento della predizione potenzialmente foriero di grandi vantaggi.

Passando di nuovo attraverso il paradigma della trasformata Zeta, si ottiene:

( )( ) ( )

W z X z

z

zz

z

E zz

z

z

z

X z z E z z z X z z E z z z

loop erno

loop ernoloop erno

( ) ( ) ( )

( ) ( ) ( ) ( ) ( )

int

intint

=

+

+ +

+

=

= + + = +

1

1

1

1

1

1

1

1 2

1 1 2 1 2 1

1

11

1

11 1

1

1 2 1 2

cio, nel dominio dei tempi :

y x e e ei i i i i= + + ( )1 1 22

Si spera allora che sia : e e e ee e

i i i ii i + = =

+

2 021 2 1

2 , ossia si esegue

uninterpolazione lineare dei campioni di rumore (il che era prevedibile; lADC del primo

ordine lavora come un mantenitore, ai fini della predizione). La formatura del disturbo

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 24 -

migliora sensibilmente; si passa da uno zero del primo ordine, in banda base, ad uno zero del

secondo ordine. I calcoli del rapporto Segnale-Rumore diventano:

( ) ( )( )n E f sen fT df e T sen fTe

ff T df e f T

sf

s sf

ss

fs

02 2 2 2

02

0

2

24 4 4

02

4

05

4 2 2

216

52

0 0

0

= =

=

( ) ( ) ( )

( ) ( )

Un aumento della frequenza di campionamento porta ad un allontanamento del sen2 di

rumore dalla banda del segnale; ci pi efficace del caso del primo ordine, nella misura di

15 dB per ogni raddoppio di OSR; ritradotto in bit, significano 2.5 bit per il passaggio fs 2

fs. .

Figura 1.17 - Profili in frequenza del segnale e del rumore

per A/D Sigma-Delta del 2 ordine

Il miglioramento si paga in termini di stabilit; lanello semplice reggeva variazioni di

guadagno da 0.7 a 1.3 funzionando correttamente, e comunque restava stabile fino ad un gain

uguale a 2; i due loop nidificati tollerano al massimo variazioni del 5% sui guadagni. Le

amplificazioni per ora sono due, fornendoci un grado di libert in pi (Candy-Temes, [2]).

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 25 -

Un altro inconveniente che si subisce la riduzione della dinamica utile per il segnale.

La rete di predizione pi efficace, ma occupa una dinamica superiore rispetto ai /2

necessari ad ei . Laddove nellanello singolo luscita variava sempre tra due livelli adiacenti di

discretizzazione, ora con il loop doppio essa pu mostrare salti di livello; comportamento

sintomatico del fatto che lingresso alla scalinata stato sollecitato da una variazione robusta,

indotta dalla somma algebrica di ei-2 - 2ei-1 ,che pu raggiungere 3/2. Siccome loverload

del quantizzatore da evitare, perch corrisponde (linearizzando) ad una perdita di

trasmittenza nellanello saturato e quindi ad un aumento secco del rumore (non pi

predetto), occorre limitare a priori la dinamica dei segnali da convertire presentati al primo

sottrattore dellADC Sigma-Delta.

Da ultimo, le imperfezioni degli integratori (lossy integrators) provocano perdite di

memoria che peggiorano la qualit della predizione; per, per notare il build-up dellerrore

provocato da questa non-idealit, occorre avere transitori in input veramente lentissimi.

La reiezione del pattern noise, fortunatamente, cresce assai con laggiunta del secondo

anello; anche con ingressi costanti il sistema decorrela bene il disturbo di quantizzazione dalla

sua causa generante.

Sia detto, per inciso, che aumentare ancora il numero di loop difficile: un ADC Sigma-

Delta del 3 ordine composto da tre integratori ed un ritardo in retroazione, e mostra quindi

forti problemi di stabilit. Esistono altre tecniche per acquisire caratteristiche ai morsetti del

terzo ordine, e ordini superiori: sono denominate MASH (o metodi Multistage) e si basano sul

prelievo di segnali intermedi tra un anello e laltro, nonch sulla ricomposizione delle uscite

binarie per mezzo di blocchi digitali. Presentano comunque anchesse inconvenienti di

matching tra le funzioni di trasferimento digitali e quelle dei blocchi analogici, che devono

essere ben fissate per impedire una trasmissione degli errori tra i circuiti in cascata.

1.10 - Evidenza spettrale delle propriet di shaping sul rumore

Visto tutto ci, resta da risolvere il problema di visualizzare leffetto del filtraggio

eseguito dallanello Sigma-Delta sul rumore introdotto allaltezza del quantizzatore; e questo

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 26 -

va effettuato per anelli di ordine 1 e 2, onde confrontarne visivamente le caratteristiche.

Occorre di conseguenza iniettare un E(z) il pi possibile bianco, per non rischiare di avere una

successione di toni sinusoidali bens una fascia uniforme di rumore che lasci intravedere

leffetto dello shaping. In ultima analisi, occorre decorrelare E(z) da X(z) anche per un Sigma-

Delta del 1 ordine: ma allora si pu inviare direttamente del rumore bianco in ingresso, a cui

lADC non pu certamente infliggere pattern noise! Si acquisisce in tal modo la sicurezza che

E(z) ha spettro uniforme, e quindi subisce in pieno la formatura verso le alte frequenze. Dato

poi che Y(z) = X(z) + ...[E(z) formato], lingresso va sottratto al risultato finale, al fine di

evitare di ritrovarsi la fascia iniettata presente anche alle basse frequenze.

Se ne ricava una riprova grafica evidente delle caratteristiche spettrali dei convertitori

Sigma-Delta :

- anello del 1 ordine: inviluppo del rumore del tipo sen(t)

0 1 2 3 4 5 6 7Pulsazione Omega

Figura 1.18 - Trasformata del rumore simulato per anello del 1 ordine

- anello del 2 ordine : inviluppo del rumore del tipo (sen(t))2 = 1-cos(t/2) , a

coseno rialzato:

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 27 -

0 1 2 3 4 5 6 7

Figura 1.19 - Trasformata del rumore simulato per anello del 2 ordine

In ambedue i casi , la trasformata del rumore presentata ha solo scopo illustrativo; ci

interessa landamento, in particolare alle basse frequenze, dove il fitting stato curato con

maggior attenzione. Essendo osservazioni di una sola realizzazione del processo stocastico di

uscita, esse hanno bassa confidenza statistica, ed andrebbero mediate con tecniche passa-basso

per aumentare questultima; segnatamente, si potrebbe ricorrere alla teoria del

periodogramma, e utilizzare il metodo di Welch. Esso si esplica spezzando la sequenza di

ingresso in pi tronconi, trasformandoli e quadrando la FFT (secondo la definizione di

periodogramma, |H(z)|2 /N ), regolarizzandola con una finestratura e mediando infine tra loro

gli spettri cos ottenuti. La riprova dellesistenza di contatti con lasse delle ascisse,

rispettivamente del primo e del secondo ordine, purtuttavia stata fornita con pi chiarezza in

questo modo.

Il fatto che i dati che nelle tecniche ADC convenzionali erano unici ed indispensabili ad

una ricostruzione dell ingresso ora siano rappresentati nascosti in interi treni di bit ad alta

bit-rate, ha fatto infine comprendere come gli errori introdotti dalle imperfezioni circuitali

sulla singola transizione pesino molto meno, essendo compensati dai filtraggi successivi. Per

giunta, landare a quantizzare luscita dellintegratore in modo tanto manicheo di per s una

garanzia di robustezza rispetto a piccole variazioni dei parametri della rete.

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 28 -

1.11 - Cenni alla realizzazione circuitale

Limplementazione fisica di un modulatore Sigma-Delta si presta molto bene alluso dei

filtri di tipo switched capacitors. Il blocco di integrazione, qualora realizzato con un

amplificatore operazionale con R in input e C in reazione, avrebbe sofferto del mismatch dei

parametri tra i due componenti, certo cos diversi; poter costruire invece un resistore

equivalente servendosi di una capacit garantisce la superiore precisione ottenuta con design

del tipo a centroide comune. Gli interruttori che servono in questo tipo di applicazione sono

transistori MOS, che poi costituiranno il mattone elementare della parte digitale di filtraggio a

valle; loperazionale medesimo ha requisiti che giustificano una sua costruzione a MOSFET;

da ultimo, trattandosi di un circuito di interfaccia verso una logica, pu esso stesso gi agire

da Sample & Hold, condensando in s le funzioni di campionamento e conversione.

Lo schematico conster quindi di una sezione di ingresso che legger alternativamente il

dato continuo in arrivo, e invertendolo quello continuo in reazione; un operazionale con

capacit in retroazione, che integrer tale errore danello; seguito da una sezione di

conversione A/D che potrebbe consistere di un solo comparatore, oppure di un semplice

convertitore flash da pochi bit; la sua uscita la stringa binaria che viene effettivamente

trasmessa a valle, e che va anche riportata allingresso previa conversione DAC (si

confronter infatti con un input scalare, ovviamente). Nel caso di anello del 2 ordine, tale

disposizione schematica risulta essere:

AD C

1

2 1

2

1

1 2

2

DAC

C

CC

C

In

Out

z -1

Figura 1.20 - Esempio di realizzazione a switched-capacitors di un

modulatore Sigma-Delta del 2 ordine

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 29 -

1.12 - Decimazione del segnale digitale sovracampionato

Dalla precedente, sommaria rivisitazione delle propriet peculiari dei convertitori

Sigma-Delta si deduce senzaltro la necessit di una catena di elaborazione digitale a valle del

filtro a switched capacitors. Luscita dellanello nel nostro caso a 2 bit, e velocissima;

contiene in s tutta linformazione desiderata, ma anche parecchio rumore seppure traslato in

frequenza. Non certamente fruibile da un DAS (Data Acquisition System) convenzionale;

gi si parlato di come gli ADC tradizionali escano con sequenze di parole binarie, a molti

bit, rinnovate con frequenza poco superiore a quella di Nyquist. Il segnale grezzo che esce dal

blocco flash interno va quindi sottoposto ad un processo di estrazione dellinformazione, che

si tradurr in un baratto tra velocit (da calare) e numero di bit di ogni parola (da alzare). In

nuce, quel sovracampionamento che costituiva la premessa alla eccezionale robustezza

dellanello ora non ha pi ragione di essere mantenuto, dal momento che si lavora con oggetti

digitali e quindi immuni da errore; servono piuttosto i 2.5 bit di risoluzione in ampiezza

garantiti da ogni raddoppio della fs rispetto al suo valore minimo teorico. Proprio per questo

opportuno non parlare di convertitore A/D Sigma-Delta tout-court, quanto piuttosto di

modulatore1 Sigma-Delta e di catena di conversione A/D di tipo Sigma-Delta.

La funzione di abbassamento della frequenza operativa in ambito digitale prende il

nome di decimazione: da un bitstream rapido si prende un campione ogni N, rallentando del

medesimo fattore la sequenza a valle del blocco. Tale azione non indolore, nel dominio delle

frequenze: se loperatore z-1 , infatti, rappresenta il ritardo unitario a 200 MHz, ad una bit-rate

decimata a 50 MHz esso vale 4 dei ritardi precedenti. Potremmo chiamare questo nuovo

ritardo con Z-1, laddove :

Z z N=

La trasformata Zeta delluscita del loop Sigma-Delta invariata, formalmente; a meno

della sostituzione di z con Z-N. Questo significa che da ogni polo se ne generano N,

equidistanziati in fase sulla circonferenza individuata dal modulo (elevato ad 1/N) del polo

originario e centrata nellorigine degli assi complessi. Dove prima si incontrava una sola

1 Un modulatore, oggetto usato per le Telecomunicazioni, ha due ingressi : si pensi alla modulazione di ampiezza AM, o difrequenza FM. In entrambi i casi lun segnale interagisce con il secondo, trasformandolo. Parlare di modulatore Sigma-Delta significa invece fare riferimento alla modulazione della stringa binaria di uscita sulla base dellingresso, come simodula una portante QPSK con un flusso binario; si scambia cio leffetto con la causa, usando la figura retorica dellametonima.

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 30 -

replica spettrale del segnale e del rumore, ora se ne incontrano N; il pericolo di commettere

aliasing quindi aumentato, consistentemente col fatto che il segnale di partenza viene ora

osservato in meno punti.

Laspetto della sequenza discreta passato da un flusso fitto ad uno pi rado;

dualmente, nelle frequenze si avr uno spettro del segnale, e del suo rumore intercalato, che

tende a collassare verso lorigine dellasse delle ascisse, divenendo pi stretto. Graficamente,

avendo gi presente la forma delle onde con le quali ci confronteremo:

Figura 1.21 - Effetto della decimazione sugli spettri in uscita da un anello Sigma-Delta

In un caso come quello illustrato la decimazione di un fattore 2. Solo un picco di

rumore stato riportato, per non congestionare il grafico.

Se si decima invece di un fattore N = 4, si avr la presenza di ben tre repliche spettrali

che si immergono nel rumore di modulazione della replica ferma in banda base; si produce

cos un deterioramento del segnale inaccettabile per gli standard audio ed anche per quelli

video. Occorre allora predisporre un blocco di filtraggio, digitale, immediatamente a monte

della sezione di downsampling. La forma del filtro deve soddisfare due requisiti fondamentali:

- essere adatta a ripulire dal rumore le bande adiacenti alle frequenze alle quali

scenderanno le repliche;

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 31 -

- avere una implementabilit numerica non troppo complessa, per non incidere

eccessivamente sulla difficolt della progettazione successiva.

La prima idea realizzativa viene dalla teoria delle misure simultanee, usata nei

dispositivi numerici per lelaborazione dei segnali. Prendere un campione su N senza previo

filtraggio significa perdere informazione netta; se per si fa in modo di leggere i campioni di

ampiezza ed i campioni (ad esempio) della derivata dellampiezza, anche leggendo la

sequenza pi lentamente della frequenza di Nyquist la ricostruibilit dellonda garantita. Pi

in generale: campionare una generica funzione che abbia una qualche forma di memoria dei

campioni adiacenti non letti, oltre alla mera magnitudo del segnale, riporta il loro contenuto

informativo nella catena. E come se si avesse a disposizione una successione di combinazioni

lineari dei taps, che fornisce i termini noti per scrivere il sistema di equazioni che lha

generata; per riottenere i valori dei campioni combinati basta invertire il sistema lineare.

Nel nostro caso basta collezionare linformazione relativa al rumore, supposto bianco,

che affligge i taps intermedi; si pu allora pensare di mediare N campioni tra una lettura e la

successiva. In effetti, nel dominio trasformato alloperazione :

yx

NY z X z

z

NX z

N

z

zn

ii

Ni

i

N

N

=

=

=

=

=

0

1

0

1

1

1 1

1( ) ( ) ( )

corrisponde un abbattimento del rumore alle varie frequenze del tipo :

Y f X fsen fNT

N sen fTs

s

( ) ( )( )

( )=

Il blocco precedente del tipo FIR (Finite Impulse Response), quindi comodo da

realizzare e con bassa latenza di risposta.

Il seno cardinale periodico, trattandosi di segnali discreti; e presenta proprio N zeri in

ogni periodo di 2, preserva cio dal rumore le zone che alloggeranno le repliche in seguito.

Laspetto della sua risposta allimpulso quello di N campioni alti 1/N e poi di un pad infinito

nullo; per analogia con un pettine, tale categoria di filtri denominata COMB FILTERS.

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 32 -

1.13 - Scelta dellordine e del fattore di decimazione

Come esplicitato nel tutorial di Crochiere-Rabiner ([3]), in genere ogni fase di

decimazione ammette una implementazione pi semplice se svolta in pi passi. Il primo stadio

dovr essere veloce, ma se non cala la fs di molto potr anche essere un filtro poco selettivo

in frequenza, e quindi semplice; lultimo filtro potr viceversa avere requisiti molto restrittivi

in termini di ripple e intervallo di transizione tra stop- e pass-band, perch ormai opera su una

sequenza lenta. Lottimizzazione del carico computazionale della catena di decimazione passa

allora necessariamente attraverso il sezionamento dellazione, da compiere in almeno due fasi

successive. Dovendo essere il nostro prodotto finale un commodity system da piazzare su

chip che svolgono altre funzioni, si adottato uno schema a due stadi di decimazione: un FIR

(Finite Impulse Response, all-zeros) veloce ed un IIR (Infinite Impulse Response, all-poles)

pi lento. Il primo si deve occupare solo di eliminare il noise a crescita lenta; il secondo ne

raffina lazione e si occupa anche delle distorsioni introdotte vicino alla banda base. Partendo

da un fattore di sovracampionamento pari a 25 (200 MHz / 8 MHz di Nyquist per il segnale di

tipo televisivo), opportuno scendere di 24 volte per conservare un poco di margine anti-

aliasing: e si dimostra appropriato dividere la decimazione in un fattore 4 per il FIR ed un 6

per lIIR.

Seguendo infatti la filosofia a comb filters, si nota che un limite inferiore per la

frequenza decimata dal FIR 4 fN . Scendendo ulteriormente infatti la quantit di rumore

riportata in banda dal refolding - per quanto efficace sia stata la riduzione del medesimo

grazie al primo minimo - tende a salire sensibilmente (si confrontino i grafici forniti da

Candy-Temes ancora in [2]); fino a 4 fN si sconta invece un peggioramento pressocch

costante di 0.14 dB. Il leggero taglio che il lobo principale del sinc inferisce al segnale X(z)

viene per giunta limitato entro 2.75 dB di calo; inoltre, la reiezione ai disturbi in alta

frequenza che potrebbero venire immessi in banda base, data dal rapporto tra lattenuazione

data dal sinc alle due frequenze corrispondenti che si sovrapporrano poi nel folding, di 48

dB.

Lavorare a 200 MHz con tale filtro non per agevole: opportuno spostare la

complessit maggiore dove le frequenze sono gi calate. Inoltre la struttura a comb filter

implementa quella operazione di media che abbiamo visto essere necessaria per recuperare il

segnale X(z) uscente da un modulatore Sigma-Delta; ma essendo i campioni di h(n) uguali ad

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 33 -

1/N, il filtraggio richiede uno stadio finale di divisione per 1/N dei valori calcolati, per avere

guadagno unitario; e la divisione si riduce ad uno shift binario, se N una potenza di 2;

meglio dunque scendere solo di un fattore di decimazione 4 con lo stadio FIR, giungendo ad

una frequenza intermedia fd di campionamento pari a 6 fN .

Il sinc alla prima potenza dato dalla semplice operazione di media ha comunque dei lobi

laterali che sono relativamente alti; ricordando che lo shaping del rumore del secondo ordine

nel nostro caso, desiderabile avere una decrescenza dei lobi del filtro almeno del terzo

ordine, in maniera da contrastare con successo la crescita di 20 dB/decade dello spettro di

disturbo. Per confermare questintuizione utile per procedere in modo pi formale (come

fatto da Candy in [4]).

Nota la trasformata Zeta del rumore uscente dal modulatore Sigma-Delta, ad essa si

applica il filtraggio a sinc di ordine pari almeno allordine dellanello; lo spettro ottenuto va

poi ridiviso per il profilo del sinc per riportarlo indietro, alluscita dellanello, laddove esso

potr essere interpretato come rumore prodotto da un ADC flash interno avente pi bit di

quello reale. Indicati con K lesponente del sinc e con L lordine del loop, si ottiene:

K = L :

N z E z zz

z NL

N K

K' ( ) ( )( )=

11

1

111

dopo la semplificazione, passando ad esprimere le frequenze con z e j fTs= 2 , e noto che il

rumore bianco ha e = / 12 di potenza da trasformare in densit spettrale unilatera :

( )N f e T NN

sen fNTs K sK

' ( ) ( )= 2 2

stavolta lestensione in frequenza infatti fNTs

= 12

. Per tornare a monte del decimatore

occorre ridividere per il seno cardinale periodico, ottenendo infine lespressione del rumore

equivalente :

( )N e NT sen fTequiv s s K' ( ). = 2 2 .

-

La catena di conversione A/D Sigma-Delta ed il ruolo del decimatore - Cap. 1

- 34 -

Questultima va confrontata con quella fornita in precedenza al paragrafo 9; se ne noter

limmutata forma e laggiunta di N, che implica un peggioramento del rapporto segnale-

rumore. Agli effetti esterni tuttavia utile rimarcare che N(f) analogo a quello di un Sigma-

Delta con passo di quantizzazione pari a /NK ; ecco allora trovata una maniera per

determinare il numero di bit di risoluzione alluscita dal decimatore FIR.

K = L+1:

( )

N z E zz

z N N

z

z

E z zz

z N

N L

L

N

mediatoa pettine

LN L

L

' ( ) ( )

' ( )

=

=

=

1

1

1 1 1

1

11

1

1

1 1

11

ed il rumore ha gi subto un abbassamento da parte del filtro; avendone mediati N campioni,

il calo di potenza sar proprio N, ossia sul valore quadratico medio N :

( )

( )

N f eT

N

N

Nsen fNT

e TN

sen fNT

sL s

s L sL

L' ( ) ( )

( )

= =

=

22

21

2

Stavolta il passo dei livelli di quantizzazione del Sigma-Delta equivalente vale N/NK

. Il rumore equivalente :

( )N e T sen fT sen fTsen fNTequiv s s

L s

s

' ( )( )

( ).=

2 2

che valutato a bassa frequenza non praticamente diverso dal rumore originario. Si conferma

quindi la bont dellidea di utilizzare un ordine di decimazione K = L+1, cio nel nostro caso

K = 3. Tale scelta pressocch universalmente adottata nelle catene di filtraggio e

downsampling successive agli ADC sovracampionati; i vantaggi portati dalluso di

caratteristiche passa-basso di ordine superiore non bilanciano la complessit aggiunta, ed anzi