1 Prof. Marco Mezzalama a.a. 06/07 Politecnico di Torino Dip. di Automatica e Informatica M....

-

Upload

lalia-volpi -

Category

Documents

-

view

217 -

download

0

Transcript of 1 Prof. Marco Mezzalama a.a. 06/07 Politecnico di Torino Dip. di Automatica e Informatica M....

1 Prof. Marco Mezzalama a.a. 06/07

Politecnico di TorinoDip. di Automatica e Informatica

M. Mezzalama - M. Rebaudengo

BUS DI CPU

2 Prof. Marco Mezzalama a.a. 06/07

BUS veloce(PCI)

BUS lento(ISA)

CPU

Coproc

DRAM Cache(L2)

clock Cache(L1)

BUS veloce(AGP)

LAN

Host bus(FSB)

DESKTOP SYSTEM

3 Prof. Marco Mezzalama a.a. 06/07

In Dual Independent Bus (DIB) architecture systems the single system bus is replaced by a "frontside bus" for shuttling data between the CPU and main memory, and between the CPU and peripheral buses and a "backside bus" for accessing Level 2 cache. The use of dual independent buses boosts performance, enabling the CPU to access data from either of its buses simultaneously and in parallel.

Dual

Idependent Bus Arch.

4 Prof. Marco Mezzalama a.a. 06/07

Dual Idependent Bus Arch.

5 Prof. Marco Mezzalama a.a. 06/07

SYSTEM BUS

PCI

CPU

DRAM Cache(L2/3)

Cache(L1/2)

Memory bus

SERVER SYSTEM

PCI

CPUCache(L1/2)

6 Prof. Marco Mezzalama a.a. 06/07

Ciclo di Bus

È la sequenza di eventi attraverso la quale la CPU comunica con la memoria, con un dispositivo di I/O, con l’Interrupt Controller.

In funzione dei processori può essere costituito da 2 o 4 cicli di clock di sistema.

Internamente esistono sempre 4 periodi

Si compone di almeno 4 fasi, denominate T1, T2, T3, T4.

• T1: sull’address bus viene scritto l’indirizzo

• T2, T3, T4: sul data bus viene messo il dato.

Se la CPU non deve accedere all’esterno, i segnali di controllo del bus sono inattivi ed i relativi piedini sono in alta impedenza.

Se nessun altro dispositivo utilizza il bus, questo si trova allora nello stato di idle.

7 Prof. Marco Mezzalama a.a. 06/07

Ciclo di Bus

Nel 8086 il ciclo interno (4 CLK) è identico al ciclo esterno di bus

Nei processori tipo pentium o nei bus di sistema (es. PCI) il ciclo di bus è di 2 CLK

Ad esempio nel bus del pentium (host bus o memory bus) a 100MHz il trasferimento avviene in 2 CLK, cioè in 20ns.

In generale si indica la capacità di trasferimento del bus espressa in MBps (Mega Byte per secondo)

Esempio: pentium con DBUS a 64 bit e 100MHz si ha:

(64/8)*100M/2 = 400MBps

Essendo 2 i periodi di clock per ciclo di bus

8 Prof. Marco Mezzalama a.a. 06/07

PCI CLK = 66MHz, 32 bit DBUSAGPx4 = 66MHz x 4

9 Prof. Marco Mezzalama a.a. 06/07

Ciclo di Bus

Bus Cycle

T1 T2 T3 T4 T1 T2 T3 T4

Address Buffer Data Address Buffer Data

CLOCK di BUS

CLOCK di BUS interno

10 Prof. Marco Mezzalama a.a. 06/07

Ciclo di Lettura

• T1: sull’address bus viene scritto l’indirizzo

• T2: la CPU forza sul data bus il valore Z

• T3, T4: la memoria scrive il dato sul data bus.

11 Prof. Marco Mezzalama a.a. 06/07

Ciclo di Scrittura

• T1: sull’address bus viene scritto l’indirizzo

• T2: la CPU scrive il dato sul data bus

• T3, T4: la memoria legge il dato dal data bus.

12 Prof. Marco Mezzalama a.a. 06/07

Cicli di Idle

Vengono inseriti dalla CPU quando necessario, ossia quando:

• la CPU non necessita di nuovi dati e

• la coda interna delle istruzioni è piena, e non può essere eseguita alcuna fase di prefetch.

13 Prof. Marco Mezzalama a.a. 06/07

Cicli di Wait

Se la memoria non è sufficientemente veloce, lo segnala alla CPU, e questa inserisce tra T3 e T4 una serie di stati di attesa (wait states) fino a che la memoria risponde.

Per comunicare all'8086 la necessità di uno o più cicli di wait, la memoria esterna invia un segnale sul pin READY.

14 Prof. Marco Mezzalama a.a. 06/07

PENTIUM

ABUS (A31-A3, BE7-BE0)

DBUS (64 bit)

ADS

Stato (D/C, W/R,M/IO)

READY

BIT PARITA’ (DP7-DP0)

DMA

INTERRUPT

L1/L2 cacheControl (MESI)

MULTIPROC.SYNCR

15 Prof. Marco Mezzalama a.a. 06/07

Segnali di Controllo

ADS (o ALE): il fronte di salita segnala durante T1 che sull’address bus è pronto un indirizzo.

IO/M*: indica se il ciclo di bus fa riferimento alla memoria o a un dispositivo di I/O;

R/W*: indica se si tratta di un ciclo di lettura o scrittura

C/D: indica se sul bus sono presenti dei dati o no

16 Prof. Marco Mezzalama a.a. 06/07

HOLD e HLDA

Costituiscono l’interfaccia verso il controllore di DMA.

Quando un dispositivo desidera acquisire il controllo del bus, porta a 1 il segnale HOLD.

A questo punto il processore, terminato il corrente ciclo di bus, pone in alta impedenza i segnali di ABUS, e i segnali di controllo

Quando il dispositivo rilascia il bus, riporta a 0 il segnale HOLD.

17 Prof. Marco Mezzalama a.a. 06/07

Segnali di Interrupt

Sono:

• INTR (input): richiesta di interrupt da parte di un dispositivo esterno

• INTA* (output): accettazione della richiesta da parte della CPU, e temporizzazione del trasferimento del codice di interrupt

• NMI (input): richiesta di interrupt non mascherabile.

18 Prof. Marco Mezzalama a.a. 06/07

READY

READY rappresenta un segnale di sincronizzazione con l'esterno.

All'esecuzione dell'istruzione WAIT, il processore testa il segnale READY e, se vale 1, inizia ad eseguire dei cicli di idle; quando READY torna a 0, il processore esegue l'istruzione successiva alla WAIT.

19 Prof. Marco Mezzalama a.a. 06/07

BEi

Nell’80x86 il segnale BEi* (Bank Enable), con i che varia tra 0 e il numero di byte di parallelismo del DBUS, definisce la dimensione e l’allineamento del tipo trasferito:

BE0* = 0 trasferimento del byte meno significativo

BE1* = 0 trasferimento del secondo byte

ES.

nell’istruzione MOV AL, (BX) viene attivato BE0

nell’istruzione MOV AX, (BX) viene attivato BE0 e BE1

nell’istruzione MOV EAX, (BX) viene attivato BE0, BE1, BE2 e BE3

20 Prof. Marco Mezzalama a.a. 06/07

LOCK*

Indica che un’istruzione con il prefisso LOCK e’ in corso di esecuzione e conseguentemente il bus non puo’ essere utilizzato da un altro potenziale master.

21 Prof. Marco Mezzalama a.a. 06/07

22 Prof. Marco Mezzalama a.a. 06/07

PENTIUM BUS CYCLE

Nel pentium esistono due tipi di cicli:

•single transfert: trasferimento di un solo dato

•Burst cycle: trasferimento di 4*64 bit (32 byte) effettuato per aggiornamento della L1 cache nei casi di cache miss

23 Prof. Marco Mezzalama a.a. 06/07

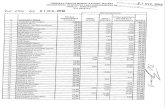

CICLO DI BUS CON DATA BUS A 32 BIT(ciclo lettura)

Con bus a 32 bit, ABUS è costituito dai seguenti segnali:A31-A2BE3-BE0 (4 byte)

24 Prof. Marco Mezzalama a.a. 06/07

CICLO DI BUS CON DATA BUS A 32 BIT(ciclo scrittura)

25 Prof. Marco Mezzalama a.a. 06/07

CICLO DI BUS CON DATA BUS A 32 BIT

(ciclo scrittura con wait)

VerificaSegnale di READY’: nel primo casoLa memoria NON è pronta, nel secondo SI

26 Prof. Marco Mezzalama a.a. 06/07

PENTIUM BUS CYCLE

(esempio con Dram)

Si supponga di avere un pentium con host bus a 300MHz che interfaccia una memoria dram con ta = 80 ns

Nel caso di single transfert (trasferimento di un solo dato) sono richiesti un certo numero di cicli di wait.

VerificaSegnale di READY’

tacpu

Ciclo di bus(2*tclock)

27 Prof. Marco Mezzalama a.a. 06/07

PENTIUM BUS CYCLE

(esempio con Dram)

Si possono fare le seguenti considerazioni:

•host bus a 300MHz significa che un ciclo di bus dura:

33*2 = 66 ns (tclock = 33ns)

•La cpu acquisisce i dati dal bus (memoria) in circa ¾ di un ciclo di bus (si veda figura, tacpu). Nel caso in esame la memoria dovrebbe pertanto rispondere in circa 50 ns.

•Ogni ciclo di wait inserito ha durata (tw) pari ad un periodo di clock. Nel caso in esame 33 ns.

In generale dovrà pertanto valere:

ta(memoria) <= tacpu + n*tw

28 Prof. Marco Mezzalama a.a. 06/07

PENTIUM BUS CYCLE

(esempio con Dram)

Applicando la:

ta(memoria) <= tacpu + n*tw

al caso in esame, si ottiene:

80 <= 50 + n*33

Da cui si deriva che il numero di cicli di wait da inserire è pari ad n = 1.

N.B. nel caso reale di DRAM è più corretto impiegare non il ta, il tempo di cyclo, tcycle, ponendosi sempre nel caso peggiore (worst case analisys). Si ricorda che tcycle è pari a circa 2*ta.

29 Prof. Marco Mezzalama a.a. 06/07

PENTIUM BUS CYCLE

(Burst cycle)Nei microprocessori con cache on –chip la maggior parte degli accessi alla memoria è

dovuta alla necessità di aggiornare la cache in presenza di cache miss o di scritture

della cache in memoria nel caso di write di dati sulla cache.

Si ricorda che la cache è organizzata in cache line, ognuna delle quali riporta il

contenuto di un certo numero di byte ADIACENTI della memoria

Ne deriva che l’aggiornamento della cache consiste nel leggere nella cache stessa un

dato numero di byte dalla memoria (principio di località). Pertanto tale

operazione deve essere fatta nel più breve tempo possibile per evitare che la cpu

resti in attiva per lungo tempo.

Da un punto di vista progettuale due sono i parametri in gioco:

• Il numero di byte associati ad una cache line

• Il tempo di aggiornamento della cache, ossia il numero di bus cycle da effettuare

per la lettura della memoria

30 Prof. Marco Mezzalama a.a. 06/07

PENTIUM BUS CYCLE

(Burst cycle)Quanto maggiore è il numero di byte della cache line tanto più è “efficace” il principio di località, ma tanto maggiore è il tempo di attesa/inattività della cpu.

Negli attuali processori il compromesso è ottenuto limitando a 4 i cicli di bus per aggiornare la cache, ma incrementando il numero di segnali del DBUS in modo che ad ogni transazione si possano leggere un elevato numero di byte.

Esempi

DBUS 32 bit, (4 bus cycle x 4 byte) = 16 byte cache line

DBUS 128 bit, (4 bus cycle x 16 byte) = 64 byte cache line

31 Prof. Marco Mezzalama a.a. 06/07

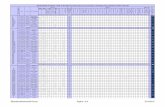

PENTIUM BUS CYCLE

(Burst cycle)Per ottimizzare i tempi di trasferimento si sfrutta il fatto che i byte sono adiacenti e quindi gli indirizzi noti a priori.

In tal modo la BIU realizza un ciclo di burst, composto da 4 cicli di bus di cui solo il primo deve essere di 2 clock. I restanti sono di un clock solo. Si ha cioè un ciclo di burst detto “2-1-1-1”

Ad esempio nel caso di bus da 100 MHz, si ha un ciclo burst della durata di 20+10+10+10 = 50, rispetto agli 80 di 4 cicli di bus normali.

Va da se che le memorie devono essere in grado di rispondere in tali tempi: da qui le nuove categorie di memoria dette “fast operative”, tipo le DDR DRAM.

32 Prof. Marco Mezzalama a.a. 06/07

PENTIUM BUS CYCLE

(Burst cycle)

Burst cycle (2-1-1-1)