POLITECNICO DI MILANOSimulink, NI VeriStand e Simulink Desktop Real-Time. Il tipo di test dipende...

Transcript of POLITECNICO DI MILANOSimulink, NI VeriStand e Simulink Desktop Real-Time. Il tipo di test dipende...

P O L I T E C N I C O D I M I L A N OFacoltà di Ingegneria

Scuola di Ingegneria Industriale e dell’InformazioneDipartimento di Elettronica, Informazione e Bioingegneria

Corso di Laurea Magistrale In Ingegneria Elettrica

A D VA N C E D T E C H N I Q U E S F O R H I L S I M U L AT I O NO F R E N E WA B L E E N E R G Y: T H E C A S E O F P V S Y S T E M

Supervisor:Prof. Giambattista Gruosso

Master Graduation Thesis by:Harshavardhan Palahalli Mallikarjun

Person Code: 10543042

Academic Year: 2017-2018

Harshavardhan Palahalli MallikarjunCorso di Laurea Magistrale In Ingegneria ElettricaAdvanced Techniques For HIL Simulation of Renewable Energy: TheCase Of PV System

A B S T R A C T

The need of alternative energy is pushing PV to be more pre-dominant to supply energy. Conducting real-time simulationsbefore commissioning the PV plant is much observed to vali-date the project proposals. As PV mathematical model dependson the temperature and the irradiation level of the atmosphere,there is a need of real-time simulation to study the dynamiccharacteristics of PV system.

The idea of this work is to present Real-time simulation frame-work, coupling modeling environments such as Matlab Simulinkto a real-time hardware like National Instruments myRIO. Theidea is to draft an implementation of Hardware-in-the-loop sim-ulation for renewable energy systems by taking a case of PVincluding control strategy and interaction with the rest of thesystem like micro-grid. They have to cope with different con-straints, the former is the solution of the differential algebraicequation (DAE) system required by the PV which is stronglynon-linear. The latter is the fast simulation of the dynamic con-trol strategy of PV such as Maximum power point tracking al-gorithm and the micro-grid with frequency regulation. In themiddle several other requirements, including Hardware-in-theloop simulation having interface algorithm of the models overEthernet and actual measurement is discussed.

This work proposes two kinds of test bench using tools likeSimulink, NI VeriStand and Simulink Desktop Real-Time. Thechoice of kind of simulation depends on the complexity of themodel that has to be simulated in real-time. The test benches 1

and 2 uses Simulink, for the model design and C code genera-tion for execution in myRIO hardware. Co-Simulation platformis presented in the case of test bench 3, where the model isdesigned in Simulink and they are compiled to execute in In-tel’s processor of the desktop, and the PV model built usingLabVIEW VI is made to run as standalone system in myRIO,later both the systems are synchronized through Ethernet forthe execution in real-time.

This thesis contains 11 Chapters, in which all the phenomenaof Hardware-in-the-loop simulation in the case of PV, havingdifferent interface algorithms are being presented.

v

E S T R AT O

La necessità di introdurre energia alternativa, nel nostro studioè l’introduzione del sistema fotovoltaico(PV) per fornire ener-gia al sistema elettrico. Prima di poter realizzare fisicamenteil sistema fotovoltaico dobbiamo simularlo in modo da poterprevedere e capire il comportamento del sistema il modellomatematico del sistema fotovoltaico dipende dalla temperaturae dal livello di irraggiamento dell’atmosfera, inoltre dobbiamostudiare la caratteristica dinamica del sistema fotovoltaico at-traverso la simulazione in tempo reale (real-time-simulation).

In questo lavoro proponiamo l’uso di Real-time simulationframework usando Matlab Simulink per la modellizzazione deicomponenti della rete e National Instruments myRIO per real-time hardware. L’idea è di implementare una bozza di Hardware-in-loop simulation per i sistemi di energia rinnovabile, pren-dendo come caso il sistema fotovoltaico con il suo corrispettivosistema di controllo e l’interazione che il PV ha con la micro-grid.

Per realizzare la modellizzazione del PV dobbiamo gestire iseguenti vincoli:

1. Risoluzione della equazione differenziale del sistema richi-esta dal PV, la quale è una equazione non lineare.

2. Realizzazione di Hardware-in-loop-simulation collegandoi modelli precedentemente citati attraverso il cavo ether-net e le misure attuali .

3. Realizzazione della simulazione delle dinamiche di con-trollo del PV attraverso l’algoritmo del Maximum pointtracking e la regolazione in frequenza della micro-gird.

Questo lavoro propone due tipi di test usando strumenti comeSimulink, NI VeriStand e Simulink Desktop Real-Time. Il tipodi test dipende dalla complessità del modello che vogliamo sim-ulare in real-time, inoltre in questo lavoro abbiamo fatto tre test.Sia il test 1 che il test 2 usano Simulink, per modellizzazione eil codice C è generato per essere eseguito in myRIO hardware.Il test 3 utilizza la piattaforma di Co-simulation, dove il mod-ello è disegnato in Simulink ed è compilato per essere eseguitoda Intel’s processor del Desktop, mentre il modello del sistema

vii

fotovoltaico è costruito utilizzando LabVIEW VI ed è stato fattoeseguire come sistema autonomo in myRIO, dopo di che i sis-temi vengono sincronizzati grazie all’ethernet per eseguirlo inreal-time.

Questa tesi contiene 11 capitoli, nei quali tutti i fenomenidi Hardware-in-the-loop simulation nel caso del sistema foto-voltaico, avendo diverse interfacce.

viii

A C K N O W L E D G E M E N T S

I would like to tribute my deepest gratitude to the following in-dividuals, for helping me in the development of the this work.

To Professor Giambattista Gruosso, for providing me an oppor-tunity to work under his supervision, for the development ofthis thesis and also for introducing me to the field of research.His guidance and ideas intrigue me to work on this topic andto gain more knowledge in the subject matter of interest.

To Yujia Huo, Phd Student of Politecnico Di Milano who helpedme to solve the complex modeling problems and also for pro-viding the key insights, during the development of this workand the research paper.

To Bhavya Ponna, for helping me to solve the errors encoun-tered while typesetting this document.

To Srikanth Kadiga and Mahanta Raju Penmatsa, my fellowbatch mates who provided me all kind of support, when I wasin need of it.

To Repubblica italiana, for allowing me to study in it’s pres-tigious institution with scholarship and for providing all thebasic needs to nurture my career.

To my parents, for their support from long distances whom Iowe all of my achievements to.

ix

C O N T E N T S

1 introduction 1

1.1 Motivation . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 Need of Real-time PV simulations . . . . . . . . . 2

1.3 Problem Formulation . . . . . . . . . . . . . . . . . 3

1.4 Research Objectives . . . . . . . . . . . . . . . . . . 3

1.5 Thesis Outline . . . . . . . . . . . . . . . . . . . . . 4

i theoretical aspects of hil 5

2 hardware-in-the-loop for power electrical

systems 7

2.1 Simulation . . . . . . . . . . . . . . . . . . . . . . . 7

2.1.1 Real-time Simulation . . . . . . . . . . . . . 8

2.2 Hardware-in-the-loop . . . . . . . . . . . . . . . . . 12

2.2.1 Different HIL methodologies for Electricdrive system . . . . . . . . . . . . . . . . . . 16

2.3 Power-hardware-in-the-loop . . . . . . . . . . . . . 22

2.3.1 Basic architecture of P-HIL simulation . . . 23

2.3.2 Real-time digital simulator and Interfacein P-HIL simulation . . . . . . . . . . . . . 24

2.3.3 Interface Algorithm . . . . . . . . . . . . . . 27

2.3.4 Pros and Cons of Interface Algorithms . . 32

2.3.5 Open issues in P-HIL simulation . . . . . . 32

2.3.6 Accuracy issue of P-HIL . . . . . . . . . . . 36

2.3.7 Procedure to conduct P-HIL simulation . . 37

ii application of p-hil in renewable energy

simulation 39

3 proposed real-time simulation architecture 41

3.1 Real-time Digital Simulator . . . . . . . . . . . . . 41

3.1.1 NI VeriStand . . . . . . . . . . . . . . . . . . 42

3.1.2 FPGA target . . . . . . . . . . . . . . . . . . 44

3.2 Interface algorithm using actual Measurement sys-tem . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4 modeling of pv and other systems under study 49

4.0.1 Solar cell characteristics . . . . . . . . . . . 49

4.0.2 Mathematical Modeling of PV in MATLAB-Simulink . . . . . . . . . . . . . . . . . . . . 52

4.1 MPPT System . . . . . . . . . . . . . . . . . . . . . 55

4.1.1 Perturbation and Observation Technique . 57

xi

xii contents

4.1.2 Boost Converter . . . . . . . . . . . . . . . . 58

4.1.3 Storage System . . . . . . . . . . . . . . . . 59

5 real-time simulation and results of pv us-ing fpga 61

5.1 Test-bench 1: PV and MPPT with the fixed Resis-tive load . . . . . . . . . . . . . . . . . . . . . . . . 61

5.2 Test-bench 2: PV with storage connected to DC Bus 66

5.2.1 Experiment . . . . . . . . . . . . . . . . . . 66

iii pv and micro-grid hil co-simulation hav-ing interface algorithm over ethernet 71

6 ethernet protocol for rt simulations 73

6.1 Need of interface algorithm over Ethernet . . . . . 73

6.2 Characteristics of the Real-time Ethernet . . . . . . 75

6.2.1 Real-time response . . . . . . . . . . . . . . 75

6.2.2 Synchronization . . . . . . . . . . . . . . . . 75

6.3 Real-time UDP Communication Protocol . . . . . 75

6.3.1 User Datagram Header format . . . . . . . 76

7 architecture of co-simulation platform 79

7.1 Real-time Digital Simulator . . . . . . . . . . . . . 79

7.1.1 Simulink Desktop Real-Time . . . . . . . . 79

7.2 LabVIEW RIO architecture . . . . . . . . . . . . . . 81

7.2.1 Architecture of the proposed test-bench . . 82

7.2.2 Model simulated in the test-bench . . . . . 83

7.3 Modeling of micro Grid and VSC converter . . . . 83

7.3.1 Non Linear model of hydraulic turbine sys-tem . . . . . . . . . . . . . . . . . . . . . . . 85

7.3.2 Governor system of Turbine . . . . . . . . . 88

7.3.3 Synchronous Machine . . . . . . . . . . . . 89

7.3.4 Turbine and generator relationship . . . . . 92

7.3.5 Excitation system model of synchronousgenerator . . . . . . . . . . . . . . . . . . . . 93

7.3.6 Control of 3φ Voltage Source Converter . . 95

8 pv and micro-grid hil co-simulation and re-sults 99

8.1 Real-time co-simulation test-bench . . . . . . . . . 99

8.2 Experiment and Results . . . . . . . . . . . . . . . 101

9 conclusion 107

9.1 Contributions to the Engineering Community . . 107

9.2 Recommendations and Future Research . . . . . . 108

10 appendix a 111

10.1 How to Create Custom FPGA bit file . . . . . . . . 111

contents xiii

10.1.1 Making a copy of the sample FPGA VIand project . . . . . . . . . . . . . . . . . . . 111

10.1.2 Customizing the FPGA VI . . . . . . . . . . 112

10.1.3 Compiling the Custom FPGA VI into aBitfile . . . . . . . . . . . . . . . . . . . . . . 113

11 appendix b 115

11.1 SLDRT Kernel Installation . . . . . . . . . . . . . . 115

11.2 Configuring Model . . . . . . . . . . . . . . . . . . 115

11.3 Code generation Parameters . . . . . . . . . . . . . 116

11.4 Signal logging to Workspace . . . . . . . . . . . . . 116

bibliography 117

L I S T O F F I G U R E S

Figure 1 Categories of Simulation based on the speedof execution . . . . . . . . . . . . . . . . . 8

Figure 2 Execution of steps in real-time and in nonreal-time simulation . . . . . . . . . . . . . 9

Figure 3 Simulation category according to the in-teraction among different modules un-der study . . . . . . . . . . . . . . . . . . . 10

Figure 4 Components of Hardware-in-the-loop sim-ulation . . . . . . . . . . . . . . . . . . . . . 13

Figure 5 Architecture of C-HIL simulation . . . . . 14

Figure 6 Architecture of P-HIL simulation . . . . . 15

Figure 7 Electrical drive framework . . . . . . . . . 16

Figure 8 DC Drive having a vehicle wheel as amechanical load . . . . . . . . . . . . . . . 17

Figure 9 Signal level HIL Simulation block diagram 19

Figure 10 Signal level HIL Simulation of DC drive . 19

Figure 11 Power level HIL Simulation block diagram 20

Figure 12 Power level HIL Simulation of Electricaldrive . . . . . . . . . . . . . . . . . . . . . . 20

Figure 13 Mechanical level HIL Simulation blockdiagram . . . . . . . . . . . . . . . . . . . . 21

Figure 14 Mechanical level HIL Simulation of Elec-trical drive . . . . . . . . . . . . . . . . . . 22

Figure 15 Voltage divider circuit . . . . . . . . . . . . 23

Figure 16 Architecture of P-HIL simulation consid-ering a voltage divider circuit . . . . . . . 24

Figure 17 P-HIL simulation interface done by cur-rent amplification . . . . . . . . . . . . . . 28

Figure 18 Ideal-transformer model method of in-terface algorithm . . . . . . . . . . . . . . 29

Figure 19 Scheme of TLM interface algorithm . . . . 29

Figure 20 TLM interface algorithm . . . . . . . . . . 30

Figure 21 PCD interface algorithm . . . . . . . . . . 31

Figure 22 DIM interface algorithm . . . . . . . . . . 31

Figure 23 Interface of Voltage divider circuit for sta-bility studies . . . . . . . . . . . . . . . . . 35

Figure 24 Architecture of VeriStand Engine deployedin RT Target . . . . . . . . . . . . . . . . . 43

xiv

List of Figures xv

Figure 25 VeriStand interface between PC and theRT Target . . . . . . . . . . . . . . . . . . . 44

Figure 26 Sequential procedure that is followed inReal-time execution . . . . . . . . . . . . . 45

Figure 27 Analog input ports of myRIO with ADC . 46

Figure 28 Solar cell equivalent electric circuit . . . . 49

Figure 29 Equivalent PV cell circuit used for mod-eling . . . . . . . . . . . . . . . . . . . . . . 52

Figure 30 Simulink model of the PV cell . . . . . . . 53

Figure 31 Current Characteristics of modeled PVmodule . . . . . . . . . . . . . . . . . . . . 54

Figure 32 Power of modeled PV array for differentirradiation and @ constant temperatureof 298.15K . . . . . . . . . . . . . . . . . . . 54

Figure 33 Power of modeled PV array for differenttemperature and constant irradiation . . . 55

Figure 34 PV with MPPT system connecting to load 56

Figure 35 Perturbation and Observation Techniqueflowchart . . . . . . . . . . . . . . . . . . . 58

Figure 36 Schematic diagram of Boost Converter . . 59

Figure 37 Generic battery model . . . . . . . . . . . 59

Figure 38 PV with MPPT system in myRIO . . . . . 61

Figure 39 Input and output voltage of the boost con-verter for change in irradiation from 1000W/m2

to 800W/m2 at 0.5s . . . . . . . . . . . . . 62

Figure 40 PV system model compiled for RT simu-lation . . . . . . . . . . . . . . . . . . . . . 63

Figure 41 Simulink model to be compiled for RTsimulation . . . . . . . . . . . . . . . . . . 64

Figure 42 Input and output Voltage of the boostconverter in RT Simulation for change inirradiation from 1000W/m2 to 800W/m2

at 0.5s . . . . . . . . . . . . . . . . . . . . . 64

Figure 43 Maximum Power tracked in real-time withthe output voltage maintained by MPPTsystem across the PV array terminals . . . 65

Figure 44 Simulation results comparison . . . . . . . 65

Figure 45 Block diagram of the test bench created . 66

Figure 46 Test-bench used for HIL simulation . . . . 67

Figure 47 Irradiation and temperature measured inreal-time . . . . . . . . . . . . . . . . . . . 68

Figure 48 Voltage measured across DC bus in real-time . . . . . . . . . . . . . . . . . . . . . . 68

xvi List of Figures

Figure 49 Voltage measured across DC bus usingoscilloscope . . . . . . . . . . . . . . . . . . 69

Figure 50 Power delivered by PV and consumed byload . . . . . . . . . . . . . . . . . . . . . . 69

Figure 51 SOC and the battery current . . . . . . . . 70

Figure 52 Battery terminal voltage . . . . . . . . . . 70

Figure 53 UDP Header format . . . . . . . . . . . . . 77

Figure 54 UDP Pseudo header format . . . . . . . . 77

Figure 55 Simulink desktop Real-time architecture . 81

Figure 56 LabVIEW RIO Architecture . . . . . . . . 81

Figure 57 Co-Simulation architecture used for HILsimulation . . . . . . . . . . . . . . . . . . 82

Figure 58 Block diagram of the simulated model . . 83

Figure 59 Block diagram of Hydroelectric power plantsystem . . . . . . . . . . . . . . . . . . . . . 85

Figure 60 Block diagram of Hydraulic turbine system 88

Figure 61 Block diagram of Hydraulic turbine gov-ernor . . . . . . . . . . . . . . . . . . . . . . 89

Figure 62 Block diagram of DC Exciter type 1 . . . . 94

Figure 63 Block diagram of Control of VSC . . . . . 97

Figure 64 Test-bench created for co-simulation . . . 99

Figure 65 LabVIEW VI for UDP transmission andreception in myRIO . . . . . . . . . . . . . 100

Figure 66 MATLAB-Simulink model compiled foruse in SLDRT . . . . . . . . . . . . . . . . . 101

Figure 67 Power delivered by PV system in boththe simulations . . . . . . . . . . . . . . . . 102

Figure 68 Power of PV system at 18th s . . . . . . . . 103

Figure 69 Frequency of the grid in per unit . . . . . 104

Figure 70 Voltage at PCC in per unit . . . . . . . . . 105

Figure 71 Power delivered by Synchronous gener-ator to grid . . . . . . . . . . . . . . . . . . 105

Figure 72 Reactive power delivered by PV systemto grid . . . . . . . . . . . . . . . . . . . . . 106

L I S T O F TA B L E S

Table 1 Pros and Cons of Interface algorithm . . . 34

Table 2 Available communication protocols . . . . 74

Table 3 Excitation System . . . . . . . . . . . . . . 97

Table 4 Parameters of Synchronous Machine . . . 98

Table 5 Mechanical Driving System . . . . . . . . 98

xvii

A C R O N Y M S

ADC Analog To Digital Converter

C-HIL Controller Hardware In The Loop

DAC Digital To Analog Converter

etc Et Cetera

FIFO First In First Out

FPGA Filed Programmable Gate Array

GUI Graphical User Interface

HIL Hardware In The Loop

HUT Hardware Under Test

HMI Human Machine Interface

MPPT Maximum Power Point Tracking

P-HIL Power Hardware In The Loop

PCC Point of Common Connection

RIO Re-configurable Input Output

ROS Rest of The System

RT Real-time

RTDS Real-time Digital Simulator

SG Synchronous Generator

SLDRT Simulink Desktop Real-Time

SOC State of The Charge

UDP Unigram Data Protocol

VSC Voltage Source Converter

VSS Virtually Simulated System

V2G Vehicle To Grid

xviii

1I N T R O D U C T I O N

In this chapter I have taken an opportunity to convey my ideasand motivation for thesis work being done on Hardware In theLoop (HIL) simulation studies of renewable energy, by takingcase of photovoltaic (PV) system, to demonstrate the platformand to solve the problems of simulating complex mathematicalmodels in real-time.

1.1 motivation

Entire human population of this era, is in the quest of ’Se-cure, Clean and Efficient Energy’. It is one of the big societalchallenge that is being addressed by most of the world orga-nizations and the governments. To name one, Horizon 2020 isthe biggest EU Research and Innovation programme ever withnearly €80 billion of funding available over 7 years (2014 to2020) [1], in which the above mentioned problem of energy isone of the societal challenge addressed through this project byEuropean Union.

Increase in energy demand, the constraint of the present in-frastructure to fully exploit the conventional energy source andalso environmental concern has made us look at PV cell to har-ness solar energy.

A PV system is mainly used for,

1. Bulk production of electrical energy to meet the existingenergy demand as an alternative supply.

2. Satellites, space crafts and in other aero-space applica-tions to harness solar energy in space.

3. Electric vehicles as an hybrid configuration, but not sopopular and useful.

A great number of research work is being conducted to bringdown PV unit cost and to increase the efficiency of the PV mod-ules. As a result, today we are able to get upto 27% efficientsolar cells [43] which are remarkable.

1

2 introduction

PV delivers lot of energy in the afternoon, while the peakenergy demand is in the morning and evening, hence storagesystem is very important. But the storage system takes much ofthe investment and requires maintenance [17]. Instead of hav-ing PV on top of electric vehicles, batteries designed for electricvehicles are used for storing excess energy from the grid, and itis exchanged back when it’s in need. This technology is calledas Vehicle to grid (V2G) [20], a ground breaking concept that isin much of interest by the research community.

These upcoming technologies are very promising for mankindto live in a sustainable world. Simulation studies of PV for gridinteraction, storage and V2G brings faster implementation oftechnology from paper to people. As many of the countries areproposing solar power projects, especially developing countrieslike China and India, a low cost platform to conduct these stud-ies are much appreciated.

1.2 need of real-time pv simulations

As penetration of PV generation increases, it’s impact on stabil-ity and and security of the power system will become more andmore significant, due to the characteristic of randomness andvolatility [31]. Modeling and simulation are the basic technolo-gies to study the impact for the power grid in which, large-scalePV generation systems are integrated.

Simulations in usual platform may give good results but theyare not able to deliver results for dynamic change in input aspresent in real-world in run-time, the model may not respondfor such a change. When we try to simulate to know the longterm performance of a system, the normal simulation requires avery long time to deliver results and the accuracy of the resultsmay also get compromised. Hence it is necessary to conductreal-time simulation with the models that can respond for fasterinput dynamics [32].

The power generation capability of the PV depends on theever-changing environmental conditions like temperature andsolar irradiation, hence real-time simulation of PV system to-gether with its controller is recommended to validate the con-trol aspects and also to study the behavioral aspects of the sys-tem under different circumstances resulting from external orinternal dynamic influence.

’Hardware In the Loop’ is the state of the art simulation thatprovides the solution for the above requirement, where a sys-

1.3 problem formulation 3

tem behaviour is emulated in a hardware and tested in real-time according to the requirement.

1.3 problem formulation

While simulating the complex model like PV system interactionwith the grid in real-time, we may encounter many problems.The important ones to mention are,

1. The need of a PV mathematical model that can deliverresults faster to keep the real-time simulation propertiesduring execution. Solving the algebraic loop in the PVmodel is an important task as algebraic loops are not sup-ported in the real-time hardwares.

2. There is a need of cost-effective test bench/platform forsimulating PV systems in real-time that can be used forcontrol validation, studies of storage system and integra-tion of PV system to the power drive train or grid.

3. Model based design of process and systems are very pop-ular, there are tools available for automatic code genera-tion for the developed model, it’s required to use thesetools, that can deliver C code from the model, which canbe used for cost effective target hardwares.

4. The memory of the real-time digital Simulator (RTDS) isa main constraint while simulating a complex model likegrid, this memory is used for storing and executing thecomplied C code in real-time. It may be necessary to splitthe model into two or more separate systems and bridgethem using an appropriate interface.

5. Interfacing the two models using respective interfacing al-gorithm introduces some errors in the execution, that re-sults in, instability of the system during run time and alsoaccuracy of the results varies according to the interfacingalgorithm used.

1.4 research objectives

As explained earlier the main objective of this work is to pro-pose the low-cost real-time simulation platforms, that can be

4 introduction

used for real-time simulations, incorporating HIL testing method-ologies using hardware. The following objectives are framed tomeet in this research work.

1. To create a Mathematical model of PV system that can beused for real-time simulation, which has faster convergingbehaviour that keeps the execution in real-time.

2. To create a test bench for validating the control or theprocess validation of the PV system.

3. To use the real world data in run-time of the simulation.

4. To create a co-simulation platform for emulating PV ina hardware and complex model like grid as rest of thesystem in the Simulink Desktop real-time.

1.5 thesis outline

The thesis is being divided into three parts, Part I containsChapter 2, which presents the detailed study of HIL simula-tion by presenting examples and case studies. The need andtypes of interface algorithms are studied. Also about maintain-ing stability and accuracy during the execution in run-time arediscussed.

Part II contains three Chapters, in Chapter 3 the proposedarchitecture for real-time simulation using VeriStand as real-time digital simulator and myRIO as hardware is presented.Chapter 4 presents the detailed modelling of PV, MPPT, DC-DCConverter, etc. Later in Chapter 5 the results of HIL real-timesimulation is illustrated with the test bench created.

Part III has four chapters, in Chapter 6 the Ethernet pro-tocol that are being used for data communications are men-tioned and detailed explanation is given on UDP protocol, inChapter 7 the architecture of proposed test bench for HIL co-simulation having interface algorithm over Ethernet is beingpresented. The Chapter 8 deals with the created test-bench andthe execution of real-time experiment along with the discussionof results. Finally the conclusion of this work is drawn in Chap-ter 9.

Part I

T H E O R E T I C A L A S P E C T S O F H I L

In this part the detailed study of Hardware-in-the-loop simulation is presented. It is very essential tounderstand the basic ideology of this type of simu-lation methods for the development of the PV testbench for different test case scenarios. The majorproblem in executing HIL simulation is, having thesystem states stable throughout the simulation andalso to maintain accuracy without affecting the char-acteristics of the emulated system. In my case theemulated system is PV array whose characteristicsdepends on the series and parallel resistances, whichcan be affected by introducing the interfacing algo-rithm of HIL simulation. The key points that has tobe understood for successful execution of HIL simu-lation is given in this part.

2H A R D WA R E - I N - T H E - L O O P F O R P O W E RE L E C T R I C A L S Y S T E M S

This chapter will light on the facts of simulation, its categoriesand need of different kind of simulation techniques. It alsonarrates, state of the art real-time simulation, Hardware-in-the-loop, Power-hardware-in-the-loop, their methods and issues. Mymain goal in this work is,

1. To present a real-time simulation framework coupling mod-elling environment such as MATLAB Simulink to a real-time hardware, in this work National Instruments myRIOis chosen as the real-time hardware which is being ex-plained in the later section.

2. To conduct Co-simulation in real-time, incorporating Hard-ware in the Loop simulation strategy for simulating PVsystem and grid whose mathematical models are inter-faced through Ethernet.

HIL is widely used for testing in automotive industries, ma-rine and aerospace applications etc., but nowadays it is gain-ing much popularity in real-time testing in Electrical powerdomain, especially in renewable energy planning, testing andcommissioning. Though HIL has much benefits, it is still aemerging topic in the field of research, hence the detailed studyof HIL simulation is given in this chapter.

2.1 simulation

The development of many products and the process is charac-terized by the integration with digital control systems. The in-tegration is performed by the hardware and the software com-ponents. Because of the expanding multifaceted nature and themutual relationship between the design of the process and con-trol system, computer aided techniques for modeling, simula-tion and furthermore the design methods are required. Thereare many tools available in the market to address these needs.

Thus, a faster way to validate research proposals pertainingto the above-mentioned characteristics is by adopting simula-

7

8 hardware-in-the-loop for power electrical systems

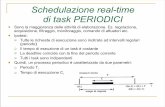

tion techniques. With respect to the required speed of the com-putation, the simulation can be grouped into three categories[19].

1. Simulation without time limitation

2. Real-time Simulation

3. Simulation faster than real-time

In simulation without any time restrictions, the results arenot forced to be available at particular time instances. A degreeof freedom with respect to the execution time is given for thesimulator to solve the equation and to continue the iterationfor the specified time. Whereas in real-time simulation, the ex-ecution time is as same as real world clock. The equations areforced to deliver the output at particular time instances and theiterations of model equations are done while interacting withoutside world in real-time. The simulation faster than real-timeprovides the solution of the equations as it is immediately avail-able after processing which enables to monitor faster dynamicsof the real world.The three categories and their brief usage is represented in Fig-ure 1.

Figure 1: Categories of Simulation based on the speed of execution

2.1.1 Real-time Simulation

Real-time simulation means not only fast computing, its task isto control or react to the events that take place in real worldwith the clock speed same as that of the real-world clock [26].

2.1 simulation 9

Digital real-time simulation (DRTS) of the electric power sys-tem is the reproduction of voltage or current waveforms withthe desired accuracy, that are representative of the behavior ofthe real power system being modeled.

To achieve such a goal, a digital real-time simulator needs tosolve the model equations for one time-step within the sametime in real-world clock [15]. Therefore, it produces outputs atdiscrete time intervals, where the system states are computedat certain discrete times using a fixed time-step.

Two situations can arise depending on the time required bythe simulation platform to complete the computation of stateoutputs for each time-step, if the execution time Ts for the simu-lation of the system is shorter or equal to the selected time-step,the simulation is considered to be real-time, it is shown in theFigure 2.

Figure 2: Execution of steps in real-time and in non real-time simula-tion

In the first execution step the model gives the solution exactlyat same time of the real world clock tn but the second executionstep results the solution faster than next clock step Tn+1, butin this case the real-time property is maintained by making themodel to wait, until reaching the next clock step Tn+1. This waittime is called as idle time and solution is made available exactlyat real-time. In the next case it is illustrated in the figure thatthe first execution step takes little longer than Tn+1.

In the later case the simulation will miss a step of executionwhere this phenomena is called as overrun. The occurrence ofoverrun in the simulation makes the model to loose the prop-erty of real-time.

A simulated system will provide a dynamic output subject toits particular simulation time-step, which can be faster/slowerthan the real-life system’s dynamics. Therefore, ensuring RT

10 hardware-in-the-loop for power electrical systems

is not a matter of accelerating or slowing the simulation, butproviding valid outputs at precise (reality-consistent) instants.Having an early or a delayed result makes the simulation failas it no longer captures the real dynamics of the system.

2.1.1.1 On-line and Off-line Simulation

Another significant subdivision among simulation technologiesis, whether they keep running on-line or off-line. This charac-teristic is a determinant for setting up the abilities of the simu-lation framework and their scope as shown in the Figure 3. Thereason for the real-time requirement is mostly that one part ofthe investigated system is not simulated, but real. A processcan be understood as a series of steps along a sequential “line”of events. The implication of on-line alludes to the considera-tion of the simulation in between the process, so performingthe tasks of a certain step.

Figure 3: Simulation category according to the interaction among dif-ferent modules under study

Those system under study ordinarily incorporate the associ-ation with the rest of the sub-process. Therefore input/outputexchange is necessary.

Off-line simulation can adapt to systems that require no in-teraction with different sub processes either in light of the factthat the entire framework is simulated or such communicationis incorporated artificially. e. g., infusing recorded data from theprocess during runtime of the simulation.

Briefly, on-line simulation influences the modeled sub-systemto some portion of the full process as it runs, while off-line sim-ulation runs independently. Both methodologies can adapt tohuman intercession so as to modify set-points or parameters; be

2.1 simulation 11

that as it may, such human interaction yields on-line behavioronly if it is an actual sub-process in the previously mentionedline of events i. e., when it can’t be infused by programmedinfusion of the data.

On-line simulations can only be run if real-time propertiesare ensured, as the surrounding events react under real worldclock timing. In this way, the simulation copes with the dy-namic behavior and the input/output characteristics of the sim-ulated sub-process. Effective on-line simulation will be usefulfor detailed analyses as the collected data will depict close-to-real process behavior. In this way, bandwidth, precision, gainsand limits, as well as stability, sensitivity, noise rejection, out-put effort, etc., can be studied due to dynamical consistencyand minimized assumptions.

It is worth mentioning that real-time off-line simulations arepossible. As long as the deterministic simulation deadlines aremet effectively, hence in the Figure 3 the real-time simulation isconnected to off-line simulation methodology in a dotted line.The RT simulation can be guaranteed on an independent envi-ronment. However, it has no input/output interaction with thereal world exists in this case.

2.1.1.2 In-the-loop Simulation

Whenever a process is cyclical, a “loop” instead of a line definesthe system’s flow. Having any in-the-loop sub-process impliesthe same on-line integration with the surrounding system. TheIn-the-Loop (IL) notation is used to denote such an interactiontogether with the specific system being added to the main pro-cess. Numerous simulation strategies are accessible to addressthe issues of the framework outlined [28]. They are, model-in-the-loop (MIL), software-in-the-loop (SIL), processor- in-the-loop (PIL), hardware- in-the-loop (HIL) and power-hardware-in-the-loop (P-HIL). They directly refer to the specific technolo-gies used and their supported interactions. Brief narration oneach of the In-the-loop simulation techniques are as follows.

1. Model-in-the-loop: Controller and the plant are simulatedin the host computer without any real hardware compo-nents.

2. Software-in-the-loop: Simulated plant is run with the sim-ulated control in the host computer

12 hardware-in-the-loop for power electrical systems

3. Processor-in-the-loop: Plant/control runs in a digital plat-form (Micro-controller/DSP/FPGA) and the controller orplant runs in the host computer.

4. Hardware- in-the-loop: Process in which a plant, synthe-sized in a compiled code, runs in digital platform and in-teracts in real-time with a physical controller. In this tech-nique the simulated process in the external digital plat-form and is operated with the real control hardware.

As shown in Figure 3 HIL and simulation techniques based onHIL require real-time conditions to be met, as actual real worldsignals or power interactions are used as the interface.

Summarizing, a simple non-real-time simulation will wait forall results to be ready after performing the required ordinarydifferential equation (ODE) solver operations. This will gener-ally take a long time to be processed and will give "ideal" dis-crete results. Real-time simulation powers the process to fit intoa deterministic time-step, so showing the real-time qualities ofthe system. Real-time results are closer to reality since all pro-cessing modules are demanded to react for changes at the rele-vant time scale.

Finally, HIL incorporates the actual hardware solution to beimplemented. Consequently, the real-time model accounts forthose cases at the appropriate time scale to which the Hardware-under-Test (HUT) is to be subjected.

2.2 hardware-in-the-loop

The hardware- in-the-loop simulation (HIL) is characterized byoperating real components in connection with real-time emu-lated components. Usually, the control system hardware andsoftware are the real system, as they are used in production.The controlled process consists of actuators, where as plant/-physical process and sensors are emulated or some parts of itare real. Consider this example of ‘Soyuz Simulator’ to train as-tronauts. In this case the astronaut is subject under test whereas the flight behaviors are emulated, the controllers and the ac-tuators are real. A HIL framework composed of three crucialparts, a hardware under test (HUT), a virtually simulated sys-tem (VSS) and an interface that connects both HUT and VSS.

Figure 4 gives practical example of HIL simulation. In thiscase, the simulator mimics a virtual environment of dockingand re-entry that is continuously changing according to the

2.2 hardware-in-the-loop 13

Figure 4: Components of Hardware-in-the-loop simulation

hardware’s (the human pilot) reaction. When the pilot receivesthe vision through the monitors, he makes real-time decisionsand sends the commands back to the simulator using controlswitch or other input tools. The display screen, human eyes,and the control switch comprises the HIL interface.

One of the flourishing area of HIL is rapid control prototyp-ing. In this case, the real embedded controller is tested withthe emulated plant, the HUT is subjected to ability of the real-time digital simulator to integrate complex dynamical systemsmany simple and complex dynamical system are emulated andused for control prototyping. As an example, HIL platform forprototyping and testing of wind generator controllers are pre-sented in the paper [34]. In this, author described a 10-turbinewind farm that is connected a single feeder, which is emulatedin real-time simulator. One of the wind turbine is controlled us-ing an externally emulated wind turbine controller having theinterface using analog and fast digital inputs and outputs inreal-time.

Another example for product prototyping using HIL is sim-ulation of Hybrid electric vehicle for the evaluation of differ-ent characteristics. Authors in the paper [30] are evaluating thecharacteristics of the motor when it is installed in the vehicleand used in different terrains and driving mode. They proposea model in which they will have a vehicle simulator, a controllerand the dynamo-meter. Here dynamo-meter is the real-worldsystem used to create vehicle dynamics and it is also the sys-tem under test. The vehicle simulator consists of all the actualvehicle information and its dynamic characteristics. The PI con-troller used in real-time gathers the information from the ve-hicle dynamics and actual motor speed and it commands themotor which is under test to perform accordingly.

HIL simulation is categorized into two groups

1. Controller-hardware-in-the-loop (C-HIL)

14 hardware-in-the-loop for power electrical systems

2. Power-hardware-in the-loop (P-HIL)

2.2.0.1 Controller-HIL and Power-HIL

Most of the rapid control prototyping HIL applications exchangethe signals between the simulator and the HUT are at lowpower levels typically in the voltage range of ±12V and theycan easily interact with the real world using analog to digitalconverter or vice versa with good accuracy and no power ex-change takes place between the simulator and the HUT, thistype of HIL testing is called as C-HIL.

Figure 5 shows the basic architecture of Controller-hardware-in-the-loop. In this type of simulation only signals are exchangedbetween the real-time digital simulator (RTDS) and the hard-ware under test. Usually the electronic control unit is subjectedto the hardware under test which receives the forward signalsof the process/plant emulated in RTDS. The forward signal-s/feedback signals generated in the RTDS will undergo digi-tal to analog conversion to feed the pseudo measurements ofprocess/plant to the controller. The controller interprets thispseudo measurement signals as real world signals. After it pro-cessing the information, it generates the control signal that isfed to RTDS through a analog to digital converter to behaveaccording to the instructions obtained by HUT.

Figure 5: Architecture of C-HIL simulation

Whereas in many cases, there is a need of exchanging powerbetween the simulator and the HUT (example Electric vehiclemotor as HUT) and the simulator should be able to address

2.2 hardware-in-the-loop 15

this request. The HUT may absorb the real power henceforthacting as a sink, it can be handled by incorporating appropriatepower amplification and conversion apparatus and this kind ofHIL testing is called as P-HIL simulation, the basic architectureof P-HIL simulation is as given in Figure 6.

In this simulation methodology the hardware that absorbsthe real power, is subjected to be the HUT. The RTDS comeswith real-time model emulated in it along with the human ma-chine interface to control the simulation process. The emulatedmodel will generate the forward signals which will go underdigital to analog conversion. These signals are amplified to thepower level using a power amplifier. There by providing thereal power to HUT, as if it is working in the real world scenario.

The HUT will react to the power obtained and it behavesaccordingly in the real world. The measurements of the HUTis taken using appropriate sensors and they are fed to RTDSthrough ADC’s which are received as feedback signals for themodel emulated in the RTDS. To the obtained forward signalsthe model emulated in the RTDS will act and generate neces-sary forward signal and this process repeats in the simulationas it progress with respect to time. The power amplifier andthe sensors used for measurements together forms the powerinterface between the emulated system and the HUT.

Figure 6: Architecture of P-HIL simulation

16 hardware-in-the-loop for power electrical systems

2.2.1 Different HIL methodologies for Electric drive system

To know the different HIL methodologies that can be imple-mented in electrical domain, I introduce an example of Electricdrive system given in the paper [10], the author has given thedistinctive techniques for directing HIL simulation for electricdrives. In which he clarifies the interfaces and the strategies togo from signal level to mechanical level of integration.

An electrical drive can be defined as an electro-mechanicaldevice for converting electrical energy into mechanical energyto impart motion to different machines and mechanisms forvarious kinds of process control [27].

Figure 7: Electrical drive framework

The electric drive framework incorporates the following seg-ments in it. Power modulator, Sources, Control unit, Sensingunit, Electrical machines and loads. The control unit holds theprocess control where it gathers the information from the avail-able sensors and as per the requirement it yields the pulses forthe power electronic switches present in the power modulatorwhich interface the source and the electrical machine. The elec-trical drive framework is represented in the Figure 7.

The type of control unit selected depends on the dynamicsof the process control, if it involves faster dynamics then high-speed devices called FPGA are used to control the faster dy-namics and to reach high frequency modulation of the powerelectronic converter. A complete model of DC drive is shown inthe below Figure 8.

The illustrated DC drive model contains a battery source Vsthat provides the required voltage and delivers the current is tothe IGBT power converter, the motor terminals are connectedto the power converter whose output voltage is given by the ex-pression Vo and the load current is given by im. The rated speedof motor is Wm rad/s and the torque generated is Tm which iscoupled to the wheel of the vehicle through a transmission gear

2.2 hardware-in-the-loop 17

Figure 8: DC Drive having a vehicle wheel as a mechanical load

box Wg is the speed of the vehicle in rad/s and Tg is torque ofthe vehicle in Nm. The battery voltage measurement Vs, loadcurrent im and the desired output torque of the wheel Tgref isgiven to the controller which produces the gate pulses for theIGBT switches for power regulation.

2.2.1.1 Mathematical model of the selected DC drive system

The chopper converts the input source voltage Vs to the outputvoltage Vo as per the duty cycle ’D’ applied by the controller. Bythis also the source current is and the load current im is relatedas shown below.

Vo = Vs ∗Dis = im ∗D

(1)

Where D is the modulation index of the chopper.The DC machine characteristics can be described using volt-

age applied on the armature winding, the armature current pro-duced and the back EMF generated and it is given by,

Ldiadt

= ia ∗ Ra − Eemf − Vo (2)

where, L and R are motor inductance in H and resistance in Ωrespectively.

18 hardware-in-the-loop for power electrical systems

The torque of the DC machine is is proportional to the arma-ture current ia and the EMF generated if proportional to thespeed of the machine Wm.

Tm = ka ∗ iaEemf = ka ∗Wm

(3)

where, Ka is the torque co-efficient.Gearbox gives the torque Tg and the speed of the wheel Wg

from the machine torque and the machine speed using the gearratio kg.

Tg = kg ∗ TmWm = kg ∗Wg

(4)

The wheel converts the rotational motion Wg to the linearmotion Vspeed and also the obtain torque Tg to the traction forceFtract using the wheel radius Rwheel.

Ftract =Tg

Rwheel

Wg =Vspeed

Rwheel

(5)

Vehicle speed is obtained by equation of vehicle dynamicsrelation with traction force Ft and resistant force Fres.

MdVspeed

dt= Ftract − Fres (6)

where, M is the mass of the vehicle including the rotating mass.The resistant force Fres is calculated using the relation,

Fres = Fo +αVspeed + bV2speed +M ∗ g ∗ sin(θ) (7)

where, Fo is the frictional force, α is the friction co-efficient, bis the drag co-efficient,θ is the slope angle to the horizontalsurface and g is acceleration due to gravity.

2.2.1.2 Signal level HIL Simulation

In signal level of HIL simulation, only the control hardwarethat holds the process control is tested. The other parts such aspower modulator, electrical machine and the mechanical loadare simulated in real-time. The simulation should be able to ex-change the signals between the controller (HUT) and simulated

2.2 hardware-in-the-loop 19

Figure 9: Signal level HIL Simulation block diagram

model, hence the simulated model is emulated in another con-troller board which can provide the signal characteristics of thepower parts in the system.

A specific signal conditioning is being adapted to impose thesame input and output of the power parts. This method of HILis called as “signal level HIL simulation” because only signalsare used as the interface between the HUT and the simulatedsystem.

Figure 10: Signal level HIL Simulation of DC drive

Equation 1 to Equation 6 are modeled and emulated in a DSPfor real-time simulation.The measurement parameters such assource voltage Vs and armature current im are sampled to feedthem as pseudo variables. These variables can be gathered dur-ing the measurement using sensors in real world but now it isbeing simulated. The DSP is also emulating the behavior of thepower modulator hence the step size of DSP is much smallerwhen compared to the controller HUT, the overall configura-tion is shown in the Figure 10.

20 hardware-in-the-loop for power electrical systems

2.2.1.3 Power level HIL Simulation

In this case actual controller board and the power electronicsconverter are evaluated, the other parts of the drive are simu-lated. The simulation will impose the inputs and outputs onthe power electronic converter and the controller under test. Inthis method the simulation environment is composed of sec-ond power converter and a second controller to simulate thesame dynamics of the motor, Figure 11 shows above describedconfiguration.

Figure 11: Power level HIL Simulation block diagram

The DC machine behavior is mimicked by connecting thepower modulator under test to another chopper in series withan inductor as shown in the Figure 12.

Figure 12: Power level HIL Simulation of Electrical drive

Equation 2 to Equation 6 are being simulated in the DSP inreal-time. The second chopper modulation ratio Demu is calcu-lated and converted into gate pulses by selecting proper switch-ing frequency so that the same current im is imposed throughthe inductor as given by the DC motor Equation 2. In this typeof simulation the machine characteristics is emulated by em-ploying the current control loop in the real-time simulator. Se-lecting the proper chopping frequency to allow the current in

2.2 hardware-in-the-loop 21

the continues conduction mode and the time constant of theinductive circuit is a key for correct emulation of the machinecharacteristics. This kind of HIL simulation helps to test thechopper influence (EMC on control) and unwavering quality,real battery execution when it is incorporated with the vehicleand in like manner tests.

2.2.1.4 Mechanical level HIL Simulation

In Mechanical level HIL Simulation1, the whole drive i. e., con-trol, power electronic converter and the DC machine is testedusing a simulated mechanical load. The simulation must ex-change the mechanical inputs and outputs with the electricalmachine under test. To simulate the load behavior another elec-trical machine is used as controlled mechanical load, it is sup-plied by the second power electronic converter and also the sec-ond controller which is running in real-time, the block diagramof the mentioned architecture is given in the Figure 13.

Figure 13: Mechanical level HIL Simulation block diagram

The second controller should control the mechanical load aswell as it should send the fictitious mechanical measurementsto the controller under test. The interface between the real andsimulated terms are composed of mechanical variables.

When this type of the HIL testing is employed in the electricalvehicle DC drive, it provides the static test bench for testing andproduct prototyping.

To simulate the behavior of the mechanical power train, theDC machine is connected to another electric machine (Induc-tion motor) which is powered by a power converter as shownin the Figure 14. The DSP controller board simulates the Equa-tion 4 to Equation 6 in real-time and the inverter modulationvector Demu is calculated to impose the same speed of rotation

1 This is the method proposed by the author in the work [10], though thiskind of simulation is not exactly classified classified as Mechanical-HIL butit usually referred as Power-HIL.

22 hardware-in-the-loop for power electrical systems

of Wg to the gear transmission. In this method a closed speedcontrol loop is needed to emulate the behavior of the vehicle.Using this type of test the effect of power electronics on torqueand the machine limitation can be easily tested

Figure 14: Mechanical level HIL Simulation of Electrical drive

2.3 power-hardware-in-the-loop

P-HIL is becoming progressively well-known because of theaccentuation on not endangering power systems, power elec-tronics, and other associated electrical apparatuses before com-missioning these devices in the actual systems. As already dis-cussed, the whole P-HIL simulation system design is based onthe hybrid configuration of computer simulation of part of thesystem, known as the “rest of system” (ROS), in real time, thecontrol and measurement of the hardware under test (HUT)that is connected to that real-time simulation and on their inter-facing through digital and analog input/output signals. A fun-damental component of the P-HIL approach is the closed-loopnature of the interfaces, allowing two-way interaction betweenthe HUT and the virtual simulated system (VSS).

When a subsystem module/device of a large system to bedeployed, it is highly recommended to do P-HIL test makingthe device that has to be tested as HUT and the large systememulated in the RTDS at an early development stage. It enablesto know the system level interactions and possible to mitigatethe issues if present. Further, for systems that have not yet beenfully realized, development schedules for various componentsof the system may differ substantially, preventing componentsdeveloped early in the cycle to be tested with other componentsof the system until later in the development cycle. In this case,P-HIL simulation offers a way to perform integration testing of

2.3 power-hardware-in-the-loop 23

the HUT at an early stage, making use of models of the othercomponents in the system.

P-HIL experiments can be conducted in a tightly controlledlab environment in which experiments can be quickly and grace-fully terminated, P-HIL simulation provides a means to test theHUT for extreme or dangerous conditions that would not be at-tempted with a fully hardware-based test bed of the surround-ing system.

Though it has so much advantages, this methodology is oftenforgotten in the scientific community, hence a less number of re-search work is being carried in this area. Due to advancementin digital dives like FPGA and immediate need of addressingenergy issues using renewable sources. P-HIL tests are gainingmore emphasis in this regard for design, project evaluation andtesting of integration of renewable energy source with the gridsimulation for worst case scenarios. P-HIL is a safe risk reduc-ing method that is extremely applicable because it provides amore realistic environment than software simulation alone.

2.3.1 Basic architecture of P-HIL simulation

Consider a primitive voltage divider circuit as shown in theFigure 15, it is composed of a voltage source Vo, source resistorR1 and the load resistor R2.

Figure 15: Voltage divider circuit

The source voltage connection with the resistors closes thecircuit and makes the current i1 to flow through them andthe voltage V1 is observed across R2. Now if we like to makethe load resistance as HUT and the voltage source along withits source resistance is simulated in real-time in a RTDS, weshall implement this basic architecture of P-HIL as shown inFigure 16.

The idea is the component to be tested is replaced by a cur-rent source or a voltage source in the simulated model whereas the component is imposed with the real voltage or current

24 hardware-in-the-loop for power electrical systems

Figure 16: Architecture of P-HIL simulation considering a voltage di-vider circuit

source as same as the magnitude as in the simulated system.In the source side, the resistor R2 is replaced by a controlledcurrent source in the model developed and the voltage acrossthe current source is calculated in simulation. The calculatedvoltage V1 obtained in the simulated system is applied to theterminals of the actual hardware through a power interface, thiscreates the virtual voltage V1 to be the real world actual voltageV

′1, ideally these two voltage are same i. e., V1 = V

′1. The current

measured from the hardware circuit i1 is sent back to the sim-ulated model running in RTDS as a feedback signal, model inthe RTDS incorporates this feedback signal as the actual currentflowing in the circuit.

This method shows the possible setup of power interface inP-HIL system, as there are many interfacing methods are avail-able. The principle of this real-time simulation implies that theelectrical signals of the physical power system (i.e., current andvoltage) are identically replicated by the RTDS [15]. The simu-lators used and integrated in P-HIL simulations must be ableto solve the differential equations of the corresponding powersystem within the defined time step, and this requirement mustbe fulfilled all the time.

2.3.2 Real-time digital simulator and Interface in P-HIL simulation

To conduct a P-HIL-based experiment, several things are takencare and issues are addressed. Among them the most importantare,

1. Real-time digital simulator

2.3 power-hardware-in-the-loop 25

2. Power amplifier

3. Interface

2.3.2.1 Real-time digital simulator

RTDS plays a major role in entire P-HIL simulation because ofthe model emulated is controlled by RTDS and it is only respon-sible for keeping the simulation in real-time. A wide variety ofreal-time digital simulators are available in the market. Somereal-time engines cater more toward bulk power applicationsand thus, form a P-HIL standpoint. It is also a software bridgebetween the emulated model in the target device and human,it provides the HMI between the tester and the real-time target.

The selection of the target device is based on many factors,but one importantly is the computing capability of it. To modelthe high switching characteristics of converters, a fast processoris needed to reach the minimum step size as low as 1µs. A real-time simulator needs to solve a grid-scale model by roughly50µs or a smaller time-step, a simulation of such a system mayrequire more computing capability and the ability to simulatewith a very small time-step. From a hard ware architecturalpoint of view, the RTDS can be grouped into the following cat-egories.

• PC based

• Custom processor based

• Supercomputer based

• FPGA based

The PC-based RTDS uses general-purpose multi core proces-sors that run on RT-Linux and execute real-time code gener-ated from the system model with optimized solvers. Custom-processor-based RTDS are based on RISC processors runningon VxWorks RT-OS and its user interface. Supercomputer-basedRTDSs are based on machines with large computational plat-form and the last one uses FPGAs as the main computationalhardware that is used for both large-scale and small-scale sim-ulation activities. Simulation on FPGA is a good solution toachieve the custom performance. However, the coding of com-plex solvers for FPGA is still very complex and often requireslow-level FPGA programming expertise.

26 hardware-in-the-loop for power electrical systems

Most of the RTDS comes with the application software wherean inbuilt library providing GUI to do build model by dragand drop, also they provide a platform to build custom modelusing C code or any other tool. The application software holdsthe solver methodology to solve the model as well. Most promi-nently usage of MATLAB model gives an easy development en-vironment. As, a well-defined libraries enables user to cut thedevelopment time, but very less RTDS support this facility.

2.3.2.2 Power amplifiers

As P-HIL experiments involve the transfer of power throughthe interface, an amplifier is needed to reproduce simulatedconditions at the point of common coupling with the HUT.In P-HIL-based experiments, it is typically desired to test theelectrical apparatus at its intended power rating and dynamicevents may further require voltages and currents more thanthe rated values for limited duration. Thus, it is required toutilize an amplifier that is sized appropriately for the task andthat additionally has a bandwidth that can conduct the planneddynamic tests. Also, considerations that must be taken care in-cludes slew rate limiting due to bandwidth limitations as wellas quantization error in voltage/current synthesis.

It’s the task of the engineer who is testing to select appropri-ate power amplifier according to his testing needs. The guideto select proper power amplifier is given in [24] in this paperthey suggest three types of power amplifiers addressing differ-ent needs. They are,

1. Switched mode power amplifier: Switched-mode ampli-fiers are commonly used for P-HIL simulation rangingfrom small-scale power applications up to the megawattrange. Typical AC/DC/AC converter typologies consist-ing of front-end rectifier and back-end inverter is used inthis method. Based on type of P-HIL experiment, controlstrategy of the amplifier, switching frequency and the out-put filters are selected.

2. Linear power amplifiers: They are most suitable for P-HILapplications in the small to medium power scale.

3. Generator-type power amplifiers: This type of amplifica-tion employs a three-phase synchronous generator drivenby a DC or AC motor and separate exciter systems.

2.3 power-hardware-in-the-loop 27

The following characteristics must also be carefully consid-ered to select the amplifier for the P-HIL application.

• Power ratings of the device under test

• Amplifier interface connections

• Source and sink power ratings of the amplifier

• Amplifier response times

• Amplifier slew rate

• Amplifier harmonic distortion and frequency resolution

• Amplifier input and output voltage/current range

• Amplifier input and output impudence

2.3.2.3 Interface

Interfacing the RTDS with the HUT holds an important task inP-HIL simulation. Type of interface will decide the stability andaccuracy of the simulation, selecting the proper interfacing al-gorithm is the key to get accurate results and meeting the goalsof the P-HIL simulation. Many types of interface algorithms areavailable and it’s being explained in detail in the next section.

2.3.3 Interface Algorithm

Interface algorithms provide the means of relating simulatedvoltage and currents at the PCC between the ROS and theHUT to the measured voltage and current of the P-HIL am-plifier. This element is critical as it has a profound influenceon the accuracy and stability of the P-HIL-based experiment.Few commonly known methods of interface algorithm are pre-sented here [36]. Dual forms of each method, referred to asvoltage type and current type, are generally available to accom-modate operation with an amplifier accepting either a voltagereference or a current reference, respectively.

Figure 16 shows the interfacing method, where the voltageV1 is amplified for the same kind of P-HIL application it can beinterfaced by amplifying current instead of voltage and the volt-age across the HUT is sent as feedback to the RTDS as shownin the Figure 17.

28 hardware-in-the-loop for power electrical systems

Figure 17: P-HIL simulation interface done by current amplification

These two methods are duals in every interface algorithmand gives different boundaries of stability hence a suitable typeof amplification for interface method should be selected.

2.3.3.1 Ideal-Transformer Model

Ideal transformer Model (ITM) is the most commonly employedmethod employed in interfacing RTDS and the HUT, becauseof its straight forward nature, not being complex to realize thesystem and also, it is most accurate and immediate solution tothink of. Depending on type of signal to be amplified it is againcategorized into Voltage type ITM and current type ITM. Heretime delay ∆t is considered as the only error in P-HIL interfaceamplification, while there are many factors involved which arediscussed in later section, but this one is major, since it involvesin the stability of the test.

In this method the reference signal is given to the power am-plifier with a unity gain no modifications are made, the feed-back signal is given to the RTDS at proper sampling rate asshown in the Figure 18.

The open loop transfer function for this algorithm is given by,

GITM = −exp(−s∆t) ∗ Zs(S)Zl(S)

∗ Tpa(S) ∗ Tm(S) (8)

Where,∆t Total time delayTpa(S) is the dynamic transfer function of the Power amplifierTm(S) is the dynamic transfer function of measurement system

2.3 power-hardware-in-the-loop 29

Figure 18: Ideal-transformer model method of interface algorithm

∆t is occurred due to the delay in the signal, occurred dueto power amplifier ∆td1 and due to measurement process ∆td2.The stability of this interface depends on ratio of Zs(S)

Zl(S)in the

voltage type amplification interface and on Zl(S)Zs(S)

in the in thecurrent type amplification.

2.3.3.2 Time-variant First order Approximation

Time-variant First order Approximation (TFA) is based on theassumption that, HUT in a Power-HIL simulation can be mod-eled as first-order linear system having RL or RC topology.With the recorded historical simulation data, the co-efficientsof HUT model can be solved and updated on line during theexperiment. Compensations can then made in the simulator tocorrect the errors introduced by the interface.

2.3.3.3 Transmission line model

Transmission line model (TLM) uses a linking inductor or ca-pacitor to interface the RTS with the HUT as shown in the Fig-ure 19.

Figure 19: Scheme of TLM interface algorithm

30 hardware-in-the-loop for power electrical systems

The inductor or capacitor is taken as a Bergeron transmissionline and modeled as an equivalent Norton circuit or Thevenincircuit. The detailed interface of this method is shown in theFigure 20.

Figure 20: TLM interface algorithm

The equations of the TLM method are given by followingequations, Linkage impedances is given by Equation 9 and linecoefficient is given by Equation 10 respectively.

Zlk =L

∆t

Zlk =∆t

C

(9)

β =Zs −ZlkZs +Zlk

Zlk ∗ Tamp(S) ∗ Tflit(S) (10)

The open loop transfer function using this algorithm is,

GTLM =1−β ∗ exp(−2S∆t)1+β ∗ exp(−2S∆t)

∗ ZsZlk∗ Tamp(S) ∗ Tflit(S) (11)

Where,∆t is the time delayTamp(S) Transfer function of power amplifierTflit(S) Transfer function of filterL Inductance in mHC Capacitance in µF

2.3.3.4 Partial Circuit Duplication

The partial circuit duplication (PCD) method includes a linkingimpedance Zab in the simulated system and also on the hard-ware side as shown in the Figure 21.

2.3 power-hardware-in-the-loop 31

Figure 21: PCD interface algorithm

Large values of the linking impedance improves the stabil-ity of the interface but introduces inaccuracies due to increasedpower losses. The open loop transfer function of the PCD methodis given by

Gpcd =ZsZhut

(Zs +Zab)(Zhut +Zab)∗ exp(−s∆t) ∗ Tamp(S) ∗ Tfilt(S)

(12)

Where,∆t is the time delayTamp(S) Transfer function of power amplifierTflit(S) Transfer function of filterZab Impedance linked

2.3.3.5 Damping Impedance Method

The damping impedance method(DIM) is a composite of theideal transformer and PCD methods. It has a linking impedanceZab similar to the PCD and includes a damping impedanceZdamp as shown in Figure 22. The DIM method has very high

Figure 22: DIM interface algorithm

32 hardware-in-the-loop for power electrical systems

stability when the value of Zdamp is equal to Zhut. The openloop transfer function of the DIM method is given by Equa-tion 13.

Gdim =Zs(Zhut −Zdamp)

(Zs +Zab +Zdamp)(Zhut +Zab)∗exp(−s∆t)∗Tamp(S)∗Tfilt(S)

(13)

Where,

∆t is the time delayTamp(S) Transfer function of power amplifierTflit(S) Transfer function of filterZab Impedance linkedZdamp Damping Impedance

There are many interface algorithms are coming up accord-ing to the needs and to address the issues, but the above men-tioned are the basic types that can be incorporated easily.

2.3.4 Pros and Cons of Interface Algorithms

Several advantages and disadvantages of using different inter-face algorithms are briefly presented in the Table 1 [14, 36].

2.3.5 Open issues in P-HIL simulation

As with any modeling and simulation work, the accuracy ofthe virtual surrounding system is limited by the accuracy ofthe models employed in that system. Second, the restrictionsimposed by the real-time simulation requirement may imposeadditional limitations on the size and level of detail that can beincluded in the models. Real-time simulators typically employfixed time-step solvers with some minimum achievable time-step sizes. This restriction can have implications on the timeconstants that can be represented, switching frequencies thatcan be employed for switching power electronics models, andgenerally on the frequency band over which the models canappropriately represent reality.

Additionally, the amplifiers, actuators, sensors and ADC orDAC cards comprising the P-HIL interfaces introduce time de-lays, distortion, and their own bandwidth limitations which canaffect the experiments and, in some cases, lead to instabilities.

Capability limitations in terms of voltage, current, torque,speed, etc. of the amplifiers and actuators also impose further

2.3 power-hardware-in-the-loop 33

Interface Algorithm Pros and Cons

ITM

Pros:Simple to implement and highlyaccurate. Cons:Stability depends on the ratio ofsource impedance to the loadimpedance in case of voltage typeand on the ratio of load impedanceto the source impedance in case ofcurrent type.

TFA

Pros:Approaches modeling of HUT as firstorder, high bandwidth, Functionalityfor error correction.Cons:Computational complexity due tomatrix inversion, Instability due topredictive behavior, Inaccurate due toextreme sensitivity to the sensornoise, it has limitations withnon-linear systems and highfrequency signals.

TLA

Pros:highly stable because of it’s based ontrapezoidal approximationCons:The algorithm replaces linkinginductor and capacitor with a resistorwhich accounts of the powerconsumption which is not acceptable.Low flexibility and high maintenancecost.

restrictions on the range of experiments that can be conducted.Thus, it is important to consider the limitations of a P-HIL ex-periment, and it is important to properly consider the accuracyof the results in the context of the points noted. Indeed, twoof the most important aspects of the analysis of P-HIL experi-ments are assessment of stability and accuracy.

34 hardware-in-the-loop for power electrical systems

Interface Algorithm Pros and Cons

PCD

Pros:Highly stable, it is a promisingmethod to implement for large scalecircuits and systems.Cons:Value of linking component ratio tosource or load impedance affectsaccuracy. Accuracy is often low dueto stability requirements on Zab, poorconvergence limits the applicabilityof the relaxation technique.

DIM

Pros:high stability and accuracy when thedamping impedance is equal to theload impedance of HUT, this methodhas the ability to adapt.Cons:High fidelity impedance basedmodel of the HUT is required,though it may often not available.

Table 1: Pros and Cons of Interface algorithm

2.3.5.1 Stability issue of P-HIL

the closed-loop system in real-time simulation platform con-sists of DAC converters, power amplifier, HUT, measurementprobes, sample-and hold circuit and ADC converters shouldnot exhibit unstable/oscillatory behavior. Stability is a neces-sary criterion for the accuracy of the simulation and for theequipment safety, HUT devices may be damaged when the sys-tem becomes unstable. Hence, appropriate counter measuresshould be implemented to detect undesired modes of opera-tion and return to a safe state.

One of the main sources of instability in P-HIL simulationsis the computation time and data acquisition time of the RTDSsystem [36]. Even if the time step is very short as small as microseconds, for certain parameter values of the hardware part to besimulated and the hardware part attached as real HUT device,the P-HIL simulation may become unstable. Additionally, de-pending on the equipment used and its realization, the poweramplifier may be far from ideal by introducing additional de-

2.3 power-hardware-in-the-loop 35

lays, exhibiting other dynamic behavior or even distortions dueto nonlinearity.

Consider the voltage divider circuit as shown in Figure 23,the load impedance is the physical resistor while the other partsof the circuit are simulated. To facilitate this the voltage ampli-fier produces the simulated voltage V1 as a physical voltage V

′1

and imposes it on to the actual load resistor.

Figure 23: Interface of Voltage divider circuit for stability studies

The actual current i2 flowing through the resistor is mea-sured and fed back to the RTDS which incorporates that signalas the actual current flowing inside the simulated circuit.Theoriginal circuit is known to be stable but it’s implementation inP-HIL simulation is found instable. Let an error ε occurs dur-ing the voltage amplification of V2 at the time instance te, thecorresponding error in i2 is given by Equation 14.

∆V2(te) = ε and i2 =V2Zl

∆i2(te) =ε

Zl

(14)

When this current is fed back to simulator it will cause fur-ther error in V1 and it is given by Equation 15.

∆V1 = Vs −Zs ∗ i1

∆V1(tk+1) = −Zs

Zlε

(15)

By sending out this updated value of V1 in the new time step,the previous error is effectively amplified by a factor of −Zs

Zl. As

36 hardware-in-the-loop for power electrical systems

long as ZsZl

is greater than 1, the oscillatory error will continueto increase in magnitude until it reaches the maximum hard-ware limit. Concluding it, for P-HIL to be stable, both HUT andthe simulated model should be stable systems, the open looptransfer function of the system must meet Nyquist stability cri-terion. For Figure 23 the open loop transfer function is given byEquation 16. For stability Zs

Zl< 1.

Gol = −Zs

Zl∗ exp(−s∆t) (16)

2.3.6 Accuracy issue of P-HIL

Accuracy relies on stability, but goes much further, because itis a necessary and sufficient condition for P-HIL simulation. AP-HIL simulation demands a certain level of accuracy other-wise, results will be meaningless. Ideally, the interface betweenthe hardware under test and the simulated system should haveunity gain with infinite bandwidth and zero-time delay in or-der to ensure proper correspondence between the HIL systemand the original system.

However, such an ideal interface is neither achievable nor af-fordable in practice. As a result, all HIL simulations containerrors caused by the imperfection of the interface. When theerrors are too excessive the validity of the simulation are com-promised, it gives out misleading results.

only limited research has been performed on the simulationaccuracy issue and it remains an open research problem thatneeds better solutions. One possible method to estimate the ac-curacy of a power HIL simulation is to evaluate the transferfunction of the system response with respect to interface dis-turbances. For example, we assume that, in the system of Fig-ure 23, the system state of interest is the dynamic response of V1[37], Because most of the system error comes from the voltageamplification, we treat the voltage error as an external distur-bance and study the transfer function between this disturbanceand V1. The transfer function to be evaluated in this example isgiven by Equation 17.

G =−ZsZl

1+ ZsZlexp(−s∆t)

(17)

2.3 power-hardware-in-the-loop 37

Small value of transfer function shows the rejection to thedisturbances hence high accuracy in the simulation results. Byimplementing different interfacing algorithms, different levelof accuracy can be reached, hence the open loop transfer func-tion in each method of interface algorithm is mentioned, sothat, the user can select according to the simulation needs. Dif-ferent interface algorithms influence the P-HIL simulation byaltering the system’s open-loop transfer function, the system’sopen-loop transfer function, especially its magnitude, has a di-rect relationship to the system stability and to the simulationaccuracy. Therefore, it can be utilized as the performance indexfor interface algorithms.

2.3.6.1 Interface Compensation

Since a P-HIL simulation inherits the flexibility of the softwaresimulation, various function blocks can be easily implementedin the simulation to preprocessing a signal before it is sent tothe interface. This leads to the possibility to alter the overall per-formance of a P-HIL interface by inserting certain compensator.For example, assume the transfer function of an interface isG(S). Adding a compensator with a transfer function of G−1(S)will idealize the interface to unity gain [37].

Interface compensation differs from the interface algorithm.Interface compensation does not alter the P-HIL system topol-ogy but instead inserts a function block in the path of an in-terfacing signal in order to compensate for the time delay, theinjected noise, or the magnitude attenuation in the interface.