Corso ARM

-

Upload

nicola-masarone -

Category

Documents

-

view

301 -

download

6

description

Transcript of Corso ARM

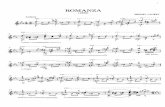

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

1/102

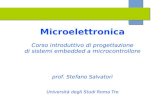

Microprocessori e Microcontrollori Corso di progettazione su Corso di progettazione su SoCSoC ARM ARM

Prof. N. MasaroneLab.: St. 132 (S2DEL – Solid State and Diamond Electronics Lab.)e.mail: [email protected]

Architettura ARM

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

2/102

Hardware Software

Soluzione del problema

Sistema desktop

Sistema embeddedHardware Firmware

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

3/102

Identificazione dell'hardware necessario

SBC

DSP

µC

FPGA

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

4/102

elaborazione

μP011001...

D/A101101...

main(){ ...

101101...

A/D

conversione A/D conversione D/A

registrazione

Esempio di sistema misto analogico-digitale per applicazioni audio

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

5/102

Breve storia del processore ARM (Advanced Risc Machine)●Il concetto RISC (Reduced Instruction Set Computer) risale a programmi di ricerca realizzati negli anni '80 presso le Università di Stanford e Berkeley (CA – USA).

● ARM viene sviluppato presso la Acorn Computers Limited di Cambridge (UK) tra il 1983 e il 1985 (Acorn Risc Machine).

● Acorn aveva acquisito una forte posizione sul mercato britannico, specialmente nel mondo scolastico, grazie al microcomputer BBC (basato sul processore 8-bit 6502, presente anche in Apple II) realizzato per una serie televisiva della BBC.

● Per migliorare il microcomputer, nel 1983, gli ingegneri Acorn prendono in considerazione vari processori commerciali CISC 16-bit, ma nessuno risulta soddisfacente (specialmente nel tempo di risposta agli interrupt, punto di forza del vecchio 6502).

● Acorn prende in considerazione l'eventualità di sviluppare in proprio un processore, ma l'impegno previsto risulta enorme, sia in termini di forza lavoro che in termini di conoscenze tecniche.

● L'articolo sul processore RISC I della Berkeley University propone una soluzione vincente sviluppata da pochi studenti universitari in meno di un anno.

● La semplicità di esecuzione dell'architettura RISC onora il vincolo richiesto di velocità nella risposta agli interrupt.

●L'ARM diventa il componente centrale della produzione Acorn ed è il primo processore RISC commerciale (1985).

●Nel 1990 nasce ARM Limited (Advanced Risc Machine) come società autonoma, venditrice di proprietà intellettuale (IP); ARM è quindi una società fabless, cioè non produce silicio.

● Ad oggi, più di 10 miliardi di processori ARM sono stati consegnati nel mondo intero dagli oltre 200 partners di ARM Limited.

● La consegna continua incessante ad una velocità di 90 processori al secondo.

ARM Milestones: http://www.arm.com/aboutarm/milestones.html

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

6/102

5V TechnologiesActel CorporationAlchip Technologies, Inc.Altera CorporationAnalog Devices IncAnyka Technologies CorporationAtmelAvago TechnologiesBroadcom CorporationCelestial Semiconductor, Ltd.Chipnuts Technology (Shanghai) Inc.ChipXCirrus LogicConexantDatang Microelectronics Technology Co., LTD.eASICEnergy Micro ASeSilicon CorporationFreescale SemiconductorFujitsu Microelectronics America, Inc.GENS Logic Co., Ltd.HiSilicon Technologies Co., Ltd.INDILINXIntel CorpInternational Business MachinesISINE INC.Kawasaki MicroelectronicsLuminary Micro, Inc

Marvell Semiconductor, Inc.Micronas GmbHMobilEye Vision Technologies LtdNEC Electronics (Europe) GmbHNeoMagic CorporationNVIDIANXPOberthur Card SystemsOki Electric Industry Co.,Ltd.ON Semiconductor (Formerly AMI Semiconductor)Open-SiliconOxford SemiconductorPixim, Inc.Samsung Electronics Co., LtdShanghai Huahong Integrated Circuit Co., Ltd.Shanghai Jade Technologies Co, Ltd.Shanghai Silicon IP Technologies Co.,Ltd.Shenzhen ZTE IC Design Co.LtdSpansion IncSpreadtrum Communications Inc.STEPMINDSTMicroelectronicsTexas InstrumentsToshiba America Electronic ComponentsWinbond Electronics CorporationXi'an HuaXun Microelectronics Inc.Zoran Corporation© ARM Ltd

Partners ARM Ltd.

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

7/102

© ARM Ltd

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

8/102

Nintendo DS LiteARM Processor: ARM 7, ARM 9

ARM Processor: ARM 9ESony Playstation 3 (60GB)

ARM Processor: ARM 9Sony PlayStation Portable - PSP

Sharp Aquos LCD TVARM Processor: ARM 7

Humax RG-100 Digital Satelite Set-top-boxARM Processor: ARM 9

Kodak EASYSHARE Z1275 Zoom Digital CameraARM Processor: ARM926EJ-S© ARM Ltd

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

9/102

Apple iPod Nano

ARM Processor: Dual ARM7TDMI

Apple iPhone

ARM Processor: ARM1176JZF-SARM7TDMI-SARM926EJ-S

ARM 9

Nokia N70 3G Phone

ARM Processor: ARM9

Hewlett Packard iPaq 6320 PDA

ARM Processor: ARM925

Tom Tom Go 300 GPS Portable Navigation system

ARM Processor: ARM920T

© ARM Ltd

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

10/102

Verbatim Store ‘n Go Pro DiskOnKey

ARM Processor: ARM7

HP Deskjet 5940

ARM Processor: ARM946E-S

Netgear WGR614 Wireless Router

ARM Processor: ARM9

D-Link DVC 2000 Broadband Internet VideoPhone

ARM Processor: ARM9

Opengear CM4000remote control server

ARM Processor: ARM9

© ARM Ltd

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

11/102

Dynon Avionics EFIS-D10A - Electronic Flight Information System

ARM Processor: ARM7TDMI

Artega GT (Dual-Dashboard Display)

ARM Processor: ARM926EJ-S

ExaDigm XD2100SP Mobile Payment system

ARM Processor: ARM7

Hewlett Packard HP 50g Scientific Calculator

ARM Processor: ARM920T

Sonosite MTurbo (Portable Ultrasound Device)

ARM Processor: ARM926

© ARM Ltd

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

12/102

© 2000 Addison Wesley

address

instructions

processor

memory

registers

instructions

data

00..0016

FF..FF16

and data

Schema di computer con programma memorizzato

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

13/102

opcode S

12 bits4 bits

Instruction Opcode Effect

LDA S 0000 ACC := mem16[S]

STO S 0001 mem16[S] := ACC

ADD S 0010 ACC := ACC + mem16[S]

SUB S 0011 ACC := ACC - mem16[S]

JMP S 0100 PC := S

JGE S 0101 if ACC >= 0 PC := S

JNE S 0110 if ACC !=0 PC := S

STP 0111 stop

© 2000 Addison Wesley

Il set di istruzioni MU0

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

14/102

function op 1 addr. op 2 addr. dest. addr. next_i addr.

n bitsn bitsn bitsn bitsf bits

function op 1 addr. op 2 addr. dest. addr.n bitsn bitsn bitsf bits

function op 1 addr. dest. addr.

n bitsn bitsf bits

function op 1 addr.n bitsf bits

function

f bits

istruzione a 4 indirizzi

istruzione a 3 indirizzi

istruzione a 2 indirizzi

istruzione a 1 indirizzo

istruzione a 0 indirizzi

Formato indirizzi delle istruzioni

ARM Mode

Thumb Mode

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

15/102

Uso dinamico tipico delle istruzioni

Instruction type Dynamic usage

Data movement 43%

Control flow 23%

Arithmetic operations 15%

Comparisons 13%

Logical operations 5%

Other 1%

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

16/102

Architettura RISC(Reduced Instruction Set Computer)

Set di istruzioni ridotto: lunghezza fissa, un solo ciclo per l'esecuzione (pipeline). Il peso

dell'elaborazione è spostato sul compilatore;

l'hardware esegue istruzioni semplici ad alta velocità.

Funzionalità load/store: il

processore lavora solo su dati presenti nei

registri, limitando gli accessi alla

memoria (collo di bottiglia per la

velocità di esecuzione) per le

sole istruzioni specifiche di load e

di store.

Esecuzione in pipeline: il

processore spezza ogni istruzione in

più fasi che interessano parti

diverse dell'hardware.

(Fetch, Decode, Execute) con un

miglioramento del throughput.

Ampio banco di registri: validi sia

per il contenimento di dati che di

istruzioni, permettono

un'esecuzione più veloce del

programma, limitando gli accessi alla

memoria principale.

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

17/102

Stato ARM (32 bit) e stato Thumb (16 bit)●Il codice Thumb utilizza circa il 40% di istruzioni in più rispetto al codice ARM●Il codice Thumb utilizza il 30% in meno di potenza della memoria esterna

Il codice Thumb occupa circa il 70% dell'equivalente

codice ARM

Con memoria a 16-bit il codice Thumb risulta 45% più veloce del codice ARM

Con memoria a 32-bit il codice ARM risulta 40% più

veloce del codice Thumb

16-bit mem

32-bit mem

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

18/102

Modi di funzionamento del processore ARM

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

19/102

= banked register

Registri generali e Program Counter nello stato ARM

r0r1r2r3r4r5r6r7r8r9r10r11r12r13

r14 (LR)r15 (PC)

CPSR

User | Systemr0r1r2r3r4r5r6r7

r8_fiqr9_fiqr10_fiqr11_fiqr12_fiqr13_fiq

r14_fiq (LR)r15 (PC)

CPSR

FIQ

SPSR_fiq

r0r1r2r3r4r5r6r7r8r9r10r11r12

r13_svcr14_svc (LR)

r15 (PC)

CPSR

Supervisor

SPSR_svc

r0r1r2r3r4r5r6r7r8r9

r10r11r12

r13_abtr14_abt (LR)

r15 (PC)

CPSR

Abort

SPSR_abt

r0r1r2r3r4r5r6r7r8r9r10r11r12

r13_irqr14_irq (LR)

r15 (PC)

CPSR

IRQ

SPSR_irq

r0r1r2r3r4r5r6r7r8r9

r10r11r12

r13_undr14_und (LR)

r15 (PC)

CPSR

Undefined

SPSR_und

Exception modes

Priviliged modes

program status register nello stato ARM

Register bank: 31x32-bit registers + 6 status registers

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

20/102

Registri generali e Program Counter nello stato Thumb

User | System FIQ Supervisor Abort IRQ Undefined

Exception modes

Priviliged modes

= banked register

r0r1r2r3r4r5r6r7SPLRPC

CPSR

r0r1r2r3r4r5r6r7

SP_fiqLR_fiq

PC

CPSRSPSR_fiq

r0r1r2r3r4r5r6r7

SP_svcLR_svc

PC

CPSRSPSR_svc

r0r1r2r3r4r5r6r7

SP_abtLR_abt

PC

CPSRSPSR_abt

r0r1r2r3r4r5r6r7

SP_irqLR_irq

PC

CPSRSPSR_irq

r0r1r2r3r4r5r6r7

SP_undLR_und

PC

CPSRSPSR_und

Program status register nello stato Thumb

Register bank: 21x16-bit registers + 6 status registers

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

21/102

r0r1r2r3r4r5r6r7r8r9

r10r11r12

Stack pointer (r13)Link register (r14)

Program counter (r15)

ARM state

Current program status register(CPSR)

Saved program status register(SPSR)

Thumb state

r0r1r2r3r4r5r6r7

Stack pointer (r13)Link register (r14)

Program counter (r15)Current program status register

(CPSR)Saved program status register

(SPSR)

Relazione tra registri dello stato thumb e registri dello stato ARM

Copyright © 2001 ARM Limited

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

22/102

Modi e registri visibili nello stato Thumb e ARM

Copyright © 2001 ARM Limited

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

23/102

CPU08 opcode map (CISC) © Freescale Semiconductor, Inc.

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

24/102

ARM instruction set

summary (RISC)

Copyright © 2001 ARM Limited

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

25/102

Program status register (CPSR - SPSR_exc)

0

Z C V Q Res JN Reserved Reserved E A F T M[4:0]IGE[3:0]

31 30 29 28 27 26 25 24 23 20 19 16 15 10 9 8 7 6 5 4

= reserved in ARM7/TDMI-S core

condition code flags control bits

oVerflow

Carry or borrow or extend

Zero

Negative or less than

IRQ disable

FIQ disable

Thumb/ARM

10000M[4:0]Mode

User

10001FIQ

10010IRQ

10011Supervisor

10111Abort

11011Undefined

11111System

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

26/102

Istruzioni di spostamento

Copyright © 2001 ARM Limited ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

27/102

modifica di CPSR (modo di funzionamento):MRS r0, CPSR ; carica CPSR in r0BIC r0, r0, #0x1F ; cancella il modo corrente..ORR r0, r0, #0x13 ; .. ed entra in SupervisorMSR CPSR_c, r0 ; aggiorna CPSR

; ora in stato SVC

modifica di CPSR (flag di condizione):MRS r0, CPSR ; carica il valore di CPSR in r0BIC r0, r0, #0xF0000000 ; azzera le flag N, Z, C, VMSR CPSR_f, r0 ; aggiorna le flag in CPSR

modifica di CPSR (disabilita IRQ):MRS r0, CPSR ; carica il valore di CPSR in r0BIC r0, r0, #0x80 ; disabilita INTMSR CPSR_c, r0 ; aggiorna lo stato in CPSR

; ora in stato INTmodifica di CPSR (entra in modalità FIQ):

MRS r0, CPSR ; carica il valore di CPSR in r0BIC r0, r0, #0x1F ; azzera i bit di modalitàORR r0, r0, #0x11 ; imposta i bit come FIQMSR CPSR_c, r0 ; aggiorna la modalità in CPSR

; ora in stato FIQ ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

28/102

Istruzioni aritmetiche

Copyright © 2001 ARM Limited

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

29/102

somma di due registri:ADD r5, r1, r3; addiziona r1 e r3 con risultato in r5

decrementa r2 e verifica se vale zero:SUBS r2, r2, #1; decrementa r2 e imposta CCBEQ LABEL ; salta se r2 vale zero.. ; .. altrimenti va oltre

moltiplica r0 per 5 (usando il barrel shifter):ADD r0, r0, r0, LSL #2 ; r0 * 4 + r0 = r0 * 5

subroutine che moltiplica r0 per 10 (usando il barrel shifter):MOV r0, #3BL TIM10..

TIM10 MOV r0, r0, LSL #1 ; x 2ADD r0, r0, r0, LSL #2 ; x 5MOV PC, r14 ; ritorna

addiziona un intero a 64 bit in r0, r1 ad un altro in r2, r3:ADDS r2, r2, r0; somma i meno significativi e salva il carryADC r3, r3, r1; somma i più significativi con carry

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

30/102

ARM Architecture Reference Manual

031

00000

LSL #5

031

00000

LSR #5

031

11111 1

ASR #5 , negative operand

031

00000 0

ASR #5 , positive operand

0 1

031

ROR #5

031

RRX

C

C C

© 2000 Addison Wesley

Operazioni di shift in ARM

LSL: Logical Shift Left (0-31)LSR: Logical Shift Right (0-32)ASL: Arithmetic Shift Left = LSL (0-31)ASR: Arithmetic Shift Right (0-32)ROR: ROtate Right (0-32)RRX: Rotate Right eXtended (1)

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

31/102

prodotto scalare di due vettori:MOV r11, #20 ; inizializza il contatore del cicloMOV r10, #0 ; inizializza il totale

LOOP LDR r0, [r8], #4 ; carica il primo elemento..LDR r1, [r9], #4 ; .. ed il secondoMLA r10, r0, r1, r10 ; r10 = r0 x r1 + r10SUBS r11, r11, #1 ; decrementa il contatore del cicloBNE LOOP ; se r11 <> 0 salta a LOOP .... ; .. altrimenti procede

esempi di moltiplicazioni:MUL r4, r2, r1 ; r4 = r2 x r1MULS r4, r2, r1 ; r4 = r2 x r1, set flag N e ZMLA r7, r8, r9, r3 ; r7 = r8 x r9 + r3SMULL r4, r8, r2, r3 ; r4 = bit 0 - 31 di r2 x r3

; r8 = bit 32 - 63 di r2 x r3UMULL r6, r8, r0, r1 ; r8, r6 = r0 x r1UMLAL r5, r8, r0, r1 ; r8, r5 = r0 x r1 + r8, r5

sottrazione a 64 bit (r0, r2 LSW mentre r1, r3 MSW):SUBS r4, r0, r2 ; r4 = r0 – r2 e imposta il carrySBC r5, r1, r3 ; r5 = r1 – r3 + carry -1

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

32/102

Istruzioni logiche

Copyright © 2001 ARM Limited ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

33/102

Copyright © 2001 ARM Limited ARM Architecture Reference Manual

esempi di operazioni Booleane:AND r0, r1, r2 ; r0 = r1 and r2ORR r0, r1, r2 ; r0 = r1 or r2EOR r0, r1, r2 ; r0 = r1 xor r2BIC r0, r1, r2 ; r0 = r1 and not r2

esempi di operazioni di confronto:CMP r1, r2 ; imposta cc su r1 - r2CMN r1, r2 ; imposta cc su r1 + r2TST r1, r2 ; imposta cc su r1 and r2TEQ r1, r2 ; imposta cc su r1 xor r2

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

34/102

Istruzioni di salto

Copyright © 2001 ARM Limited

cond 1 0 1 L 24-bit signed word offset

31 28 27 25 24 23 0

cond Rn0 0 0 1 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 031 28 27 6 5 4 3 0

1L

B, BL

BX

CPSR5

T

31 0

0131 Rn

PC

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

35/102

salto incondizionato:B LABEL ; salto incondizionato....

LABEL .. ; .. fin quiciclo 10:

MOV r0,#10; inizializza il contatore del cicloLOOP ..

SUBS r0, #1 ; decrementa il contatore impostando i CCBNE LOOP ; se il contatore <> 0 ripete il ciclo..

.. ; .. altrimenti escechiamata di soubroutine:BL SUB ; branch e link alla subroutine SUB

.. ; punto di ritorno

..SUB .. ; punto d'ingresso della subroutine

MOV PC,r14; ritornachiamata di soubroutine condizionale:

CMP r0, #5 ; se r0 < 5BLLT SUB1 ; chiama SUB1BLGE SUB2 ; chiama SUB2

salto incondizionato:BX r0 ; salta all'indirizzo in r0

; entra in stato Thumb se r0[0]=1

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

36/102

Istruzioni di lettura singola da memoria

Copyright © 2001 ARM Limited ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

37/102

Istruzioni di scrittura singola in memoria

Copyright © 2001 ARM Limited

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

38/102

esempi di load / store singoli:LDR r1, [r0] ; valore all'indirizzo r0 in r1 LDR r8, [r3, #4] ; valore all'indirizzo r3+4 in r8LDR r12, [r13, #-4] ; valore all'indirizzo r13-4 in r12STR r2, [r1, #0x100] ; salva r2 all'indirizzo r1 + 0x100LDRB r5, [r9] ; carica il byte all'indirizzo r9 in r5

; (3 byte superiori azzerati)LDRB r3, [r8, #3] ; carica il byte all'indirizzo r8+3 in r3

; (3 byte superiori azzerati)STRB r4, [r10, #0x200] ; salva byte r4 all'indirizzo r10+0x200LDR r11, [r1, r2] ; valore all'indirizzo r1+r2 in r11 STRB r10, [r7, -r4] ; salva byte r10 all'indirizzo r7-r4LDR r11, [r3, r5, LSL #2]; valore all'indirizzo r3+(r5x4) in r11LDR r1, [r0, #4]! ; valore indirizzo r0+4 in r1, poi r0=r0+4STRB r7, [r6, #-1]! ; salva byte r7 all'indirizzo r6-1,

; poi r6=r6-1LDR r3, [r9], #4 ; val. all'indirizzo r9 in r3, poi r9=r9+4 STR r2, [r5], #8 ; salva r2 all'indirizzo r5, poi r5=r5+8

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

39/102

LDRSH r5, [r9] ; signed halfword dall'indirizzo r9 in r5LDRSB r3, [r8, #3] ; signed byte dall'indirizzo r8+3 in r3LDRSB r4, [r10, #0xC1] ; signed dall'indirizzo r10+0xC1 in r4LDRH r11, [r1, r2] ; halfword dall'indirizzo r1+r2 in r11STRH r10, [r7, -r4] ; halfword da r10 all'indirizzo r7-r4LDRSH r1, [r0, #2]! ; signed halfword dall'indirizzo r0+2

; in r1, poi r0=r0+2LDRSB r7, [r6, #-1]! ; signed byte dall'indirizzo r6-1 in r7,

; poi r6=r6-1LDRH r3, [r9], #2 ; halfword dall'indirizzo r9 in r3,

; poi r9=r9+2STRH r2, [r5], #8 ; halfword da r2 all'indirizzo r5,

; poi r5=r5+8

esempi di load / store singoli:LDR r0, [PC, #40] ; carica in r0 PC+0x40 (=indirizzo della

; istruzione LDR + 8 + 0x40)LDR r0, [r1], r2 ; valore all'indir. r1 in r0, poi r1=r1+r2LDRH r1, [r0] ; halfword ind. r0 in r1 (azzera 2 B sup.) LDRH r8, [r3, #2] ; halfword dall'indirizzo r3+2 in r8LDRH r12, [r13, #-6] ; halfword dall'indirizzo r13-6 in r12STRH r2, [r1, #0x80] ; halfword da r2 all'indirizzo r1+0x80

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

40/102

Istruzioni di lettura multipla da memoria

Copyright © 2001 ARM Limited ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

41/102

Istruzioni di scrittura multipla in memoria

Copyright © 2001 ARM Limited

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

42/102

copia di registri con uso dello stack:STMFD r13!, {r2-r9} ; salva r2-r9 sullo stackLDMIA r0!, {r2-r9} ; carica 8 word dall'indirizzo r0 in r2-r9STMIA r1, {r2-r9} ; salva r2-r9 all'indirizzo r1LDMFD r13!, {r2-r9} ; ripristina r2-r9 dallo stack

esempi di load store multipli:LDMIA r1, {r0, r2, r5} ; r0 := mem

32[r1]

; r2 := mem32[r1+4]

; r5 := mem32[r1+8]

STMFD r13!, {r0-r2, r14} ; salva r0-r2 e LR sullo stack LDMFD r13!, {r0-r2, PC} ; ripristina dallo stack r0-r2 e il PC

nota all'istruzione LDM tratta da ARM Architecture Reference Manual:The registers are loaded in sequence, the lowest-numbered register from the lowest memory address (start_address), through to the highest-numbered register from the highest memory address (end_address)

nota all'istruzione STM tratta da ARM Architecture Reference Manual:The registers are stored in sequence, the lowest-numbered register to the lowest memory address (start_address), through to the highest-numbered register to the highest memory address (end_address)

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

43/102

stack

libera

heap

applicazione

memoria

r0r1r2r3r4r5r6r7r8r9r10r11r12

r13 (SP)r14 (LR)r15 (PC)

registri

copia di registri con uso dello stack:STMFD r13!, {r2-r9} ; salva r2-r9 sullo stackLDMIA r0!, {r2-r9} ; carica 8 word dall'indirizzo r0 in r2-r9STMIA r1, {r2-r9} ; salva r2-r9 all'indirizzo r1LDMFD r13!, {r2-r9} ; ripristina r2-r9 dallo stack

Scopo di queste istruzioni è copiare in area2 i dati presenti nell'area1, senza utilizzare istruzioni dirette di movimento dati in memoria. area1

area2

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

44/102

STMFD r13!, {r2-r9} ; salva r2-r9 sullo stack

r0r1r2r3r4r5r6r7r8r9r10r11r12

r13 (SP)r14 (LR)r15 (PC)

0x00000B010x000000030x000002030x00000F040x00000A250x00002C080x00002C0D

bit 0bit 31

0x00005090

0x0000F200NN NN NN NN

0x0000F1FC

0x0000F1F8

0x0000F1F4

0x0000F1EC

0x0000F1F0

0x0000F1E8

0x0000F1E4

0x0000F1E0

00 00 0B 01

00 00 00 03

00 00 0302

00 00 0F 04

00 00 250A

00 00 2C 08

00 00 0D2C

00 00 50 90

registri memoria

0x0000F200 0x0000F1E0

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

45/102

LDMIA r0!, {r2-r9} ; carica 8 word dall'indirizzo r0 in r2-r9

r0r1r2r3r4r5r6r7r8r9r10r11r12

r13 (SP)r14 (LR)r15 (PC)

0x0118AC020x5576E4CD0xAD4F21780x021243290x23282FE20x16CA43230x24FE3200

bit 0bit 31

0x1443AAD4

0x10000024NN NN NN NN

0x10000020

0x1000001C

0x10000018

0x10000010

0x10000014

0x1000000C

0x10000008

0x10000000

14 43 AA D4

24 FE 32 00

16 CA 2343

23 28 2F E2

02 12 2943

AD 4F 21 78

55 76 CDE4

01 18 AC 02

registrimemoria

0x10000000

0x0000F1DF

0x10000024

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

46/102

STMIA r1, {r2-r9} ; salva r2-r9 all'indirizzo r1

r0r1r2r3r4r5r6r7r8r9r10r11r12

r13 (SP)r14 (LR)r15 (PC)

0x0118AC020x5576E4CD0xAD4F21780x021243290x23282FE20x16CA43230x24FE3200

bit 0bit 31

0x1443AAD4

0x20000024NN NN NN NN

0x20000020

0x2000001C

0x20000018

0x20000010

0x20000014

0x2000000C

0x20000008

0x20000000

14 43 AA D4

24 FE 32 00

16 CA 2343

23 28 2F E2

02 12 2943

AD 4F 21 78

55 76 CDE4

01 18 AC 02

registrimemoria

0x10000024

0x0000F1DF

0x20000000

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

47/102

LDMFD r13!, {r2-r9} ; ripristina r2-r9 dallo stack

r0r1r2r3r4r5r6r7r8r9r10r11r12

r13 (SP)r14 (LR)r15 (PC)

0x00000B010x000000030x000002030x00000F040x00000A250x00002C080x00002C0D

bit 0bit 31

0x00005090

0x0000F200NN NN NN NN

0x0000F1FC

0x0000F1F8

0x0000F1F4

0x0000F1EC

0x0000F1F0

0x0000F1E8

0x0000F1E4

0x0000F1E0

00 00 0B 01

00 00 00 03

00 00 0302

00 00 0F 04

00 00 250A

00 00 2C 08

00 00 0D2C

00 00 50 90

registri memoria

0x0000F2000x0000F1E0

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

48/102

r5r1

r9’

r0r9

STMIA r9!, {r0,r1,r5}

100016

100c 16

101816

r1r5r9

STMDA r9!, {r0,r1,r5}

r0

r9’ 100016

100c 16

101816

r5r9

STMDB r9!, {r0,r1,r5}

r1

r0r9’ 100016

100c 16

101816

r5r1r0

r9’

r9

STMIB r9!, {r0,r1,r5}

100016

100c 16

101816

Ascending Descending Full Empty Full Empty

Increment

Before STMIB STMFA

LDMIB LDMED

After STMIA STMEA

LDMIA LDMFD

Decrement

Before LDMDB LDMEA

STMDB STMFD

After LDMDA LDMFA

STMDA STMED

© 2000 Addison Wesley

Gestioni dello stack e relative istruzioni multiple

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

49/102

Generalità sullo stack

ARM Architecture Reference Manual

SP (empty ascending) (full descending) SP

(empty descending) SP

Lo stack è un'area di memoria per la registrazione temporanea delle informazioni; può essere utilizzato, per es. all'inizio di una funzione, per salvare il valore corrente dei registri, al fine di utilizzarli nel corpo funzione scrivendovi altri dati. Al termine della funzione i registri possono essere ripristinati, recuperandone i valori precedenti dallo stack.Lo stack è una struttura dati di tipo LIFO (Last-In First-Out), ovvero di tipo pila: l'ultimo dato inserito nello stack è il primo ad essere recuperato dallo stack. Deve sempre essere disponibile un puntatore SP (Stack Pointer) che fornisce l'indirizzo di accesso allo stack.Con gli attributi ascending e descending indichiamo la possibilità di aggiungere elementi nello stack utilizzando indirizzi di memoria rispettivamente crescenti o descrescenti.Con gli attributi full ed empty indichiamo la possibilità che lo stack pointer punti ad un indirizzo rispettivamente vuoto (quindi privo di valore significativo) o pieno (cioè già utilizzato per il salvataggio di un valore utile).

SP (full ascending)

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

50/102

Istruzioni di scambio, coprocessore e SWI

Copyright © 2001 ARM Limited ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

51/102

esempi di swap:SWP r12, r10, [r9] ; carica in r12 il valore all'indirizzo r9 e

; salva r10 nell'indirizzo r9SWPB r3, r4, [r8] ; carica un byte in r3 dall'indirizzo r8 e

; salva un byte da r4 all'indirizzo r8SWP r1, r1, [r2] ; scambia il valore in r1 e l'indirizzo

; in r2

esempio di SWI:SWI#0xABCDEF ; passa in modo Supervisor (privilegiato)

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

52/102

ARM Architecture Reference Manual

esempio di semaforo: [r1] → 0xFF (rosso), 0x00 (verde)MOV r0, #0xFF ; valore per il rosso

loop SWPB r0, r0, [r1] ; carica in r0 il valore da [r1] e viceversaCMP r0, #0xFF ; verifica r0 e 0xFF (rosso)BEQ loop ; se r0=0xFF va in loop

r0r1

0x00 memoria0xFF

caso [r1] = 0x00 (semaforo verde)

r0r1

0xFF memoria0x00

r0r1

0xFF memoria0xFF

caso [r1] = 0xFF (semaforo rosso)

In questo caso rimane in loop fintantoché il semaforo è rosso

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

53/102

ARM Architecture Reference Manual

bit 0bit 31

0x00 0xNN 0xNN 0xNN

0xNN 0xNN 0xNN 0xNN

0xNN 0xNN 0xNN 0xNN

0xNN 0xNN 0xNN0xNN

0xNN 0xNN 0xNN 0xNN

0xFF 0xNN 0xNN0xNN

0xNN 0xNN 0xNN 0xNN

0xNN 0xNN 0xNN0xNN

0xNN 0xNN 0xNN 0xNN

memoria condivisa

μP1

μP2L'area di memoria condivisa in rosso è

bloccata (p.e. da µP1) e può essere liberata

solo da questo.

L'area di memoria condivisa in verde è libera e può essere bloccata dal primo processore che la richiede.

Le memorie condivise sono aree dati accessibili da più task, in esecuzione sullo stesso processore o su processori diversi. Possono essere un modo semplice ed efficace per far comunicare i task tra loro; risulta però fondamentale il sincronismo delle operazioni di lettura/scrittura, al fine di garantire l'integrità delle informazioni memorizzate. A tal scopo si utilizzano i semafori.

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

54/102

A R M c o n d i t i o n c o d e sO p c o d e[ 3 1 : 2 8 ]

M n e m o n i ce x t e n s i o n

I n t e r p r e t a t i o n S t a t u s f l a g s t a t e f o re x e c u t i o n

0 0 0 0 E Q E q u a l / e q u a l s z e r o Z s e t0 0 0 1 N E N o t e q u a l Z c l e a r0 0 1 0 C S / H S C a r r y s e t / u n s i g n e d h i g h e r o r s a m e C s e t0 0 1 1 C C / L O C a r r y c l e a r / u n s i g n e d l o w e r C c l e a r0 1 0 0 M I M i n u s / n e g a t i v e N s e t0 1 0 1 P L P l u s / p o s i t i v e o r z e r o N c l e a r0 1 1 0 V S O v e r f l o w V s e t0 1 1 1 V C N o o v e r f l o w V c l e a r1 0 0 0 H I U n s i g n e d h i g h e r C s e t a n d Z c l e a r1 0 0 1 L S U n s i g n e d l o w e r o r s a m e C c l e a r o r Z s e t1 0 1 0 G E S i g n e d g r e a t e r t h a n o r e q u a l N e q u a l s V1 0 1 1 L T S i g n e d l e s s t h a n N i s n o t e q u a l t o V1 1 0 0 G T S i g n e d g r e a t e r t h a n Z c l e a r a n d N e q u a l s V1 1 0 1 L E S i g n e d l e s s t h a n o r e q u a l Z s e t o r N i s n o t e q u a l t o V1 1 1 0 A L A l w a y s a n y1 1 1 1 N V N e v e r ( d o n o t u s e ! ) n o n e

c o n d

3 1 2 8 2 7 0

© 2000 Addison Wesley ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

55/102

B r a n c h c o n d i t i o n sB r a n c h I n t e r p r e t a t i o n N o r m a l u s e sBB A L

U n c o n d i t i o n a lA l w a y s

A l w a y s t a k e t h i s b r a n c hA l w a y s t a k e t h i s b r a n c h

B E Q E q u a l C o m p a r i s o n e q u a l o r z e r o r e s u l tB N E N o t e q u a l C o m p a r i s o n n o t e q u a l o r n o n - z e r o r e s u l tB P L P l u s R e s u l t p o s i t i v e o r z e r oB M I M i n u s R e s u l t m i n u s o r n e g a t i v eB C CB L O

C a r r y c l e a rL o w e r

A r i t h m e t i c o p e r a t i o n d i d n o t g i v e c a r r y - o u tU n s i g n e d c o m p a r i s o n g a v e l o w e r

B C SB H S

C a r r y s e tH i g h e r o r s a m e

A r i t h m e t i c o p e r a t i o n g a v e c a r r y - o u tU n s i g n e d c o m p a r i s o n g a v e h i g h e r o r s a m e

B V C O v e r f l o w c l e a r S i g n e d i n t e g e r o p e r a t i o n ; n o o v e r f l o w o c c u r r e dB V S O v e r f l o w s e t S i g n e d i n t e g e r o p e r a t i o n ; o v e r f l o w o c c u r r e dB G T G r e a t e r t h a n S i g n e d i n t e g e r c o m p a r i s o n g a v e g r e a t e r t h a nB G E G r e a t e r o r e q u a l S i g n e d i n t e g e r c o m p a r i s o n g a v e g r e a t e r o r e q u a lB L T L e s s t h a n S i g n e d i n t e g e r c o m p a r i s o n g a v e l e s s t h a nB L E L e s s o r e q u a l S i g n e d i n t e g e r c o m p a r i s o n g a v e l e s s t h a n o r e q u a lB H I H i g h e r U n s i g n e d c o m p a r i s o n g a v e h i g h e rB L S L o w e r o r s a m e U n s i g n e d c o m p a r i s o n g a v e l o w e r o r s a m e

© 2000 Addison Wesley ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

56/102

ARM instruction

0 0 0 0

2831 27 0

condition field (EQ)

CPSR (Current Program Status Register)

Z

2831 27 0

condition flags

Se Z==1 (EQ) esegue l'istruzione, altrimenti la salta

Esempio di istruzione condizionata EQ

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

57/102

r1<==>ar2<==>b

Esempio: algoritmo massimo comune divisore

algoritmo con branch algoritmo con condizioni

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

58/102

Esempio: algoritmo di ricerca del massimo

if (a > b) c=a; else c=b; // c = max (a , b)

CMP r0, r1 ; compara r0,r1MOVGT r2, r0 ; se r0>r1, r2=r0MOVLE r2, r1 ; se r0<=r1, r2=r1

MOV r2, r0 ; r2=r0CMP r0, r1 ; compara r0, r1MOVLE r2, r1 ; se r0<=r1, r2=r1

CMP r0, r1 ; compara r0, r1BLE ELSE ; se r0<=r1 salta a ELSEMOV r2, r0 ; r2=r0B ENDIF ; salta a ENDIF

ELSE MOV r2, r1 ; r2=r1ENDIF .. ; ..

posto che: a → r0, b → r1, c → r2

più efficienti, ma utili solo per if-else brevi

meno efficiente, ma utile per if-else lunghi

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

59/102

ARM Architecture Reference Manual

Esempio: azzeramento di un vettore

for(i=0; i<10; i++){ a[i]=0 } // a[0] = ... = a[9] = 0

MOV r1, #0 ; valore da caricare in a[i]ADR r2, a[0] ; r2 punta alla locazione a[0]MOV r0, #0 ; i = 0

LOOP CMP r0, #10 ; i < 10 ?BGE EXIT ; if i>=10 EXITSTR r1, [r2,r0,LSL #2] ; a[i]=0 <--> [r2+r0*4]=r1ADD r0, r0, #1 ; i++B LOOP

EXIT .. ; ..

ADR è una pseudo-istruzione dell'assembler, che calcola automaticamente un indirizzo mediante istruzioni di tipo ADD o SUB applicate al Program Counter (PC)

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

60/102

Core Architecture ARM1 v1ARM2 v2ARM2as, ARM3 v2aARM6, ARM600, ARM610 v3ARM7, ARM700, ARM710 v3ARM7TDMI, ARM710T, ARM720T, ARM740T v4TStrongARM, ARM8, ARM810 v4ARM9TDMI, ARM920T, ARM940T v4TARM9ES v5TEARM10TDMI, ARM1020E v5TE

Architetture ARM

ARM Architecture Reference Manual

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

61/102

fetch decode execute

Esecuzione di istruzioni in tre fasi successiveSenza pipeline

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

62/102

Esecuzione di istruzioni in pipeline a tre stadiCon pipeline

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

63/102

t

instr. #1

instr. #2

instr. #3

ARM operazione della pipeline a 3 stadi con istruzione a ciclo singolo

fetch decode execute

fetch decode execute

fetch decode execute

latenza di tre cicli

il through-put è un'istruzione per ciclo

PC PC+4 PC+8

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

64/102

fetch ADD decode execute

fetch STR decode calc. addr. data xfer

fetch ADD decode execute

fetch ADD decode execute

fetch ADD decode execute

t

instr. #1

instr. #2

instr. #3

instr. #4

instr. #5

= main memory access

ARM operazione della pipeline a 3 stadi con istruzione multi ciclo

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

65/102

Differenza nel comportamento della pipeline in stato ARM e stato Thumb

Copyright © 2001 ARM Limited

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

66/102

address register

register bank31x32-bit registers+ 6 status registers

32-bit ALU

32x8 multiplier

write data register

instruction pipelineread data register

thumb instruction decoder

instructiondecoder

andcontrollogic

addressincrementer

WDATA[31:0]

ADDR[31:0]

barrel shifter

RDATA[31:0]

ALU

bus

A b

us

B b

us

address register

PC

bus

incr

emen

ter

bus

ARM7TDMI-S core

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

67/102

address register

register bank31x32-bit registers+ 6 status registers

32-bit ALU

32x8 multiplier

write data registerinstruction pipelineread data register

thumb instruction decoder

instructiondecoder

andcontrollogic

addressincrementer

WDATA[31:0]

ADDR[31:0]

barrel shifter

RDATA[31:0]

ALU

bus

A b

us

B b

us

address register

PC

bus

incr

emen

ter

bus

Data processing instruction (register

to register operation)cycle #1:

fetch instr. #1

PC = 0xXXXXXXXX

instr. #1

L'istruzione #1 viene caricata dalla memoria codice (fetch), all'indirizzo 0xXXXXXXXX; il program counter (PC), presente nel banco dei registri, è poi incrementato di 4 (ARM mode) passando al valore 0xXXXXXXXX + 4.

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

68/102

address register

register bank31x32-bit registers+ 6 status registers

32-bit ALU

32x8 multiplier

write data registerinstruction pipelineread data register

thumb instruction decoder

instructiondecoder

andcontrollogic

addressincrementer

WDATA[31:0]

ADDR[31:0]

barrel shifter

RDATA[31:0]

ALU

bus

A b

us

B b

us

address register

PC

bus

incr

emen

ter

bus

Data processing instruction (register

to register operation)cycle #2:

decode instr. #1fetch inst. #2

PC = 0xXXXXXXXX + 4

instr. #2

L'istruzione #2 viene caricata dalla memoria codice (fetch), all'indirizzo 0xXXXXXXXX + 4; il program counter (PC), presente nel banco dei registri, è poi incrementato di 4 (ARM mode) passando al valore 0xXXXXXXXX + 8. L'istruzione #1 passa al decoder per la sua interpretazione.

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

69/102

address register

register bank31x32-bit registers+ 6 status registers

32-bit ALU

32x8 multiplier

write data register

instruction pipelineread data register

thumb instruction decoder

instructiondecoder

andcontrollogic

addressincrementer

WDATA[31:0]

ADDR[31:0]

barrel shifter

RDATA[31:0]

ALU

bus

A b

us

B b

us

address register

PC

bus

incr

emen

ter

bus

Data processing instruction (register

to register operation)cycle #3:

execute instr. #1decode instr. #2

fecth instr. #3

PC = 0xXXXXXXXX + 8

instr. #3

L'istruzione #3 viene caricata dalla memoria codice (fetch), all'indirizzo 0xXXXXXXXX + 8; il program counter (PC), presente nel banco dei registri, è poi incrementato. L'istruzione #2 passa al decoder per la sua interpretazione. L'istruzione #1 va nella fase di execute, agendo solo sui registri (come in questo esempio) o anche sulla memoria esterna, nel caso d'istruzione di tipo load/store.

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

70/102

Esecuzione d'istruzione in pipeline

fetch dec reg ALU mem res1

fetch dec reg ALU mem res

fetch dec reg ALU mem res

2

3

time

instruction

Problemi delle pipeline

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

71/102

Rischio pipeline Read-after-write

fetch dec reg ALU mem res1

fetch dec reg ALU mem res2

time

stall

instruction

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

72/102

Comportamento del salto in pipeline

fetch dec reg ALU mem res1 (branch)

fetch dec reg ALU mem res

fetch dec reg ALU mem res

2

3

time

instruction

fetch dec reg ALU mem res

fetch dec reg ALU mem res

4

5 (branch target)

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

73/102

Eccezioni

esecuzioneDurante l'esecuzione normale di un programma, il micro esegue le istruzioni una dopo l'altra, mediante il processo di fetch-decode-execute.

Le eccezioni sono eventi anomali che prevedono reazioni particolari del micro per gestire la nuova situazione.

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

74/102

Eccezione

effetto diretto di un'istruzione

effetto indiretto di un'istruzione

derivante da una causa esterna

software interrupt (SWI)

undefined instruction

prefetch abort

data abort

reset

interrupt request (IRQ)

fast interrupt request (FIQ)

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

75/102

C P S R [ 4 : 0 ] M o d e U s e R e g i s t e r s1 0 0 0 0 U s e r N o r m a l u s e r c o d e u s e r1 0 0 0 1 F I Q P r o c e s s i n g f a s t i n t e r r u p t s _ f i q1 0 0 1 0 I R Q P r o c e s s i n g s t a n d a r d i n t e r r u p t s _ i r q1 0 0 1 1 S V C P r o c e s s i n g s o f t w a r e i n t e r r u p t s ( S W I s ) _ s v c1 0 1 1 1 A b o r t P r o c e s s i n g m e m o r y f a u l t s _ a b t1 1 0 1 1 U n d e f H a n d l i n g u n d e f i n e d i n s t r u c t i o n t r a p s _ u n d1 1 1 1 1 S y s t e m R u n n i n g p r i v i l e g e d o p e r a t i n g s y s t e m t a s k s u s e r

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

76/102

cpsr spsr_exc

PC LR_exc

set cpsr (mode bits)

PCexc vector address

Gestione in ingresso dell'eccezione

Gestione in uscita dell'eccezione

spsr_exc cpsr

LR_exc PC

© 2000 Addison Wesley

E x c e p t i o n M o d e V e c t o r a d d r e s s R e s e t S V C 0 x 0 0 0 0 0 0 0 0 U n d e f i n e d i n s t r u c t i o n U N D 0 x 0 0 0 0 0 0 0 4 S o f t w a r e i n t e r r u p t ( S W I ) S V C 0 x 0 0 0 0 0 0 0 8 P r e f e t c h a b o r t ( i n s t r u c t i o n f e t c h m e m o r y f a u l t ) A b o r t 0 x 0 0 0 0 0 0 0 C D a t a a b o r t ( d a t a a c c e s s m e m o r y f a u l t ) A b o r t 0 x 0 0 0 0 0 0 1 0 I R Q ( n o r m a l i n t e r r u p t ) I R Q 0 x 0 0 0 0 0 0 1 8 F I Q ( f a s t i n t e r r u p t ) F I Q 0 x 0 0 0 0 0 0 1 C

ISR

istruzione atomica di tipo:MOVS pc, r14 ; returnSUBS pc, r14, #4 ; pc=r14-4SUBS pc, r14, #8 ; pc=r14-8

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

77/102

L'eccezione SWI

N.B. : il modo SUPERVISOR è utilizzato anche al reset del processore

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

78/102

instr. #1

SWI

instr. #3

instr. #4

instr. #5

instr. #6

execute

decode

fetcht

PC

PC - 4

PC - 8

SWI

L'eccezione SWI viene attivata, con apposita istruzione, dopo la conclusione della fase di decode; il registro r14_svc (LR) viene caricato con il PC corrente, che punta all'istruzione successiva a SWI. In seguito il CPSR viene salvato in SPSR_svc. Poi il processore imposta i bit di modalità di CPSR come Supervisor (10011), disabilita gli Interrupt ed imposta il PC a 0x08, vettore di gestione dell'eccezione. Al termine della routine di gestione dell'eccezione, poiché il processore deve ritornare all'istruzione successiva a SWI, ricarica il valore di LR in PC. Infine ricarica il valore di SPSR_svc in CPSR, per tornare alla modalità precedente all'eccezione.

cond 1 1 1 1 24-bit (interpreted) immediate

31 28 27 24 23 0

r0r1r2r3r4r5r6r7r8r9

r10r11r12r13

r14 (LR)r15 (PC)

CPSR

User | Systemr0r1r2r3r4r5r6r7r8r9r10r11r12

r13_svcr14_svc (LR)

r15 (PC)

CPSR

Supervisor

SPSR_svc

(1)

(2)

0x08

(4)

F T 1 0 0 1 11

7 6 5 4 0

(3)

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

79/102

L'eccezione Undefined

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

80/102

instr. #1

undefined

instr. #3

instr. #4

instr. #5

instr. #6

execute

decode

fetcht

PC

PC - 4

PC - 8

Undefined instruction

r0r1r2r3r4r5r6r7r8r9

r10r11r12r13

r14 (LR)r15 (PC)

CPSR

User | System

(1)

(2)

0x04

(4)

F T 1 1 0 1 11

7 6 5 4 0

(3)

L'eccezione Undefined viene attivata quando il processore non riconosce un'istruzione (anche di coprocessore), dopo la conclusione della fase di decode; il registro r14_und (LR) viene caricato con il PC corrente, che punta all'istruzione successiva. In seguito il CPSR viene salvato in SPSR_und. Poi il processore imposta i bit di modalità di CPSR come Undefined (11011), disabilita gli Interrupt ed imposta il PC a 0x04, vettore di gestione dell'eccezione. Al termine della routine di gestione dell'eccezione, poiché il processore deve ritornare all'istruzione successiva a quella Undefined, ricarica il valore di LR in PC. Infine ricarica il valore di SPSR_und in CPSR, per tornare alla modalità precedente all'eccezione.

r0r1r2r3r4r5r6r7r8r9

r10r11r12

r13_undr14_und (LR)

r15 (PC)

CPSR

Undefined

SPSR_und

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

81/102

L'eccezione IRQ

N.B. : più periferiche possono essere collegate a IRQ e messe in priorità mediante il VIC 190

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

82/102

IRQ

r0r1r2r3r4r5r6r7r8r9r10r11r12r13

r14 (LR)r15 (PC)

CPSR

User | System

(1)

(2)

(4)

F T 1 0 0 1 01

7 6 5 4 0

(3)

L'eccezione IRQ viene attivata dopo la fase di execute, su richiesta di una periferica esterna; il registro r14_irq (LR) viene caricato con il PC corrente, che punta all'istruzione dopo la successiva. In seguito il CPSR viene salvato in SPSR_irq. Poi il processore imposta i bit di modalità di CPSR come IRQ (10010), disabilita gli Interrupt ed imposta il PC a 0x18, vettore di gestione dell'eccezione. Al termine della routine di gestione dell'eccezione, poiché il processore deve ritornare all'istruzione successiva, ricarica il valore di LR - 4 in PC. Infine ricarica il valore di SPSR_irq in CPSR, per tornare alla modalità precedente all'eccezione. In alternativa al vettore 0x18 si può caricare l'indirizzo 0xff0, se presente il VIC PL190.

instr. #1

instr. #2

instr. #3

instr. #4

instr. #5

instr. #6

execute

decode

fetcht

PC

PC - 8

PC - 4

r0r1r2r3r4r5r6r7r8r9

r10r11r12

r13_irqr14_irq (LR)

r15 (PC)

CPSR

IRQ

SPSR_irq

0x18(con VIC PL190 0xff0)

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

83/102

L'eccezione FIQ

N.B. : pur essendo possibile collegare più periferiche a FIQ è preferibile collegarne una sola

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

84/102

FIQ

r0r1r2r3r4r5r6r7r8r9r10r11r12r13

r14 (LR)r15 (PC)

CPSR

User | System

(1)

(2)

(4)

1 T 1 0 0 0 11

7 6 5 4 0

(3)

L'eccezione FIQ viene attivata dopo la fase di execute, su richiesta di una periferica esterna; il registro r14_fiq (LR) viene caricato con il PC corrente, che punta all'istruzione dopo la successiva. In seguito il CPSR viene salvato in SPSR_fiq. Poi il processore imposta i bit di modalità di CPSR come FIQ (10001), disabilita gli Interrupt, i Fast Interrupt ed imposta il PC a 0x1C, vettore di gestione dell'eccezione. In questo caso la routine di gestione potrebbe cominciare direttamente a questo indirizzo. Al termine della routine di gestione dell'eccezione, poiché il processore deve ritornare all'istruzione successiva, ricarica il valore di LR - 4 in PC. Infine ricarica il valore di SPSR_fiq in CPSR, per tornare alla modalità precedente all'eccezione.

instr. #1

instr. #2

instr. #3

instr. #4

instr. #5

instr. #6

execute

decode

fetcht

PC

PC - 8

PC - 4

0x1C

r0r1r2r3r4r5r6r7

r8_fiqr9_fiqr10_fiqr11_fiqr12_fiqr13_fiq

r14_fiq (LR)r15 (PC)

CPSR

FIQ

SPSR_fiq

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

85/102

L'eccezione Abort

N.B. : gestisce sia Data Abort che Prefetch Abort

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

86/102

abort

instr. #2

instr. #3

instr. #4

instr. #5

instr. #6

execute

decode

fetcht

PC

PC - 4

PC - 8

Data abort

r0r1r2r3r4r5r6r7r8r9r10r11r12r13

r14 (LR)r15 (PC)

CPSR

User | System

(1)

(2)

(4)

0 T 1 0 1 1 11

7 6 5 4 0

(3)

0x10

L'eccezione Data Abort viene attivata dopo la fase di execute, a seguito di un errore nell'accesso a un dato in memoria; il registro r14_abt (LR) viene caricato con il PC corrente, che punta all'istruzione dopo la successiva. In seguito il CPSR viene salvato in SPSR_abt. Poi il processore imposta i bit di modalità di CPSR come Abort (10111), disabilita gli Interrupt ed imposta il PC a 0x10, vettore di gestione dell'eccezione. Al termine della routine di gestione dell'eccezione, poiché il processore deve ripetere l'istruzione abortita, ricarica il valore di LR - 8 in PC. Infine ricarica il valore di SPSR_abt in CPSR, per tornare alla modalità precedente all'eccezione.

r0r1r2r3r4r5r6r7r8r9

r10r11r12

r13_abtr14_abt (LR)

r15 (PC)

CPSR

Abort

SPSR_abt

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

87/102

instr. #1

instr. #2

instr. #3

instr. #4

instr. #5

instr. #6

execute

decode

fetcht

PC

PC - 4

PC - 8

Prefetch abort

r0r1r2r3r4r5r6r7r8r9r10r11r12r13

r14 (LR)r15 (PC)

CPSR

User | System

(1)

(2)

(4)

0 T 1 0 1 1 11

7 6 5 4 0

(3)

0x0C

r0r1r2r3r4r5r6r7r8r9

r10r11r12

r13_abtr14_abt (LR)

r15 (PC)

CPSR

Abort

SPSR_abt

L'eccezione Prefetch Abort viene attivata dopo la fase di decode, a seguito di un errore durante il caricamento di un'istruzione; il registro r14_abt (LR) viene caricato con il PC corrente, che punta all'istruzione successiva. In seguito il CPSR viene salvato in SPSR_abt. Poi il processore imposta i bit di modalità di CPSR come Abort (10111), disabilita gli Interrupt ed imposta il PC a 0x0C, vettore di gestione dell'eccezione. Al termine della routine di gestione dell'eccezione, poiché il processore deve ripetere l'istruzione abortita, ricarica il valore di LR - 4 in PC. Infine ricarica il valore di SPSR_abt in CPSR, per tornare alla modalità precedente all'eccezione.

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

88/102

Vettori di eccezioni e livelli di priorità

Copyright © 2001 ARM Limited

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

89/102

Copyright © 2005 ARM Limited

5.25 Declaring Attributes of FunctionsIn GNU C, you declare certain things about functions called in your program which helpthe compiler optimize function calls and check your code more carefully.The keyword __attribute__ allows you to specify special attributes when makinga declaration. This keyword is followed by an attribute specification inside doubleparentheses.

interruptUse this attribute on the ARM, AVR, C4x, CRX, M32C, M32R/D, MS1, andXstormy16 ports to indicate that the specified function is an interrupt handler.The compiler will generate function entry and exit sequences suitable for use inan interrupt handler when this attribute is present.

Note, for the ARM, you can specify the kind of interrupt to be handled byadding an optional parameter to the interrupt attribute like this:void f () __attribute__ ((interrupt ("IRQ")));Permissible values for this parameter are: IRQ, FIQ, SWI, ABORT and UNDEF

Tratto da Using the GNU Compiler Collection for gcc version 4.2.2 di Richard M. Stallman and the GCC Developer Community

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

90/102

0X0000001C LDR PC, FIQ_Addr

Eccezione sollevata da una periferica di tipo FIQ

FIQ

{

(...)

0X00000000 LDR PC, Reset_Addr0X00000004 LDR PC, Undef_Addr0X00000008 LDR PC, SWI_Addr0X0000000C LDR PC, Pabort_Addr0X00000010 LDR PC, Dabort_Addr0X00000014NOP0X00000018 LDR PC, [PC,#-0xFF0]

void handlerFIQ(void)

}

(...)

(...)a++;c = a / 2;

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

91/102

0X0000001C LDR PC, FIQ_Addr

Eccezione sollevata da una periferica di tipo IRQ non vettorizzata

IRQ

{

(...)

0X00000000 LDR PC, Reset_Addr0X00000004 LDR PC, Undef_Addr0X00000008 LDR PC, SWI_Addr0X0000000C LDR PC, Pabort_Addr0X00000010 LDR PC, Dabort_Addr0X00000014NOP0X00000018 LDR PC, [PC,#-0xFF0]

void handlerIRQ(void)

}

(...)

(...)a++;c = a / 2;

VICDefVectAddr

VICVectAddr

VIC PL 190

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

92/102

0X0000001C LDR PC, FIQ_Addr

Eccezione sollevata da una periferica di tipo IRQ vettorizzata

IRQ#3

{

(...)

0X00000000 LDR PC, Reset_Addr0X00000004 LDR PC, Undef_Addr0X00000008 LDR PC, SWI_Addr0X0000000C LDR PC, Pabort_Addr0X00000010 LDR PC, Dabort_Addr0X00000014NOP0X00000018 LDR PC, [PC,#-0xFF0]

void handlerIRQ#3(void)

}

(...)

(...)a++;c = a / 2;

VICVectAddr

VIC PL 190

VICVectAddr1

VICVectAddr2VICVectAddr3

VICVectAddr4

VICVectAddr5

VICVectAddr6VICVectAddr7VICVectAddr8VICVectAddr9VICVectAddr10VICVectAddr11VICVectAddr12VICVectAddr13VICVectAddr14

VICVectAddr0

VICVectAddr14

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

93/102

0X0000001C LDR PC, FIQ_Addr

Eccezione sollevata da una periferica di tipo IRQ senza l'uso del VIC PL190

IRQ

{

(...)

0X00000000 LDR PC, Reset_Addr0X00000004 LDR PC, Undef_Addr0X00000008 LDR PC, SWI_Addr0X0000000C LDR PC, Pabort_Addr0X00000010 LDR PC, Dabort_Addr0X00000014NOP0X00000018 LDR PC, IRQ_Addr

void handlerIRQ(void)

}

(...)

(...)a++;c = a / 2;

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

94/102

L i t t l e - a n d b i g - e n d i a n m e m o r y o r g a n i z a t i o n s

h a l f - w o r d 4

w o r d 1 6

0123

4567

891 01 1

b y t e 0

b y t e

1 21 31 41 5

1 61 71 81 9

2 02 12 22 3

b y t e 1b y t e 2

h a l f - w o r d 1 4

b y t e 3

b y t e 6 h a l f - w o r d 6

w o r d 1 6

3210

7654

1 11 098

b y t e 3

b y t e

1 51 41 31 2

1 91 81 71 6

2 32 22 12 0

b y t e 2b y t e 1

h a l f - w o r d 1 2

b y t e 0

b y t e 5 a d d r e s sa d d r e s s

( a ) L i t t l e - e n d i a n m e m o r y ( b ) B i g - e n d i a n m e m o r yo r g a n i z a t i o no r g a n i z a t i o n

b i t 3 1 b i t 0 b i t 3 1 b i t 0

h a l f - w o r d 1 2 h a l f - w o r d 1 4

w o r d 8 w o r d 8

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

95/102

T h e s t a n d a r d A R M C p r o g r a m a d d r e s s s p a c e m o d e l

c o d e

s t a t i c d a t a

h e a p

s t a c k

u n u s e d

a p p l i c a t i o n l o a d a d d r e s s

t o p o f a p p l i c a t i o n

t o p o f h e a p

t o p o f m e m o r y

s t a c k p o i n t e r ( s p )

s t a c k l i m i t ( s l )

s t a c k l o w - w a t e r m a r k

a p p l i c a t i o n ’ s i m a g e

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

96/102

t1

t2

t3

t4

t5

t6

t7

stacksize

time

Comportamento dello stackmain(){

.. /* t1 */func1();.. /* t5 */func2();.. /* t7 */

} /* end of main */

func1(){

.. /* t2 */func2();.. /* t4 */

} /* end of func1 */

func2(){

.. /* t3, t6 */

} /* end of func2 */© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

97/102

A typical AMBA-based system

externalbus

interface

ARMcore/CPU

on-chipRAM

bridge

APB

AHB or ASB

test i/f ctrl

DMAcontroller

parallel i/f

timer

UART

AMBA: Advanced Microcontroller Bus Architecture

ASB: Advanced System Bus

AHB: Advanced High-performance Bus

APB: Advanced Peripheral Bus

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

98/102

Tipico sistema di debug

Copyright © 2001 ARM Limited

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

99/102

core

logic

TAPcontroller

device ID reg

bypass reg

instruction reg

in

out

I/O

enable

in enable

TDI

TMS

TCK

TRST

TDO

Organizzazione JTAG boundary scan

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

100/102

JTAG TAPcontroller

Embedded

processorcore

TCK TMSTRST TDI TDO

D[31:0]

A[31:0]

opc, r/w,mreq, trans,mas[1:0]

othersignals

scan chain 0

scan chain 2

scan chain 1

extern0extern1 ICE

bussplitter

Din[31:0]

Dout[31:0]

Organizzazione ARM7TDMI

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

101/102

Process 0.35 um Transistors 74,209 MIPS 60 Metal layers 3 Core area 2.1 mm

2 Power 87 mW

Vdd 3.3 V Clock 0 to 66 MHz MIPS/W 690

Caratteristiche ARM7TDMI

Process 0.25 um Transistors 110,000 MIPS 220 Metal layers 3 Core area 2.1 mm

2 Power 150 mW

Vdd 2.5 V Clock 0 to 200 MHz MIPS/W 1500

Caratteristiche ARM9TDMI

© 2000 Addison Wesley

Architettura ARM Microprocessori e MicrocontrolloriCorso di progettazione su SoC ARM

S2DEL – Solid State and Diamond Electronics Lab. ROMATRE

Università degli Studi

102/102

ARM7TDMI and ARM9TDMI pipeline

comparisonsinstruction

fetch

instructionfetch

Thumbdecompress

ARMdecode

regread

regwriteshift/ALU

regwriteshift/ALU

r. read

decode

data memoryaccess

Fetch Decode Execute

Memory WriteFetch Decode Execute

ARM9TDMI:

ARM7TDMI:

© 2000 Addison Wesley